#### Unit -I

### Power Semiconductor Devices

Study of Switching Devices:

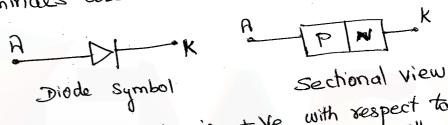

Diode :

I characteristics of Diode:

\* Power diode is a two terminal projunction destice

- \* Pn junction is normally formed by Alloying diffusing and epitaxial growth

- \* Two terminals are anode (A) and Cathode (K).

\* When anode potential is + ve with respect to Cathode, diode is forward biased and it will

- \* When Cathode potential is +ve with respect to anode, diode is revelse biased.

- In Reverse biased Condition and a small rever revelse arrent flows known as leakage

increases slowly in

magnitude with reverse voltage until breakdown \* This leakage Current or avalanche voltage diode is hired off in

\* In most Practical case diode acts as a switch

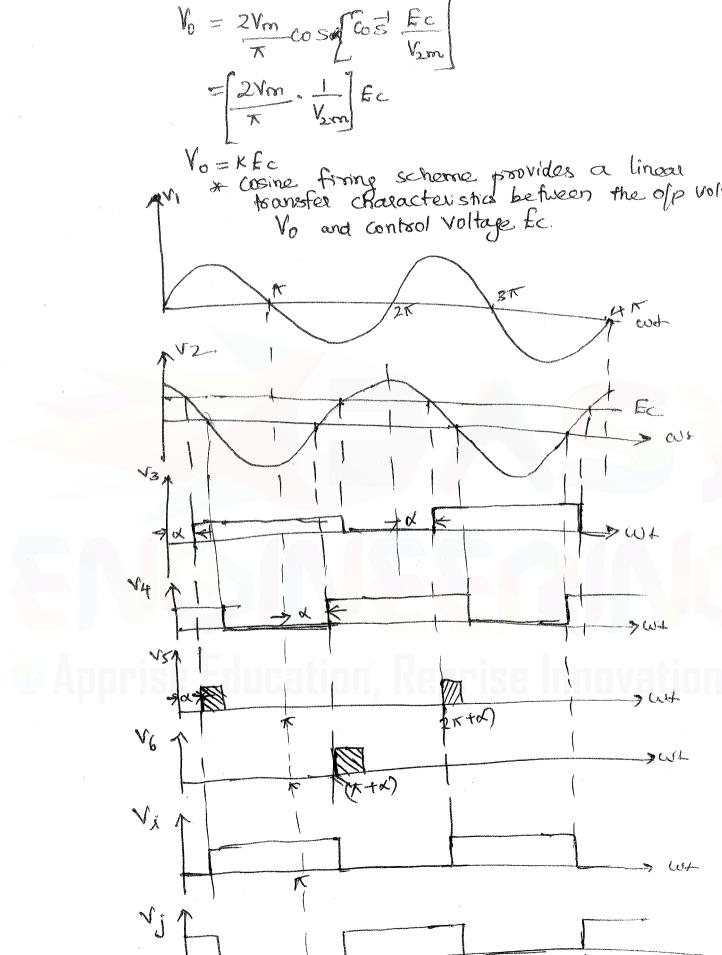

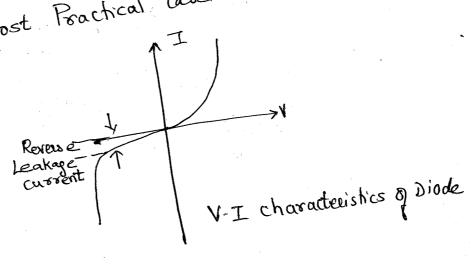

The diode Current equation (schottky diode) is given by  $J_0 = J_s \left( e^{\frac{VD}{VT}} - i \right)$ Ib- corrent through diode A Is - leakage Current or wort mA 1 - empirical Constant known as emission Coefficient or ideality factor whose Value Vasies from 1 to 2 VT - Thermal voltage V VD-Diode Voltage V VT = KT K- Boltzmann's Constant T- Absolute temperature q - electron Charge Revelse Recovery characteristics: \* The assent in a forward biased junction diode is due to the net effect of majority and minority \* Once the diode is in forward bidsed, the Carriers. forward arrent reduces to Ze 50. \* When Forward aurent reduces the diode Continues to Conduct in the reverse direction due to the minority Carriers which are stored in pn junction.

\* The diode continues to conduct due to minority The minority Carriers require a certain time to recombine with opposite charges and to be to recombine with opposite charges and to be neutralized. This time is known as reverse reutralized. The Reverse secovery characteristics of the diode is shown. is shown.

Substitute IRR m eq (1) 2 Q RR = tadi Losta = 2 QRR dift If the is negligible compared to ta, and trac 2 tor.  $\frac{2}{68} = 2 \frac{2 RR}{di/dt}$   $\frac{2 RR}{di/dt}$ Sub too in eq. IRR= V2 QRR di Revelse recovery time and peak revelse recovery current IRR depend on the storage charge ORR and severse rate of charge of current diffet. General purpose Diodes 2. Fast recovery diode, schottky diodes. Types of power Diodes: \* It has high reverse recovery time, typically 25 us, used in low speed applications. 1. General Purpose Diodes: Guent ratings vary from 1 A to Several thousand of amperes and Voltage Varies from 50V to 5KV. fast Recovery Diodes: \* It has low recovery time, normally less than 5 µs. \* Most usely in de-de and de-ac convertes ascuts,

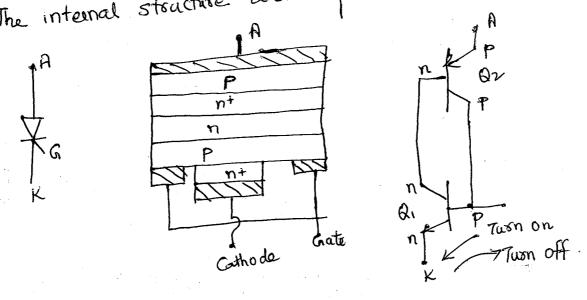

\* Current ratings from less than IA to hundred of \* Voltage Valy from 500 to 3KV. \* For voltages below 400V, epitaxial diodes provide Faster switching speeds. Than diffused diode. \* For voltages above 4000, diffused diodes are preferred. for faster switching speed. \* Bassies potential exists between metal 3. Schottky Diode: and a semiconductor to climinate the charge stage problem in schotty Diode \* A layer of metal is deposited on a thin epitaxial layer of n type silicon-A This potential parried simulates the behaviour of \* forward voltage doop of senotty schottky diode is low and leakage current is very highp-n junction. \* Reverse voltage ratings are limited to 100V, and forward whent ratings vary from IA to 300 A. ·Used in High frequency instrumentation and switching power supplies. Thyristors (SCR) It is a four layer semiconductor device with three projunctions. Three Levimals, ande, cathode and gate.

A. Anode of pripri structure

pripring structure Leurimals, ande, cathode and go

\* Three A. Anode

\* Gate P J3

\* Cathode

\* When anode is made the with respect to athode, J1 and J3 Junctions are forward

biased (FB)

Ja is reverse biased (Rejoind only a small leakage Custent flows from anode to cathode.

\* The thyristre is in forward blocking or off State and leakage awant is known as off-

State awent ID. \* When Vak 1, the R.B junction J2 breaks which

is known as avalanche breakdown and the Voltage is called Forward breakover voltage. ABO.

\* Latching awant is the minimum anode current required to maintain the thyristor in on state immediately after a thyristor I has been turned on and the gate Signal has been removed.

Holding assert is the minimum anode assert to maintain the thysistor in on-state which is less than Latching awtent.

Forward Volt-drop (Conducting) Latching Current of hate triggered for IL Holding Coverent & IH forward leakage Reverse Reverse breakdown Leakage Cussent Current vo Hage

Y When cathode to made positive with respect to anode, J2 18 F1B and J, 2 J3 are R:B!

\* The thyristor is in reverse blocking state and a reverse leakage Current Known as reverse Current IR flows through the device.

when ser is in forward blocking mode a gate pulse or anode cathode voltage is increased beyond breakover voltage to make the SCR to two on which is called forward conduction mode where the device acts like a closed switch.

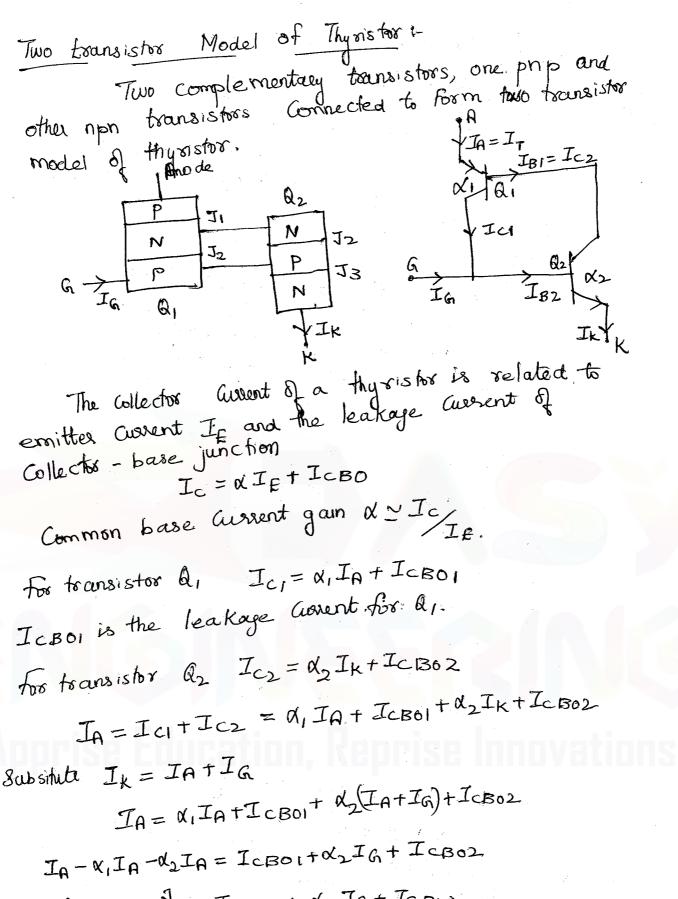

$IA\left(1-\left(\alpha_{1}+\alpha_{2}\right)=ICBOI+\alpha_{2}IG+ICBO2\right)$   $IA=\frac{\alpha_{2}IG+ICBOI+ICBO2}{1-\left(\alpha_{1}+\alpha_{2}\right)}$

\* The wwent gain of and N2 Varies with In and Ik.

\*If oxpar(N,+N2) approaches unity, denominator approaches

Zero resulting in large anode current. and

Thyristor buths on with a small gate aucent.

Thysister twon on methods: (a) Forward Voltage triggering:

or When VAK (anode Cathode vo Hage) is increased with gate circuit open, the reverse biased junction J2 will have an avalanche breakdown at a voltage called forward breakover Voltage VBO.

\* The thyrostor changes from off state to ON state characterised by a low voltage across it with large forward current.

\* Forward Voltage deop during ON state is of the order of 1 to 1.5V.

(b) Thermal Triggering (Temperature triggering).

\* When the Voltage applied between the anode and cathode is very near to its breakdown voltage, the device can be triggered by increasing its junction

& By increasing the temperature, R.B junction temperature: Collapses making the device conduct. This method of triggering is known as the thermal briggering process.

(c) Radiation triggering (Light Friggering). \* With the held of external energy, electoon hole pairs are generated in the Idevice, thus increasing the number of charge Carriers. \* This leads to instantaneous flow of awart within the device and the toggering of the device. \* Light activated Silicon Controlled rectifier (LASCIE) and light activated silicon controlled switch (LASCS) are exemples of this type of toiggeling.

a) dev/dt toiggering:

be comes reverse biased.

\* Reverse biased junction  $J_2$  has the characteristics of apacitor due to charges existing across the junction.

when froward voltage is suddenly applied, Charging award will flow tending to then the device ON.

$i_{c} = \frac{dQ}{dt} = \frac{d}{dt} (GV) = Cj \frac{dV}{dt} + V \frac{dCj}{dt}$

rate of junction capacitance is nagligible as compared to junction capacitance.

ic = c, dv

The rate of change of voltage across the device is large, the device may turn on even though the voltage appearing across the device is small.

(e) Gate Toiggering?

Most commonly used method, by applying a positive signal at the gate terminal of the device, which will triggered before the specified breakover voltage

Varying the gate signal within the Varying the gate signal within the Specified Values of maximum and Minium gate accounts.

\* Signal is applied between gate and Cathode of the device. It is of three Cathode of the device. It is of three fypes. They are dc signals, pulse signals of ac signals.

applied between the gate and cathode of the device.

with gate positive with respect to althode.

Draw backs:

\* Both power and control Circuits are not isolated from dc.

\* . Continuous gate signals produces more losses.

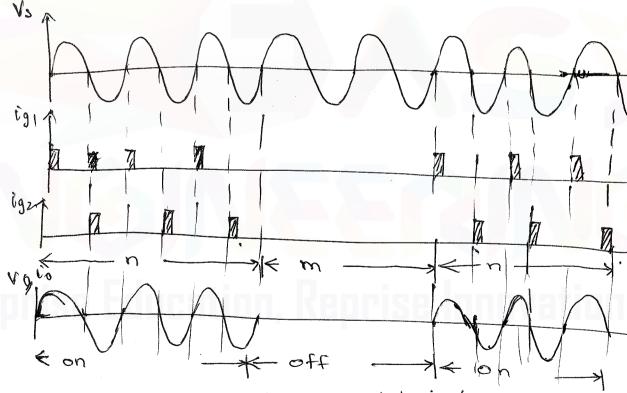

B) Ac gate triggering.

Ac source is used for gate signal. This

scheme provides the proper isolation between the

power and the Control Circuits.

rate drive is maintained during positive half ayde where the device is turned on

\* During negative half cycle severe voltage is applied where the device is fund off.

Drawback: 1. Separate transforma is required to step down the ac supply.

Pulse gate triggering:

The pulse appears periodically or sequence

This is known

as Carrier frequency gating.

Advantage

\* No need of applying Continuous signals and hence gate losses are very much reduced.

\* flectoical isolation is provided between the main device supply and its gating signals.

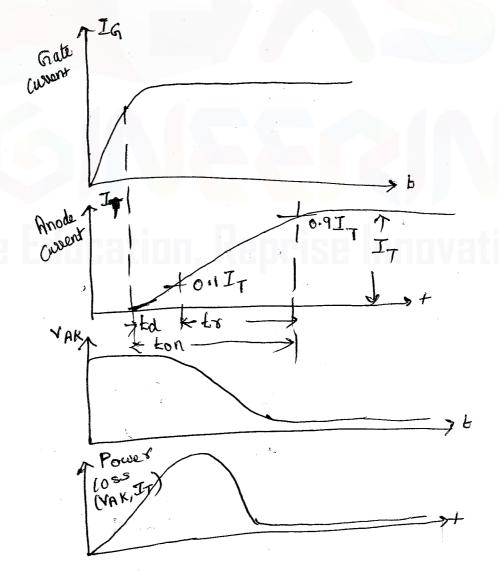

Dynamic turn on switching characteristics

The transistron From one conduction State to mon Conduction State does not take place for mon Conduction State does not take place sine instantaneously, and it occupies a finite period of time.

\* The total tuen on time ton of the SCR is Subdivided into two distinct periods, called delay time and rise time.

Delay time td:

\* The time between the instant at which gate current reaches 90% of final value and the anode current reaches 10% of final.

Rise time to

The time required for anode aurent to rise from 10 to 90% of its final value.

Turn on time tons

which of 1 to 4 us. In

\* Width of Riving pulse Should be more than 10 µs.

\* Amplitude of gate pulse Should be 3 to 5 times the minimum gate current required to trigger the SCR.

During vise time SCR Carries large Current and appreciable forward Voltage.

Is inserted in anode Circuit.

The Power Curve shows the switching losse of the device which may be significant in high trequency applications.

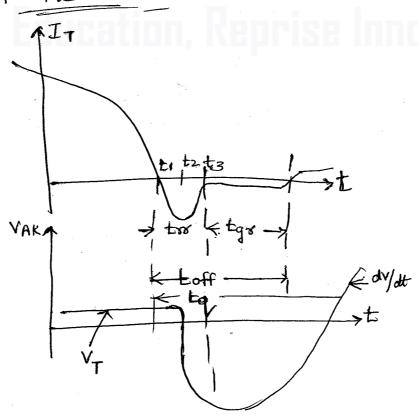

Two off Mechanism

\* The SCR Can be twomed off by reducing the Forward arrent to a level below that of the holding Current.

Process of him off is called Commutation.

\* After reducing the anode Current to Zero, of a forward voltage is applied immediately it will not block the forward voltage the device starts to conduct again unless the device is reverse biased for a finite period before a forward anode Voltage can be reapplied.

The minimum interval at which the Two off Lime: anode current becomes Zero and the instant at which the device is capable of blocking the forward. voltage: The tuen of time is divided into three two intervals, revelse We covery time and gate recovery fime.

At to, anode forward aurent becomes Zen

\* During the reverse recovery time tor, anade Cullent flows in the reverse direction.

» At t2, a reverse anode voltage is developed, and reverse recovery burrent confinues to

\* At to, I and I3 block reverse voltage, but forward voltage, cannot be blocked due to called teapped charges at the junction Carriers

At the interval to to the these carriers recombine.

Complete and \* At the recombination is applied at this forward voltage can be is the interval instant. SCR tuen of time between by and ti.

#### Commutation of sck

The percess of thering turning off a thyristor is Called Commutation. Many techniques to Commutate a thyristor. These can be classified as 1. Line Commutation (00) Natural Commutation

2. forced commutation.

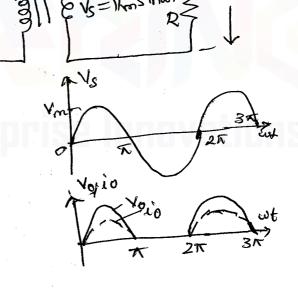

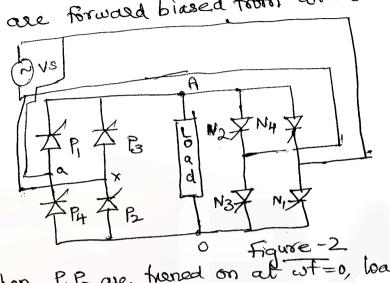

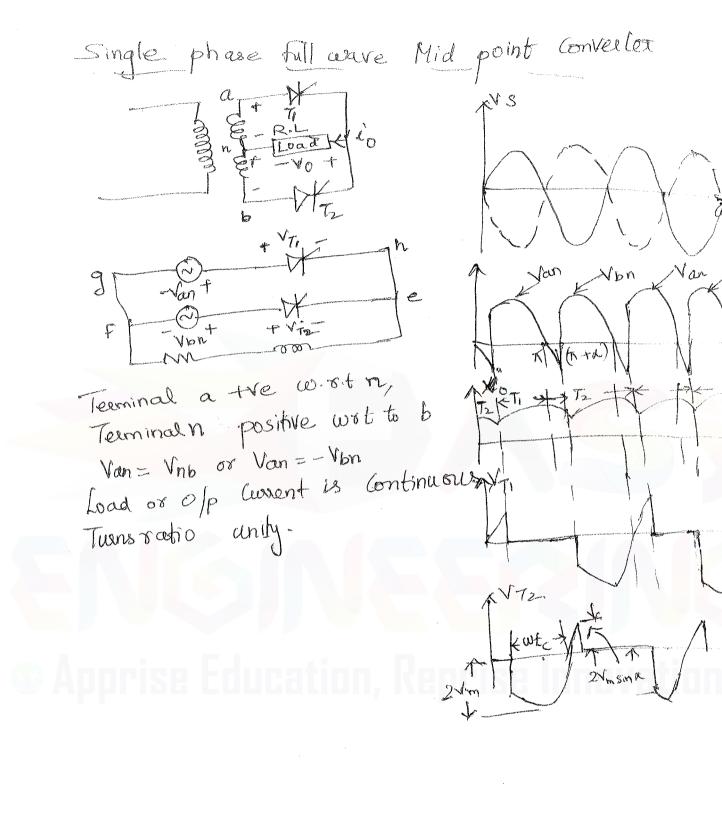

### Natural Commutation:

The thysistor is automatically two ned of during the negative half gile of input voltage of the Source voltage is ac. This Commundation is known as Natural or line Commutation. This method of Commutation is applied to phase controlled Sectifiers, ac Voltage Controller, line commutated inverters and step down

cyclo converters.

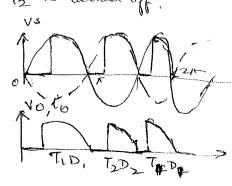

When Ti is fixed at wt=0 duling posistive Half cycle

$V_0 = V_S$ .

At wt = 1, Vs = 0, Vo=0,

When Ties formed off. during negative half ayere.

torced Commutation-

In case of de circuits for switching off the thyoistors, the forward current of the thyristor is forced to zero by an additional Circuity called Commutation Circuit. The Commutation is called forced Commutation.

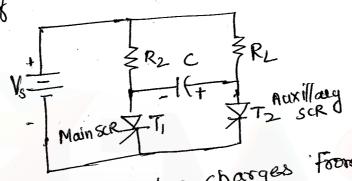

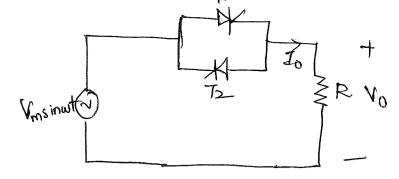

### Capacitor Commutation:

In Dr ascuits, the SCR can be horned of by switching the anote awant to an alternate path for sufficient time to allow the SCR to receive its blocking capability.

y When SCR is on, transistor is An off state, To hun, of scr, a positive pulse is applied to base of transistor a turing it on.

\* When T, Conducts, Capacitos charges from the

Source voltage through RL.

\* To then of T, auxillary thyristor To is tworld on.

\*. Reverse voltage is applied to the thyristor Ti to turn off.

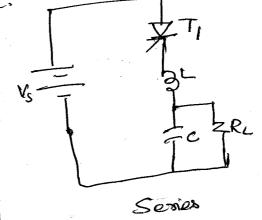

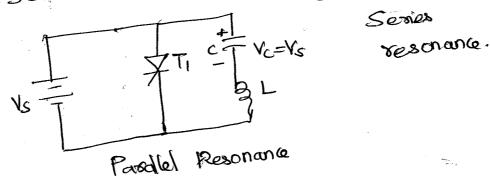

Commutation by Resonance:

\* LC Circuit Forms a resonance.

The undamp underdamped LC resonating Circuit in Series with the load applies a severse voltage to scr to tuen off.

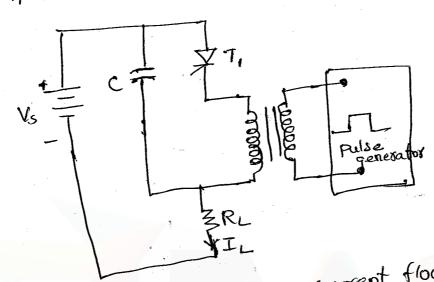

## Commutation by exteenal source:

4

\* The exteenal Source is in the form of pulse.

\* The pulse generator reverse biases the sce Ti and thus turns it off.

\*When SCR Ti is triggered the current flows through

Ti and se condary of pulse transformer and load.

To then off SCR Ti, a positive pulse from the

pulse transformer is applied to the cathode of

pulse transformer is applied to the

\* The Capacitor is charged for only IV. and Can.

Be assumed short around during the period of

Commutation.

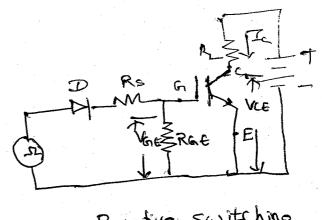

Snubber Circuit of SCR;

\* To protect the thyristor from large (di/db)

\* To protect the thyristor from large (di/db)

during turn on and large dy/dt during turn off.

a snubber circuit is essential

4 & RI

4 DI

1 - C2

T. T. T. T.

\* Inductor L. profects To from large dijut during then on process

of The Circuits by R, and D. allows the discharging of Li when the thyristor is two ned off.

\* The snubber circuit is made by R2 G2

The auxillary Circuit made by Dz and Rz allows the discharging of cz when the thyristor is turned on.

The Circuit of to and L, limits the value of diffet across the thyristor during forwards blocking.

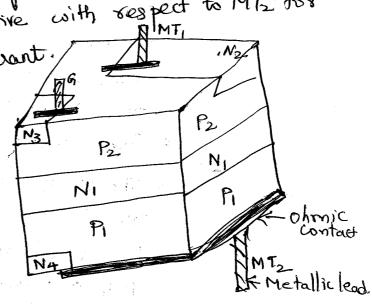

# BIDIRECTIONAL TRIODE THYRISTOR (TRIAC)

\* Two thyristors connected in antiparallel which are integrated in single structure is called as TRIAC (Triode ac switch)

\* Three terminals MT, MT and gate G.

\* TRIAC Can conduct in both direction

\* MI is positive with respect to MI, for first quadrant

\* MT, positive with respect to MT2 for third quadrant.

MT2

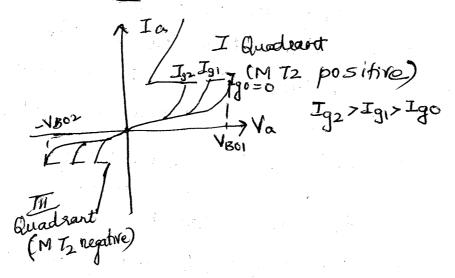

Foiggeing Modes of Triaci

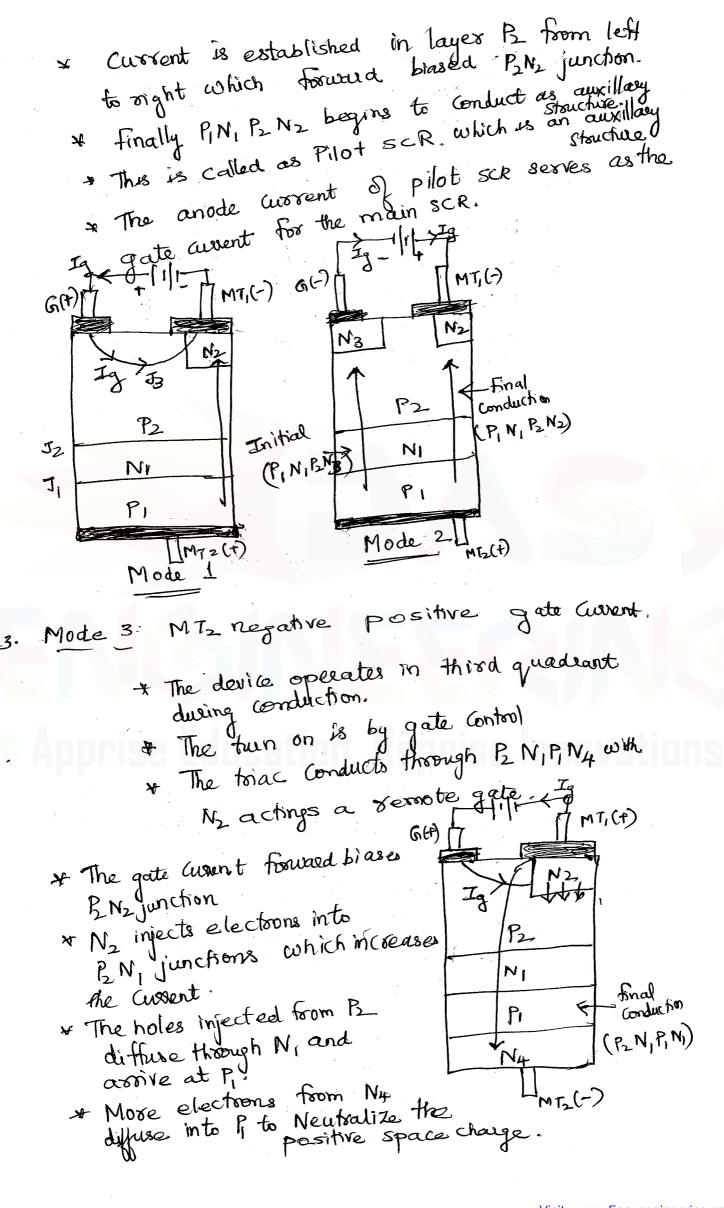

1. MTz positive, positive gate current (Mode 1)

- \* Grate awent its positive with respect to MT,.

Grate awent flows from gate lead to the ferminal MT, through P2N2 junction like an

- When gots Sufficient Charge is injected into P2 layer, reverse biased junction N,P2 Greats down.

- \* Triac starts Conducting through P.N. P. N. Layers. \* Triac speates in 1st quadrant.

# 2. M5 positive, gate ament negative (Mode 2)

- \* Grate Current flows through P2N3 junction ound reverse biased junction N, P2 is forward biased as a mormal thyristor

- \* Frac conducts through P,N,P2 N3 layers.

- + The Voltage drop falls but P2N3 mises towards the anode potential of ME.

- \* P2 is claraped to the Cathode potential of MT, a potential gradient exists across MT, a potential gradient exists across layer P2, the left hand being higher than right hand region.

\* The totac is thered on by sernote gate N2, where the device is less sensitive in third quadrant with positives gate Current

4. Mode 4 (MTz negative, megative autent)

\* N3 acts as remote gate

N3 \* Gate current forward biases 1 P2 N3 junction and electrons are injected into P2 N1 junction causing an increase of Gurrent Pini.

\* P2 N1P1 N4 tues on by sepenciative action. booking.

sensitive is more in 1st quadrant when the gate covert. and also in Titied quadrant with negative gate current.

\* Sensitive in less in 1st quadrant when -ve \* Illy in third quadeant with positive gate assent.

\* Triac can be triggered with positive or Advantages of Triaci

Neet a single heat sink of larger size whereas antiparallel SCR needs of wo heat sinks

\* Needs single fuse for protection SCRis Connected in parallel to a diode to protect against reverse voltage

Disadvantage?

Foigger Circuit neads a Careful consideration since Low duft rating

Office Conducts in both direction

Triacs are available small in rating.

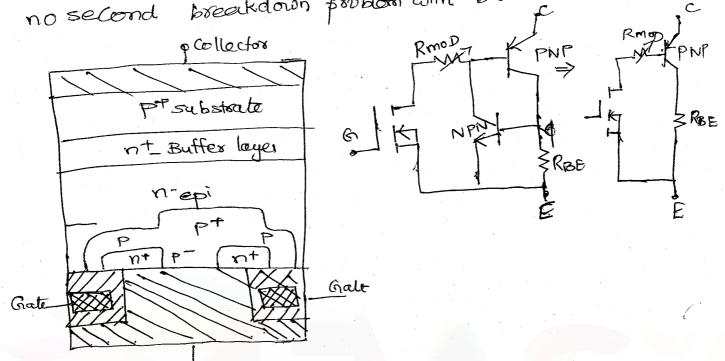

It has high input impedance of the MOSFET. and low on state Conduction losses like BJTs. There is no second breakdown problem with BITs.

pt Substade Essitted responsible for minority Cassier injection into n-region. An IGBT is made of Four alternate PNPN Layers. The nt buffer layer and wide epi base reduce the gain of NPN teeminal, thereby awaiding Latching. IGBT have two structures:

1. Punch through (PT)

In PT structure, switching time is reduced by use of heavily doped n-buffer layer in the drift region rear the collector. In the NPT Structure, Carrier life fine is Kept more than that of a PT structure, which causes conductivity modulation of the drift region and reduces the on-state voltage deop. An IGBT is voltage Controlled device, similar to power MOSFET. when the gate is made positive with respect to emitter for twon-on the n-caviers are drawn into the p-channel for twon-on the results in a forward bias of the near the gate region, this results in a forward bias of the base of the non transistor, which thereby tuens on An IGBT is trained on by just applying a positive gate voltage to open the Channel for n-takiers and a truned off by just applying a positive gete voltage to topen the channel fix

and is the truned off by removing the gate voltage to close the channel. It requires a very simple driver Circuit. It has lower switching and Conducting losses. The terminals of IGBT as gate, death and source.

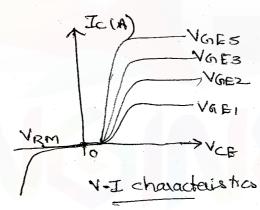

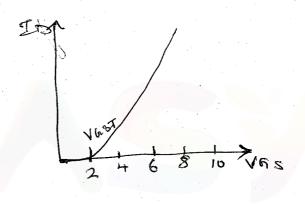

Switching Static V-I characteristics of IGBT;

The plot of collector Current Ic Versus Collectoremittee voltage VCE for Vacious values of gate-emittee voltages. The controlling parameter is gate emitter. Voltage because IGBT is a voltage controlled device. The townsfer Characteristics is a plot of collectors current Ic versus gate-emitters Voltage VGE. When VGE 18 less than the threshold voltage VGET. IGBT is in the Off state. When the device is off, junction Is blocks Forward Voltage and in case severse voltage appears across vollector and emitter, junction I, blocks it.

Ic (A). VGET Transfer Characteristics

Switching characteristics:

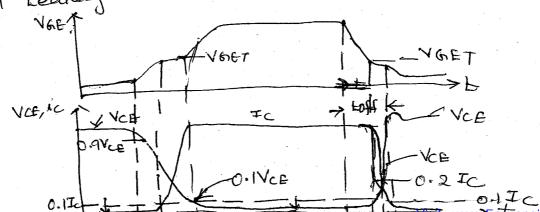

The buen-on time is defined as the time between the instants of forward blocking to forward on State. Tuen on time is Composed of delay time that and use time to. (ie) ton = ton+tr. Delay time is defined as the time for Collector emitter voltage to fall from VCE to 0.9 VCE - VCE & the initial collectors emittee Voltage. Time ton may also be defined as the time for the collector warent to rise from its iditial Leakage awaent ICE to 0-1 Ic.

Rise time to is the time ducing which the collector-emitta Voltage Falls from 0.9 VCE to 0. NCE. It is defined as the time for the collector Current to rise from 0.1 Ic to its final value Ic. After time ton, Collector aurent Ic and the Collector emitter voltage falls to small value called Conduction doop = VCES where subscript S denotes saturated value.

Two off time is of those intervals (i) delay time taf, (ii) initial fall time to (iii) final fall time top. (ie) toff = tof + tof1 + tof2 -

Delay time is the time during which gate voltage falls from Vat to the shold voltage Vast. As Vat falls to Vat during the Vat to the shold voltage Vast. As Vat falls to Vat during the Collector Current Falls from Ic to 0.9Ic. At the end of the Collector - emitter voltage begins to Dise. The first fall time to is defined as the time during which collectors current falls from 90 to 20% of its infal value Ic, or the time duing which collections-emitter Voltage rises from VCES to

final fall time top is the time during which collection O.I VEE 20 to 10% of Ic or the bires during which Voltage sises from 0.1 VCE to find value VCE. Current falls from Gollecter-emitter

Conduction and Switching Losses:

Power Losses in the IGBTs will Gons ist of (1) Drive Losses (ii) Conduction Losses (iii) Off state Losses, (iv) switching Losses.

Switching losses can be determined as a hinction of time, current and voltage has purely inductive Loads, tuen-on Losses are very small, because the transistor been on at essentially two current each Cycle, for a purely inductive load, switching Losses will be determined by the tren of losses.

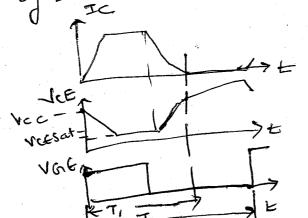

Resistive switching

Rise time (To) = 0-t1 Two off delay (Td) = t3-t2 Fall - time 1200 ( 1/2) = 15-14 Maximum Collector aurent = Icon Conduction Time (T)= E2- L) fall time one (Ti)= +4-+3 Period (7) = 1/f.

Collector to emitter Saturation Vola= VCE (set) Gate to emittee volts = VGE Collector to comittee power Supply voltage = Vac

when gate voltage is applied to an IGIST operating in a saturated switching modes the Collector to emitter voltage decreases and goes into hard saturation if sufficient gate voltage is available. The switching losses are contained in intervals 0 to t, and t3-t4. The switching power losses are directly proportional to frequency and are independent of duty cycle or pulse width. Conduct on losses are proportional to duty ande D, while off-state losses are proportional to 1-deely agre.

hate Drive arcuitsi It has gate to emitter threshold voltage

and a capacitive i/p impedance . In order to two the device on, the input capacitance must be charged up to a value greater than VG+(+h) before collector current can begin to flow. The collector to conittee - Sabuation Voltage decrease with an increase in magnitude of Vat. Lowest value of on state Voltage, VG6 should be much greater than VGE(H). To hun off the IGBT a resistor between gate and emitter is all that is required. This resistor provides a path for the gate to excitte input capacitance to discharge.

IGBT has a maximum convious and accept content that is dependent on the gate to emittex dulat. That is, higher the gate to emittee tuen - off av/dt, the lower the Controllable Collector current. The controllable current will dependent on the nature of the load.

Snubbers:

The ability to control the true on and true off times by Controlling the gate current through oppopulate Sizing of the series gate resistance further minimizes the need for then-on and then off snubbers. The snubber is used for bod line shaping and functions to reduce switching Cosses within the IGBT. The snubber also reduces from of du/dt to collector to conitte voltage. The controllable Current Capability 13 also increased since it values proportional to VCE. At low values of collector to conitte voltage, controllable collector Current is much greater than the Specified maximum value. The switching losses in the IGBT increases.

significantly due to the presence of TE2. By use of Snubbers, device heating is minimized. The operation at point P with no snubber, For, If, and If, the IGBT has Par (sw) = Vcc. Icm. f Tou +1017fi+0.17f2 switching losses equal to

When polarised mubber is used the losses are reduced. Snubbeing definitely reduces the peak power and the IGBT average power that the IGBT

rous + dissipate

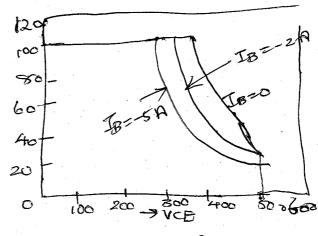

Bipolas Junction Fransistors: It is a three layer, two junction upn or pup semiconducion device. With one p-region scholwiched by by two n-region npn. transistor is obtained The term bipolar denotes that the Current flow in the device is due to the movement of both holesand elections. With two p-region Sandwiching one n-region prop transistors is obtained. But has there teeminals collectors, emitter and base. IB NPN IB POP Out Common exeitles assungement is more Common in Switching applications. So npril toansistor is used. Steady state characteristics Input characteristics A graph blu base current Is and base consitter voltage VBE gives input characteristics when collector emitter voltage VCE is more than VCEI, base airrent decreases. IBM Output characteristics Graph between Collector Correct Ic and Collector expitter voltage VCE gives output characteristics of atransistor. For base assent to be Zero Ib=0, VCE is increased, a Small leakage current flows. As the IBT, ICT. The graph shows IB=0 and IB +0. VCES Load line Break over voltage

Saturation Point I Break over Voltage

Saturation Point I Break over Voltage

The low voltage Vet is called saturation region. In this region transistor acts like a switch. The curve 2 indicates by increasing Vet and almost Constant Ic is the active region. In this region transistor acts like an amplifier. The This region transistor acts like an amplifier. The Vertical rising alive is the breakdown region.

The collector Current Ic is given by

Ic = Vcc - VcE

A bad Inc. AB is the Cocus of all possible operating points. When Foursistor is on, VCE is Zeto and Ict Vc/Rel. shown by point Air is off, Vcc appears across collector when Fransistor is off, Vcc appears across collector conittee terminals and there is no collector Current. Shown by point B.

Relation between x and B:

X = Ic is called forward Currentgain. IEAlso Ic < IE × being from 0.95 to 0.99.

Base augent is effectively the input augent and Collector augent is the output augent. The satio of collector augent Is the output I known as the Current gain.

$\beta = I_{\mathcal{B}} = h_{\mathcal{F}_{\mathcal{C}}}.$   $I_{\mathcal{B}}$

Using KCL, IE=Ic+IB.

IE>all the three current.

$$\frac{T_{E}}{I_{C}} = 1 + \frac{I_{B}}{I_{C}}$$

$$\frac{1}{X} = 1 + \frac{1}{\beta} \Rightarrow \beta = \frac{X}{1 - X}$$

$$\frac{1}{X} = \frac{\beta}{\beta + 1}$$

locansistor switch-

Transistor Operatos either in saturation region or cutt off region. For Ideal switch, point A is in Saturated state as cotto closed switch with VCE=0, point B in Cut off State with open Switch Ic=0. Large base current will cause to ansistor to work in Saturation region at point A' with VCEs small Voltage. VCES is the on-State voltage deop of order IV. when Ib=0, transistor is transed off, so execution Shift to B', in cut off region.

Apply KVL VB-RBIB = -VBE = 0 IB = VB - VBE RB Vcc = VcE + IcRc VeF = Vec - IcRc = Vec - BIBRC =VCC - BRC (VB - VBE)

> VCE = VCB + VBE VCB=VCE-VBE

VCES, Collector emitter Saturation voltage.

Ics = Vac - VCES

Re

IBS = ICS .

With FB > IBS, hard drive transistor is obtained. VCES become low and on state losses of transistor are reduced. The ratio of IB to IBS 13 Overdrive Factor (ODF)

ODF = IB

Ratio of Ics to IB is called forward awrenty oin &.

Br = Ics

The total power loss PT=VBEIB+VEIC.

# Fransistor Switching performance

A transistor Cannot be traved on instantly because of the presence of internal Capacitance, Whom VBE is applied, IBTIBS, Ic increases to collector leakage custent ICEO OS Zero. At delay time Ed the Collector Current begins to rise. This delay is due to the time required to charge base exsittex Capacitance to VBES=0.7V. After time delay, Ic rises to steady state Ic which is Known as one time to. So ton = Ed + Ex.

When VBE is removed at Er, Collector current does not charge for a time to called storage time. During ts, charge is removed from base. At time ts, Ic falls, KE starts building up. After home top, fall time Ic decreases to Icto. Ver rises to Icc.

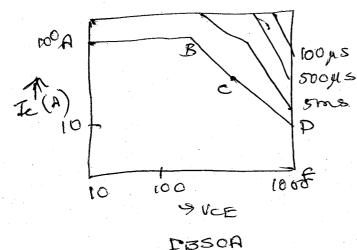

So then off time toff = Est Ef. Sate operating Area: (50A)

Two types of SON ORC FBSON VCE

and RBSOA. FBSON: When base expitted junction is forward

biased to hun on the transistor. Boundary AB is the maximum limit for dc and continuous warent. For VCE < 80V. for VEZ 780V, Ic reduces to BC to limit the junction temperature. For higher VCE current should be reduced to auxid Secondary breakdown. CD is strondary breakelown. DE gives maximum

Voltage capability for this fransistor.

FBSOA

During tuen off, a transistor is subjected to high awent and high voltage with base emitted junction severse biased SOA for then off is specified as reverse blacking Safe operating area (RBSOA). The graph is of Ie Vs VCE! with increased R.B, RBSOA decrease in Size

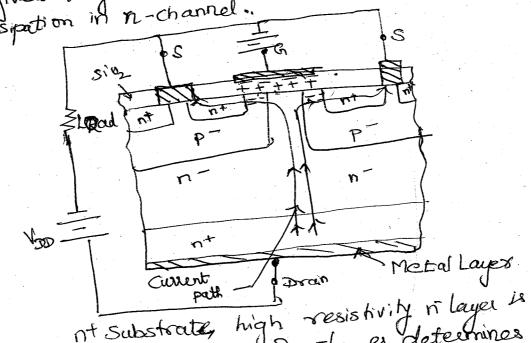

#### Tower MosfeT:

\* It has three terminals down Source and gate. \* BIT is a Gerrent Controlled device whereas MOSFET is a voltage Controlled device. Operation depends on the flow of majority carriers only Mosfer is a cinipolar device. The Control Signal sequised to trigger the MOSFET will be more when Compared to BIT.

\* Gate Circuit impedance in MosfeT is high of the order of 109 ohm.

\* BIT Suffers from Second breakdown Voltage, whereas Mosfer is free from this problem. Mosfer is finding applications in low power high frequency

Mosfe Ts are of two types: n channel Enhancement MOSFET and p-channel enhancement MosfET. n-channel Mosfer is more common because of higher mobility of electrons.

On p-stubstrate two heavily doped ntregions are diffused. An insulating layer of silicon dioxide is grown on the surface. Now the insulating layer is etched inorder to erobed metallic source and deain terminals inorder to erobed metallic source and deain terminals inorder to erobed metallic source and deain terminals inorder to metal is also deposited on Sto2 layer to form the gate of MOSFET.

The gate of

when gate is open, no current flows from deain to Source and load because of one reverse-biased nt-pjundin when gate is made positive with respect to source, an electric field is established as shown.

If Vas is the, n channel becomes roome deep and therefore more awant flows from D to s. The deain absent ID is more awant flows from D to s. The deain absent ID is enhanced by gradual increase of gate voltage, hence enhancement Mosfet.

Disadvantage:

Conducting n-channel in between deain and

Conducting n-channel in between deain and

Source gives large on-state resistance. This leads to high

power dissipation in n-channel.

opitaxially grown. The thickness of n-layer determines the

Voltage blocking capability of the device. A metal Lauper's deposited to form the diain terminals. Now pregions are diffued in the epitaxially grown in Layer.

when gate circuit Voltage is zero, VDD is present, n-pt junctions are severse biased and no current flows from deain to Source, when gate terminal is made positive with respect to source, on electric field is estabilished and electrons form n-channel in the pregion,

Power Mosfet is due to majority tarriers.

Mosfet characteristics:

(a) Transfer characteristics: Load FRD Jo

There is threshold voltage Vast below which the device is off. The magnitude of Vast is of the order of 2 to 3V.

6 Ofp Characteristics; Paves Mosfer indicate the Varietion of obsain current ID as a Function of drain - source voltage Nos. For low value of VDS, the grouph between ID-VDS to almost linear, this indicate as constant value of on-resistance RDS = VDS/ID. For given VGS, if VDS is increased, output characteristics is relatively flat indicating that deain current is nearly constant? VG857 VG54- - VGS1

Switching Characteristics:

At two on, there is an initial delay tidn during which ilp capacitance charges to gate Theeshold Voltage Vast Edn is

called two on delay time.

to called rise time, which

gate Voltage vises to Vasp, a Voltage Sufficient to drive the MOSFET into

on state. During to, drain current rises Ktonk from zoro to full on current ID. Total from on hime ton=tonton.

MAG

Tuen on fine is reduced by low impedance gate drive

Mosfet is a majority casier device, two off process is in itated soon tafter removal of gotte voltage at time to The tuen of delay tof is the time during which i/p Capacitance discharges from ovadrive gate voltage Vito Vasp. The fall time to is the time during which if capacitance discharges from Vorsto threshold voltage. Daving to, To falls to Zero.

Compalison of MosfeT with BJT

1. Moster has lower switching loss es, but on-state resistence and Conduction losses are moved BIT has higher switching

lesses but lower Conduction loss. (ii) MOSFET is voltage Controlled device, BJT is aurent Controlled device

(ii) Mosfet has positive temperature Coefficient for sesistance So le operation is easy. BIT has negative temperature (officient, so current sharing resistors are necessary during parallel operation

iv) In Mosfer, secondary breakdown does not occur, because it has positive temperature overficient, BIT has negative temperature coefficient so secondary breakdown ochur.

V) MosfeT in high to Hage ratings have more Conduction loss Mosfer is duculable in 500V, 140A whereas Bot in 1200y, 800A.

Siefe operating Area of MOSFET: The son of a power Mosfer is much better than that of a bipolar. The Mosfet, being a majority Carrier device, has a positive temperature Coefficient of redistance, and is immune from the hot-spot formation and second breakdown phenomenon that plague the bipolar transistor MosfET are therefore generally rough more rugged than bipodas and Snubber clamp Circuitof can be smaller and less dissipative With Clamp Advantages 1. Overload and peak Gweent handling Capability are high-MosfFT are generally much more rugged and forgiving than bipolars 2. Absonce of Second breakdown reduces Snubber Ciscuitry in switching applications and gives more power handling Capability in linear applications 3. Leakage Current is relatively low, typically in the order of nanoampeles. operating Area of IGBT-FBSOA 28 Square for short Switching times, identical to the FBSOA behavious of the power Mosfett for longer switching the IGBTs are themally limited. 2000 V/45 Reapplied dree at. The RBSOA is somewhat different than FBSOA. The upper sight.

hand corner of ABSOA is progressively cutout and the RBSOA becomes Smaller as the state of change of reapplied Collector to emitter voltage duce/df becomes larger By peoper choice of var and gate drive resistance, the delice asker can control the reapplied AVCE/OUT.

The breakdown voltage of PNP transistor sets the maximum permissible Collector-emitter voltage. The beta of the PNP transistor is quite low, so its breakdown voltage & essentially BVCBO, the breakdown voltage of the drift body unction. A desirable feature of IGBT is the on-state voltage vortion as Varies very little between rooms temperature cand maximum bersperature. IGBT has flat temperature characteristis because of positive and negative temperature Coefficient

Applications of IGBT:

Used in Dc and ac motor drives, UPS systems, Power Supplies and drives for Solenoids, relays & Contactors.

Supplies and drives for Solenoids, relays & Contactors.

IGBT's are becoming popular because of lower gate drive requirements, lower switching losses and Smaller Snubber Circuit requirements.

IGBT are less size, with a range of 1200v, 500A.

Steady state characteristics of MOSFET.

Steady state characteristics of MOSFET.

MOSFET 18 a voltage Controlled device which have high /p

inspedance, Since gate disaeus a very small leakage current on the

order of nanoampaess. Current gain k = ID of order \$109.

Toans Conductance of ID / Vas. / Vas Constant

Foans fee characteristics: of n-channel and p-channel. Mosfer

Vp. Vas

Vp. Vas

(a) Depletion type Mosfer V-ID

VT > VGS

P-channel. B) Enhancement type Mosfer

1. The property of the proper

The of characteristics of n-channel has three regions of operation the of characteristics of n-channel has three regions of operation of ox Saturation region (i) (ut of region whose  $V_{68} < V_{7}$  (2) Pinch off ox Saturation region  $V_{68} = V_{7}$  . The pinch off occases at  $V_{68} = V_{7}$  (3) linear region  $V_{68} = V_{7}$  . In linear region the ID 1 in proportions to  $V_{58} = V_{7}$ . In linear region the ID 1 in proportions to  $V_{58} = V_{7}$ .

Due to high deain current and low chain voltage, Mosfe Tare operated in linear region for switching actions. In Saturation region In Ternains Constant for increase in Value of VDS and toansistors are used in this region for Linear > 4 Voltage complifications. The olp resistance so=Ros= AVDS which is very high in pinch of segion of mega ohms and small in linear region of milliohans. For depletion type Mosfet the gate voltage Could be either positive or negative. Enhancement type mosfer respond to a positive gete voltage org. what happens when gate source voltage is negative (0x) Why negative gothe Vottage is not applied to MOSFET I Vasis-ve, some of the electrons in n-channel area are repelled and a depletion region is created below the oxide layer, resulting in a narrower effective channel and a high resistance from the clean to source Ros. and no Current flow from deain to source IDS=0. This is called pinch of voltage Vr when Vas is the channel becomes wider and Inst due to reduction in Ros.

## GTO (Gate two off)

\* GTO can be twented on by applying a Short Positive gate signed and furled off by negative \* It is a nonlatching device gate signal of

Advantages of GTOS DVer SCR.

- i) Elimination of Commutating Components in Forced Commutation. resulted in lost, weight and Volume to be less

- 2) Reduction in acoustic and electromagnetic noise due to the elimination of Commutation Chokes

- 3) faster twon off

- 4) Improved Efficiency.

Advantages of GTOS OVER BJT in low power applications:

- Highes blocking voltage Capability

2) High vatio of peak Controlleble Current to

- a verage auxent sarge arrent to

3) High ratio of peak sarge arrent.

average arrent.

4) High on state gain.

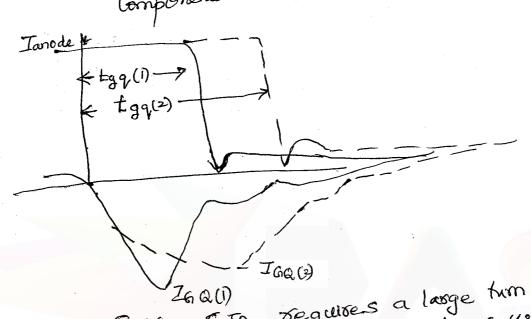

GTO is a latch on device and latch off device. The internal structure and equivalent Circuit is shown,

\* Compared to thyristor, it has an additional nt. laup, near the anode that forms a turn off arount between gate and cathode in parallel with the heen on gate. A large pulse current is passed from Cathode to gate to take away Sufficient charge Carriers from the Cathode (10) exmitted of non transister Q. \* PNP transister con le taken for regenerative \* Q, tuens off, Q2 is left with an open base, GiTo returns to non conducting state. \* GTO has a highly interdigited gothe structure with no regenerative gate Tuen on: A large gate pulse is required to horn on 6.70. \* The sate of sise dight for s I Gm 8) gate ausent digfet affects the device K EGM

\* A longer period is required burn on pulse

if the anodes current

diff is low to maintain I GM Constant untill

anode current see Stabilities.

In state:

\* Forward gate current has to been given

\* Forward gate current has to been given

\* Continuously for whole conduction period. \*

\* Otherwise device does not remain in

\* Otherwise period

Offstate period

\* On gate current should be atleast 1% of

\* On gate current should be atleast gate

from on pulse to ensure that gate

from on pulse to ensure unlation.

### Turn off:

\* Process involves the extraction of the gate charge, gate avalanche period and the anode airrent decay.

\* The initial peak him off current and turn off time depend on the extremal arcuit Components.

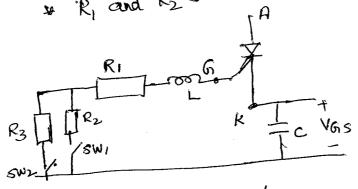

Since Ento requires a large turn off Current a charged capacitor is used to provide the required two off gate

Inductor L limits the turn off dilat of the gate current through the Circuit formed by R1, R2, Sw, and L.

\* VGs should be selected to give the required Value of VGQ.

\* R, and R2 should be minimized.

Turn off arcuit

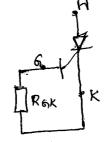

Gate Cathode resistance Rok.

- Gro to be reverse biased by keeping SW, Closed during the whole off state period.

or using a higher impedance Gravit SW2 and Rs. provided a minimum negative voltage exists.

High High impedance SW2 and R3 must

- Sink gate leakage Cursoent.

- In case of failure of auxillary supplies for gate twon off circuit, minimum gate Cathod resistance (RGK) should be applied to make the device in reverse biased.

- \* GTOS are used in voltage source converters where a fast se covery antiparallel diode is required across Each GiTo. GTO do not need reverse voltage Capability. such Gitos are asymmetric Gitos.

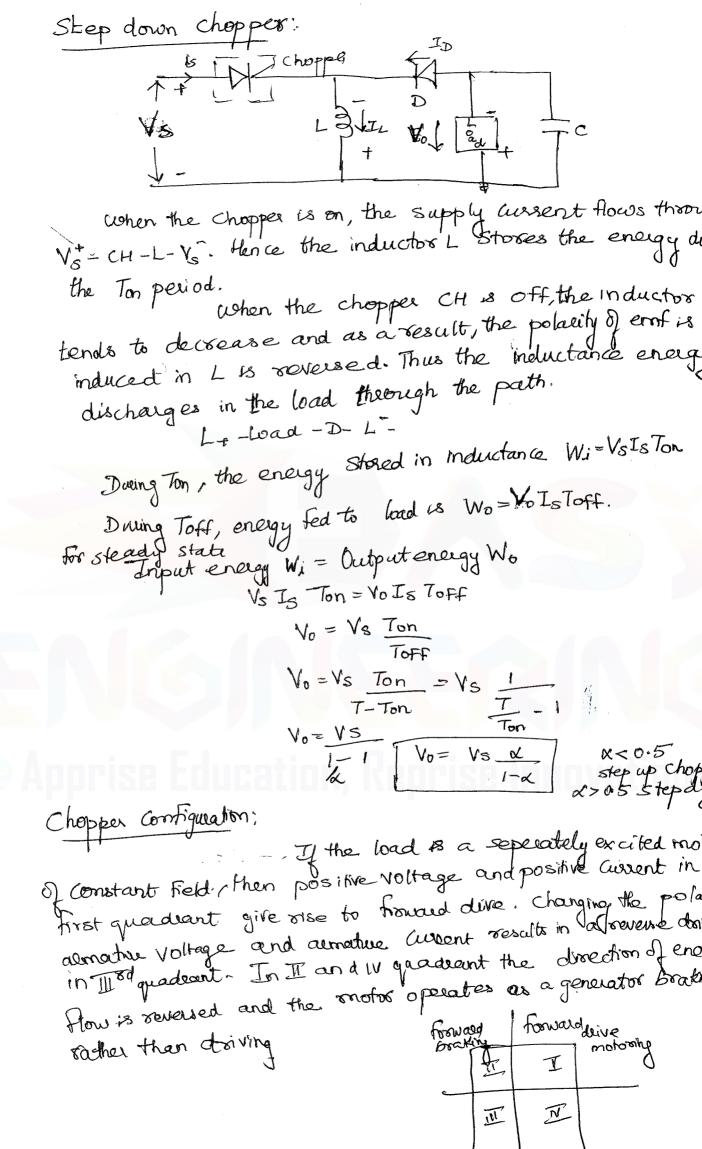

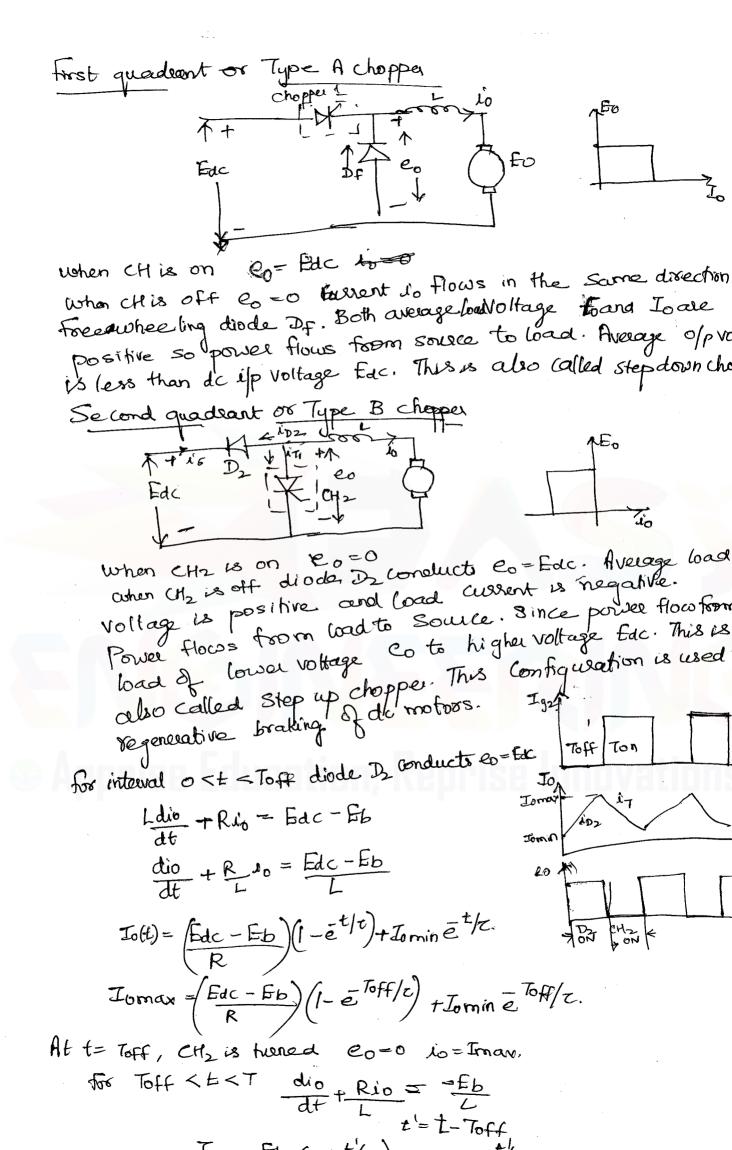

The Conversion of fixed dc Voltage to an adjustab can be carried out by the use of two types of do to d Conversion. Aclink Chopper and Dc link Chopper Hc link chopper: ac is first converted to ac by invester. is then stepped up or stepped down by a bourstermer wh is then converted back to de by a diode rectifier. The Conversion is in two stages, de to ac and then ac to d ac link chopper is costly, bulky and less efficient. Dc chopper It is a static device that converts fixed do if Voltage to a variable de 0/7 voltage directly. are now being used all over the world for sapid townsis System. These are also used in trolley car, marine hoi for lifts toucks and raine harders. The Liture electoic autom one likely to use choppers for their speed control and brakin Chapper Systems offer smooth control, high efficiency, tast desponse and regeneration. PRINCIPLE of chopper operation: It is a high speed on Joff Semi Conductor switch It connects source to load and disconnects the load from Sortra at a fast speed. The chopper is represented by a Switch Sw inside a dotted rectangle which may be huned on or triened off. During the period Ton, chopperis and load voltage is equal to South voltage Vs. During the interval Toff chapper is off, load awaent flows through the Greenhand diode FD. As a result, load terminals are short Circuited by Fo and bad Voltage is therefore, Zoo during Toff. A chopper ac Voltage is produced at the load terminals. The load auxentis antinuous. The average load voltage Vo is Continuous. Vo = Ton Vs = Ton V = QVs At Sw Ton+ Taff Ton-on-time; Toff-off-time Vs Tz Ton + Toff - chopping period

Vo = f Ton . Vs f=1 = Chopping toequency. Control Strategies. Constant forequency System The on time Ton is Valied but Chopping toequency Constant. Variation of Ton means adjustment of pulle co is also called pulse width modulation scheme. This has been reflered as time satio control. For k Toff = Ton = 1 T so that x = 0.25 x = 25%. Ton=3 T so that &= 0.75, 88 x=75% Valiable forguency System: KT-Chopping toequency is varied bad vol and on finefil Ton 4s kept Constant. (ii) Off time Toff is kept Constant. This method of controlling x is also Called forequency modulation. scheme. These are under () Chopping trequerey has to be Toff Varied over a wide range for the Control of of Voltage in Forguency modulation. (ii) For the control of x, toequency valiation would be wide. possibility of interference with signalling and telephone frequency modulation scheme. (1ii) The large off time in Longuerry modulation scheme make the load werent discontinuous which is undesi Curent limit Control= Curent limit: Control Strategy, the Chopp Current in the loa is Switched ON and OFF so that the is maintained between two limit. when Current exceeds upper l the chopper is Switched off. During off period, the load werent for and del coe as exponential. When it breaches lower limit the Chopper is Current limit is possible with constant frequency or with constant

The wad is interpretation

Vo < Vs, so therefore it is called step-down choppe Average of voltage Vo >Vs it is called Stepup Chapper. A Large inductor Lin Series with Source voltage Vs. when the chopped chison, the closed path is shown the inductor stores energy during Ton period when the chapper CHis inductor assent connot die down instantaneously this assent is forced to flow through the diode and load for a time Toff. As the Current trends to decrease, polarity of empinduced i [ 18 revaled. So load Voltage Vo=Vs+L(di/dt). when CH is on, awent though the load would increase from I When this off, arrent would fall from I to I. with OH on, Soulce voltage is applied to L (ie) V\_=Vs. When (4) is off V\_- Voty = 0 or V\_= Vo-Vs. Here V\_= Voltage across L. The energy input to inductor from the source, during the period Ton is Win - (Voltage across L) (average across L) (average across L) through i) Ton  $= V_{S} \left( \frac{I_{1} + I_{2}}{2} \right) Ton.$ During the time Toff, when chapper is off, energy released by inductor to the load is Woff = (Voltage across D) (awage awarent through L) Toff =  $(V_0 - V_S) \left( \frac{I_1 + I_2}{2} \right)$  Toff Vo = Vg T. = Vs T-X. Hor x=0 Vo=Vs , x=1 and Vo=0 when chopper is thened on and off, so that wis variable

when chapper is thened on and off, so that wis variable and the nequested step up armage of voltage, renove than some voltage is obtained.

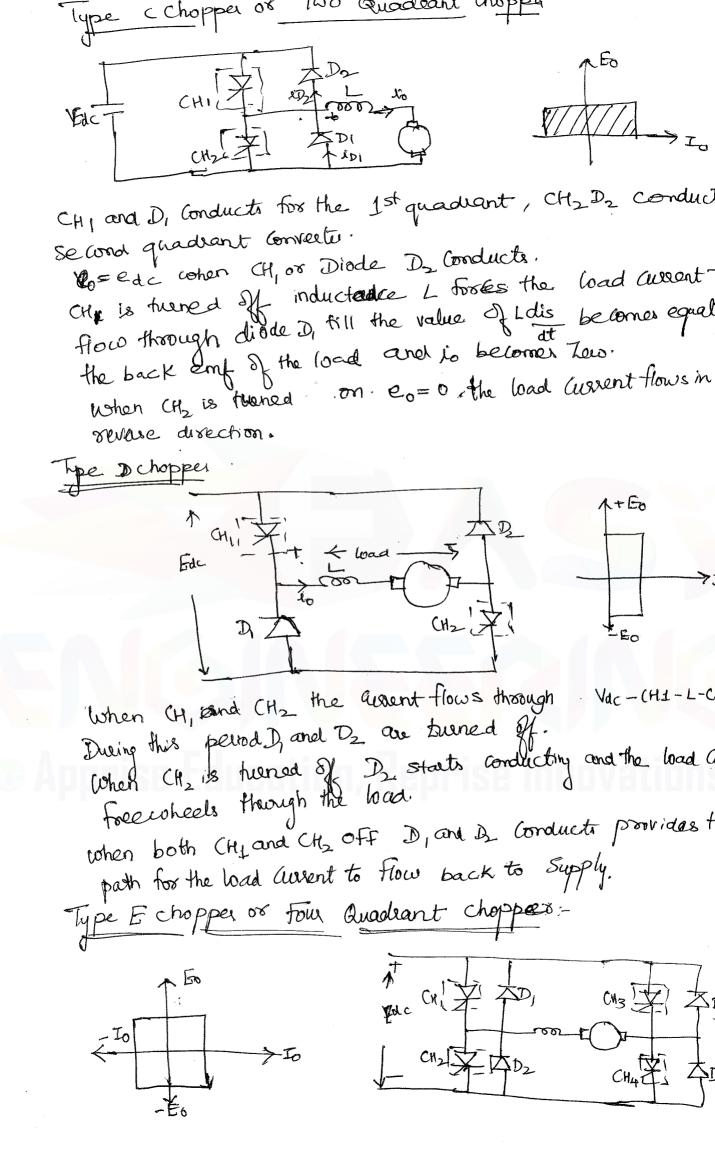

When CH, and CH4 are huned on, awarent flows through Edc-CH, loa bo and to are positive in 1st quadrant operation. When both choppers CH, and CHy are turned off, load dissipate its energy through the path Do-Edct-Edc-D2-load. bois - ve , To +ve, and fourth quadeant operation is possin When CH and CH3 are truned on, aurent flows through Edet - UB - load - CH2-Ede - Both Joand Frank negative in third quadrant. when (1/2 and (1/2 one tuned off, load dissipates 1 to en through the path load -D, -Etct-Edc-Dz-load.

En is positive, To is negative, and se Cond quadrant opera So fine quadrant chapper configuration can be used for a Terresible regenerative ac deive. CH4 is ON, CHB off and CH, is operented. With CH1, CH4 On, V and is begins to flow. Vo & Io are positive giving 1st Quadrant oper CH1 is trained off, positive arrent freewheels through CH4,D2. Se condavoidant CH2 is operated, CH1, CH3 and CH4 are off. with Oh on, reverse assent flows through L, CH2, D4 and E. Inducto Listores anergy during the time CH2 is on.

Listores anergy during the time CH2 is on.

CH3 > hursed off current is fed back to source throng diode Dir D4. Here folding more than source voltage. I diode Dir D4. Here folding is more than source voltage. I diode Dir D4. Here folding is second quadrant operations of positive, Io is -ve and it is second quadrant operations. Some of the source of of chopper so power is fed back to source. Third quidant CHI 18 kept off, CH2 and CH3 is operated. Polo of load ent fromt be reversed. With CH3 on, load gets Connected to source Vs so both Vo, io are negative leading to third quadrant operation. CHz is off, negative current free third quadrant topologion. CHz is off, negative current free theorgh CHz D4. Vo and io can be controlled in III quadrant CH4 128 operated, and other dovices are kept off. touth Quadrant Load emf Emust have its polarily reversed. with CH4 on positive awent flows through CH4, Dz, Land E. Inductance 1

for a Type step down chopper tind the tollowing Validas functions of Vs, Rand duty Cycle & in case load is resisting Hug. of voltage Vo = Ton Vs = XVs Arg. o/p awent  $I_0 = \frac{v_0}{R} = \frac{x \, v_s}{P}$ Output ament at the instant of commutation is Vs/R. For resistive Load, FD does = 0 RMs value. of bee coheeling diode. Current Zero. RMS value of op voltage = TX Vs Average thyristor current = x Vs RMs thysistor werent = Jx Vs (B) Avg. snuce ausent = XVs = Avg. thyristor aurent Effective ilpresistance of Choppers De Source voltage average source aurent A chopper has an input voltage of 2001, and a load of 15 ohm or When chopper is on, its Voltage dep is1.5V and chopping Frequency is If duty Cycle is 80%. Find (1) Average of prollage (2)RMs of pro (3) chapper on time.

Av. of p voltages = x(Vs-1.5) = 0.8 (200-1.5) = 0.8×198.5 = 158.8 RMS 0/pvoltage Vor = VX.(Vs-1.5) = 177.543

chopper on time  $-\infty = \frac{Ton}{T}$   $0.8 = \frac{Ton}{x} \cdot 10x \cdot 10^{3}$  Ton = 0.8

torced Commutations External elements L and c which do not carry the Current continuously are used to turn off a conducting Othyrist Forced commutation can be achieved in two ways reverse voltage. This reverse voltage is applied by switching a previously charged capacitor load current is passed in the reversed direction through Conducting SCR (ii) Current Commutation; the load current, net pulse awsent through thyristor bed

Tero and the device is twented by initally charged a

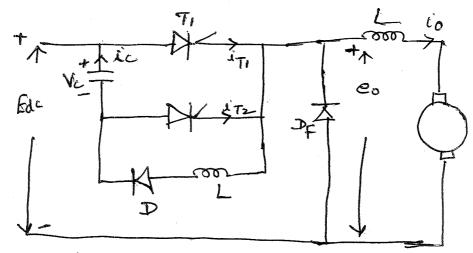

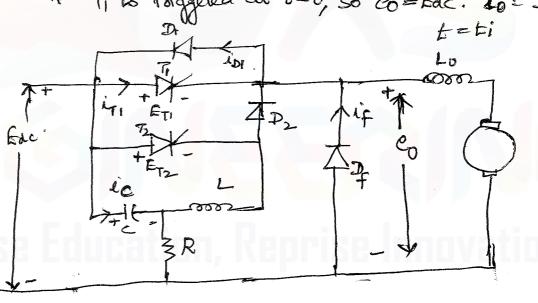

\* Current pulse is generated by initally charged a \* A conducting through a thyristor either Current flowing through a thyristor either Observes Zero due to the nature of load Circuit parameters Load Commutation; (ii) I Example to another device from the conducting the Voltage Commutated Choppel: x The Commutation Circuit Comprises an auxillary

SCRT2, a diode D, inductor L and Capacitor C.

\* The main power Circuit comprises SCRT1

\* Intially the chapacitor is charged by triggering

Ci) Mode 1 o peration:

the paths, load Current io Constitutes one path and commutation current ic, the other path

\* The load voltage is equal to supply voltage Co=E

\* Lo flows through Edc-T, -load-Edc

Commutating current is through CI-T,-L-D-C-

\* ic rises from Zero to Maximum Value. when

Vc be comes zero at  $t = t_1/2$ . \* when ic decreases to Zero, capacitor is charged with the contract of the c

to revewe voltage (-Edu) at t=ti.

\* At t=0,  $V_{72}=-Edc$ ,  $T_{72}=0$

$f = \frac{t}{2} \quad \forall T_2 = 0$   $f = \pm 1 \quad \forall T_2 = \text{Edc}$

ITI= Io, Vc = -Edc.

Mode II operation:

\* To is torggered for huning off the main SCRT,.

Turning on of Tz produces a reverse voltage, as T, which turns off main SCR T,

\* Capacitor Voltage Commutates the main SCR. T so it is called as Voltage Commutated Chopper.

\* T2 provides the path for load aurent is through tdc - C-T2 & load voltage is the sum of source voltage and voltage across capación Co=Edc+Edc=2 Edc. \* load voltage decreases as the Voltage across the Vc = VTI, Eapacitor is directly across Ti through T2. though Vc and V7, Change Capacitos discharge, load, Vc and V7, Change from (-fc) to Zee at (t2+tq) e from 2 Edc to Edc at (tz+tq) \* After (=2+tq), Vc and VII start vising from Zero forwards Fac; eo starts falling to Zero. 1874 Mode TII operation: (t3<t<T) \* At to Vc=VT1 = Edc Co = 0, Capacitor Current de cays to Zero, 72 hens of Naturally \* At t3 Capacitor is Slightly IOM Overcharged Freewheeling diode gets forward biased. イル or Load weight freewheels through dode Df. \* During free wheeling period from to T; Y2 = - ve When Capacitor is overcharged vc) 4 1c=0, dT,=0, 1= Iom, V7 = Edc, Co=0, 172 = 0. <del>G</del>d4,

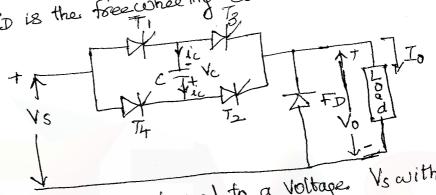

## Current Commutated Chopper:

\* T, is the reain thy istor

Commutation Circuit consists of auxillary thysistor 72, a

Inductor L, diodes D, and Dz. or Df is the free wheeling diode, R is changing resistor.

\* Ties commutated by a current pulse generated in the Commutation Circuit.

Reverse voltage across the device is applied through Connected in antiparallel to the SCR.

\* Energy for Current Commutation Comes from energy of in a capacitor.

\* Capacitor is charged to a Voltage Edc through Fact- C-R-Edc .

+ 7, 18 toiggered at t=0, so co=Edc. To= Ion

Mode I operation:

\* At time t=t, auxillary thyristor 72 is triggered to commutate main thypistor T1.

\* When To is two ned on, oscillatory cutrent is set up i

the Circuit Consisting of C, 72 and L. \* At to, the capacitor cussent is reverses, To gets here

Mode II operation: \* To is thened off at to, oscillatory ament ic flow through C, 4, P2 and Ti. to at tz, General ic flows through theistor T, and not through I to flows in opposite direction which decreases the \* At t3, ic=iT, net awent through T, 18 Zerro and thens off. As oscillatory werent thems off, it is called as awent commutated chopper. award it Mode III operation: \* Ti's thened off at t3, \* ic becomes more than io. \* Affatz, ic supplied boad auxent is and diode I begins to conduct the auxent (ic-to) and the deep in D, due to this convent Keeps the thyristor Ti reverse biased for the time to (E4-t3). RAt ty ic=io, iDi=0, Dis R.B. - After to, a constant current equal to is flows through Ade-c-L-Dz-load and apacitos c is charged linea to Fac at ts. During the period (ta-ts) ie=io. \* Vc=ft1, eo=Edc-Vcat =4 and ts-, Vc=Edc... x, At to eo=Edc-Fac=0 \* Ve increase line asity and load voltage codecreases t Mode I operation: \*At to, capacitor is overcharged to Voltage greater than source voltage Edc. \* Df becomes F.B and starts to conduct the load

\* At to te=0, Ve mones " one won the \* Interval to to to in=ic+if, ic decays, if builds up. At to / lif = lo . and lc=0. \* from period to, load auxent freewheels through Df ar Lecays \* As Kis Zero, Dz is open ascuited, Vc decays then Rfor free wheeling period of chapper. \* At K=T, T1 & triggered and cycle repeats reigi /kc=10 icn 06 WH F727 71-

# Load Commutated Choppes

4 It consist of four thyristors 7,- 74 and one commuta Capacitor. C. The thyristor 7, and 72 acts as one power and To Ty acts as second pair for Conducting the load Curley

\* To and Iz are main thyristors, T3 and T4., C is the Comm alternately.

\* FD is the free wheeling diode across the load.

The Capacitor is charged to a Voltage. Vs with appears negative and lower plate positive.

Trand 72 toiggered at t=0, the load current flows the Vs, T1, C, T2 and load, the load Voltage shoots to, Vo = Vs+Vc = 2 Vs. Load Covert flows from Source to

\* Capacité charges form Vs at t=0 to -Vs at t \* when voltage becomes is, the load voltage falls

toom 24s to 0 at t=t1.

\* Att = 0, T, and To are thered on, To T4 reverse bias by Capacitor Voltage

\* At t=t1, T, and T2 are horned off, T3 T4 forward be

Mode II: \*At t, Capacitor slightly overcharged, Freewheeling diode gets forward bidsed and load arrent founderre from T, T2 to fD.

Mode-III At to, 73 T4 is triggered, load voltage at once becomes Vo=Vs+Vc=ZVs. \* T, and Is all reverse biased, and thened off at to \* Load current flows through Vs, T4, C, T3 and load charges capacitor linearly from (-Vs) at to Vs at \* Load voltage falls from 2Vs at to Zero at t \* During (t3-t2); ic=-Io, VT1=VT2=-Vs at t2 and Vsat. tz. Mode 1 YIO Mode-II ヒノセくも o<t<t, 14 Mode III, to <text3 **V**0 21/5 2Vs ica

Buck Converter: i'c,Ic The converter produce a lower average output voltage to that the dc input voltage Edc. By Valying Ton/7 the average Output voltage an be controlled. Fransistor T, is switched on at time t=0. The supply arrent flows through filter inductor, filter capacitor and load resistor R. The inductor ste energy during the Ton period. During the interval when toans is on, diodel is reverse based and the input provides energy to the load as well as to the inductor. Now lat instant t= 75 foursistor Ties Switched off. During the interval. when transist is off, inductor awant flows through L, cloud and face idealing diode Dr and here diode Dr conducts. Voltage across inductor L EL=Ldi dt Edc Duling time Ton, the inductor Current ILA vises theaty from I, to I2 Iz  $Edc - Eo = L\left(\frac{I_2 - I_1}{Ton}\right)$ I Pac-Fo = DIL Ton IsA Ton = AI.L ic. During Toff i'r falls from Iz to I, I2-I0 - FO = -L SI I, To NC=-EO Toff = AI.L DI = Edc-Fo Ton = Toff Fo Fo tac Ton- Fo Ton = Toff Fo So Toff + Go Ton = Editon to (Toff + Ton) = Edc Ton For T = Edc Ton Fo = Edc. Ton: Fo = & Edc X = Ton

Edc Is = to Io = x Edc Io Is = x Io T=Ton + Toff T=AIL +AIL

fdc-fo Fn T=L=DILFdc DI= EO(Fdc-Fo).T I = Eo (Edc-Eo) F.L. Eac ΔI= Eo(Edc/Edc - Eo/Edc)

F. L. Edc/Edc

X= Eo

Edc ΔI= α Edc(1-α)

F. L 1'L=1c+1'0

when load sipple assent DIO is very small then D The average apacitos awaent which flow's for Ton/2 + Toff

Capacitor voltage is expossed as

Vc= [icdt + Vc(t=0)

Peak to peak ripple voltage of Capacitor is

$$\triangle V_c = V_c - V_c(t=0)$$

$$= \frac{1}{2} \int_{C} dt$$

AVC = bo (fdc - bo)

$$\frac{2 \text{Vc} = \text{Edc} \propto (1-\alpha)}{8 \text{ LC} \cdot f^2}$$

The main application is in regulated de power supplies de motor speed control.

Disadvantage:

- 1. The ip assent is discontinuous.

- 2. Input fitter is required for smoothing purpose

3. It gives one polarity of output to large and unide ordant current. circuit needed for diode Df be

DOOSE Converse (31934) Edc The output voltage is always greater than if p voltage. The inductor stores energy during on period ton. Diode DF is reverse biased and is plates the orutput stage. When the power transistor is off, the olp stage receives energy from the inductor as well as from the input. The awrent which was flowing through the transisted would now flow

through L, Df, c and load.

During Ton Edc = L(I)-II) = LAI Ton Ton Ton = DIL Dury Toff

Edc-Eo=-LAI Toff = DIL Eo-Edc

Assuming a loseless circuit Pi=Po tdcIs = Eo Io = EdcIo

Average if current Is= Io

T= 1= Pont Toff F= DIL + DIL Edc Fo- Edc

TEDIL EO Edd(EO-EdC) Peak sipple awnert

AI = Edc(Go-Edc) FLEO

$$I_{2}$$

$$I_{3}$$

$$I_{4}$$

$$I_{5}$$

$$I_{6}$$

$$I_{7}$$

$$I_{7$$

DVC= IoTon

Ton = <u>For Edc</u> Toff

Edc = Fo Toff = to Toff of

Go Toff -f

Ton=(fo-Edc) Toff = fo-Edc Fo Toff of Fo.f

Applications 1. Regulated de power supplies 2. Regenerative boaking of de motors Advantages.

1. Regulator steps up the voltage 2. High efficiency 3. Input assent is Continuous. 1. High peak current thous through transistor. T.,

2. Average of voltage is very sensitive to the

in duty cycle x. Dis advantages: 3. Circuit needs larger filter capacitors and larger be cause of higher rms Eurrent flow through

Buck Boost Regulator: A buck boost regulator provides an output voltage greater or less than ip voltage. This is also called inverting regulator since the output voltage polarity is opposite to that of the supply volt Two modes of operation Transistor Ti two ned on by the base signal Mode I \* At t=0, Ti comes to ON state and dioded Dis reverse biased & . Is flows through T, and inductor L., \* During the on period inductor stores energy and inductor current increases from I, to I2. Vs Mode I \* At t=t, Fransistor T, is Switched off. \* Current flows through inductor L, Capacitor C, and Diode: forward biased. and also to load. & Inductor current decreases from Into I, \* Voltage across the inductor is -Vo.

Analysis: Inductor current increases from I, to Iz in on the peliod  $V_8 = L I_2 - I_1 = L \Delta I$ Ton Ton = AIL AI=Vs Ton 0 Inductor current decreases from I to I, in the off period of chap Toff = - DIL DI = - Toff Vo Company eq O & D Toff

AI = Vs Ton = -Toff Vo

L Vs Ton = - Toff Vo Vo = - Vs Ton = -Vs X

Toff T-Ton I-A X-duty Cycle = Ton output vottage  $V_0 = -\frac{V_S \alpha}{1-K} = -\frac{V_S \text{ Tonf}}{1-\text{ Fort}}$ Vo (1-Tonf) = - Vs Tonf Vo - Vo Tonf = - Vo Tonf = - Vo Tonf + Vs Tonf = Vo Assume no loss in avant  $V_SI_S = -V_OI_O = \frac{\alpha V_SI_O}{1-\alpha}$ Is= Iod I-x Switching period Te Ton + Toff = AIL + AIL

VS VO

T = AIL(Vo-Vs)

VsVo When Transister is on, apacitor DI= Vs Vo Supplies the load award FL(Vo-VS) AVe= LJ Tedt = Io Ton NI=VSX FL Sub  $Ton = \frac{Vo}{(Vo - Vs)f}$   $\int \Delta V_c = \frac{IoVo}{(Vo - Vs)fc}$

Resonant Converter The switches are made to trun on and turn of at the entire load Current at high diff. The devices how high dilat experience high Voltage stoess across them. because of this high power losses in switching devices. If size and weight of components are increased, swift frequencies are increased! Another deawback is high du and du/at courses electromagnetic interference. These problems can be minimised by when each Switch can be truned on and off when the voltage account or current throughit Zero at the instant of switching. The converter which employ zero voltage and Zero auseent. The converter which employ zero voltage and Zero auseent. Zero arrent Switching Resonant Converters when the switch awent is zero, there is a current i= gd Flowing through the internal Capacitance c; due to finite slope of the switch voltage at them off. L- lype ZCS; lo=Io Le Sistened on and diode Dm Conducts. it= Vst ostst, Mode 4 Sion, Don is off I'L= Io-Im sincuot

LL= Imsinwot + To こんかる Vc=Vs(1-60540t) Ve(pk) = 2Vs since t= 3 fc  $\sqrt{c_2} = \sqrt{2} \sqrt{s}$   $E_2 = \sqrt{2} c$

Vc= Vc3 - <u>To</u> t Vc=28 aswot

$i_{L=0}$  at  $t=t_3$ Vc(t=t3)=VC3.

#4=Vc3 E

roue (05t = ts) when Capacitos Voltage tends to be negative diode Dro G Load awent Io flows through the diode Drn. Es= T- (t1+62+63+64), The peak switch voltage equals TotIm the Supply voltage Vs. since the Switch durient is zero at hun off and tun on, the switching loss becomes Very small. The peak becoment accord 10 wheest be greater than the boad autent Io. this sets a limit on the minimum Value of load resistance R. By placing an antiparallel diode across the switch, the ofp voltage can be insensitivite to load variations M-Type ZCS & Resonant Converters - Vs Mode I To mode 2 Mode 3 Ic + Vs Mode 5 Mode 4 Mode 3 Mode 2 Mode 1: IL= VSE Vc=Vs Coswot Vc=-Vs Coswo VCCPK)=Vs at and &t2  $V_c(t=t_3)=V_{c_3}$ I'm Conducts. £ = IoL/Vs Vc (tz =2) => Vs Mode 4: To tim t= +4, Vc(t= +4)= Vs E4 = (Vs - Vc3) C/IO To **V**\$  $\bigcirc$

Zero Voltage Switching Resonant Converter: The switches are towned off and then on at Zew voltage. The Capacitor C is connected in parallel with the switch si to achieve ZVS. If diode is Connect in series with S, the Voltage across a conoscillate freely and switch is operated in a fill were confiqueation. ZVs resonant converter is the dual of 20 s resonant converter. 41 Si and diode Don are off, Capacitor C charges at a Constant rate of boad assent  $V_c = \frac{Iot}{C} \cdot V_c(t=t_i) = V_s t_i = V_s c/I_o$ Mode 2: 0 SESt2. Si is still off, but diede. Im hours off. Vc = Van Sinwot +Vs Vm=IoVI/c VT(PK)=VC(PK)= TO VE +VS The inductor current iL = Io coswot. Vc (t=t2)= Vs il (t=t2)=-Io. Mode 3 - 0 5 t 5 t 3. Vc = Vs - Vm sinwot Ve=Vs-Vmsinuot il=-Iocoswot. ty = Vec Sin x. X= Vs/Vm Mode 4 S, is huned on, diode Dm remains on, 4=ILStYst. Modes. OSESES. Sis on but Done off. Load assent To flows through the switch. This mode ends at time t= t5. £5=T-(t,+t2+t3+t4), ZNS converter are used for constant load application. The pear Switch voltage dependent on load awent to. 5, must be trened on at Zeio Voltage otherwise energy will be dissipated. To avoid this Di must conduct before thening on the switch. Mede 2  $I_{o}$ Mode 5 Mode 4

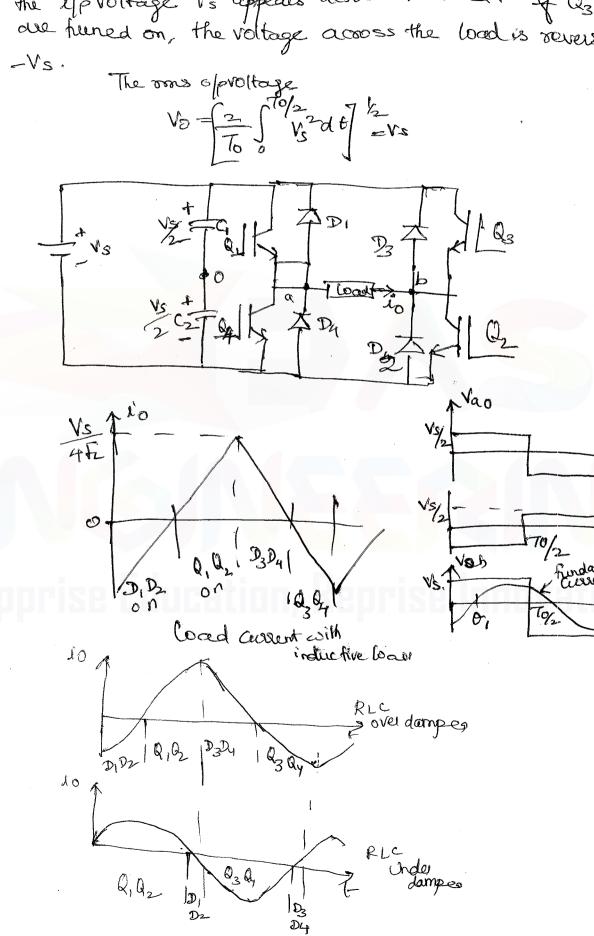

3) Inveiters De to ac Converteus are known as inverteus. The function of inverter is to change a de i/p voltage to symmetric ac of voltage of desire a magnitude and frequency. The of voltage Could be fixed or variable at a fixed or Variable frequency. The opprottage of ideal inverter should be Sinusoidal. For low and rove diwin power applications, square wave or quasi sq wave voltage but for high power applications, low districted Sinusoidal waveforms are objusted. The harmonic Content of ofp Voltage can be minimized as reduced significantly by switchin Inverteus are used in industrial applications like variable sp ac motor doives, induction heating, standby power supplies, and bethriques. uninterraptible pouver supplies. Inverteur all classified into two types (1) single phase in and 2) those phase inverters. Each type can use controlle from on and true off devices. The inverters generally use Phim control signals for producing an ac opp voltage. An inverter is call ifp to voltage fed inverter (VFI) if the isp voltage remains constant Constant fed inverter (CFI) if the isp current is maintained constant A variable de linked inverter if the ipproltage is Contoollable. Principle of operation; Vao=Vo when one to ansistor Q is turned on for a time To/2 the instantaneous Voltage across the land to is Vs/2. If transistors a is only tuened on a time To/2, - Vs/ appears across the load: (I), and G2 are not tuened on at the same time. The inverter requires a three cuire de source and when a transistor is off its reverse Voltage is Vs, instead of Vs/2. This inverter is known les a hay boidge Inverter soms of voltage  $\frac{T_0}{T_0} = \frac{12}{4} \frac{V_5}{4} = \frac{V_5}{2}$ . For inductive load the load assent cannot change invalidably

of Qis truned of at t= To/2; the load current would continue to the fly by load and lower half of dc Source untill the current fall

When diode Dioo De wonducts, energy is fedback to do sou and these diodes are known as feedback diodes. Single phase bridge Inveder

A single phase Voltage Source inverter is shown It consists of four choppers. When Q, and Que hered the ilprollage Vs appears across the load. If Q3 and 6 are huned on, the voltage across the load is reversed o -Vs. The orans approllage

Vo = \[ \frac{2}{70/2} \frac{70/2}{V\_5} \d \text{d} \frac{1}{2} \text{vs} \] Thouse 太 Dy Vao ල 76 fundamental ioi

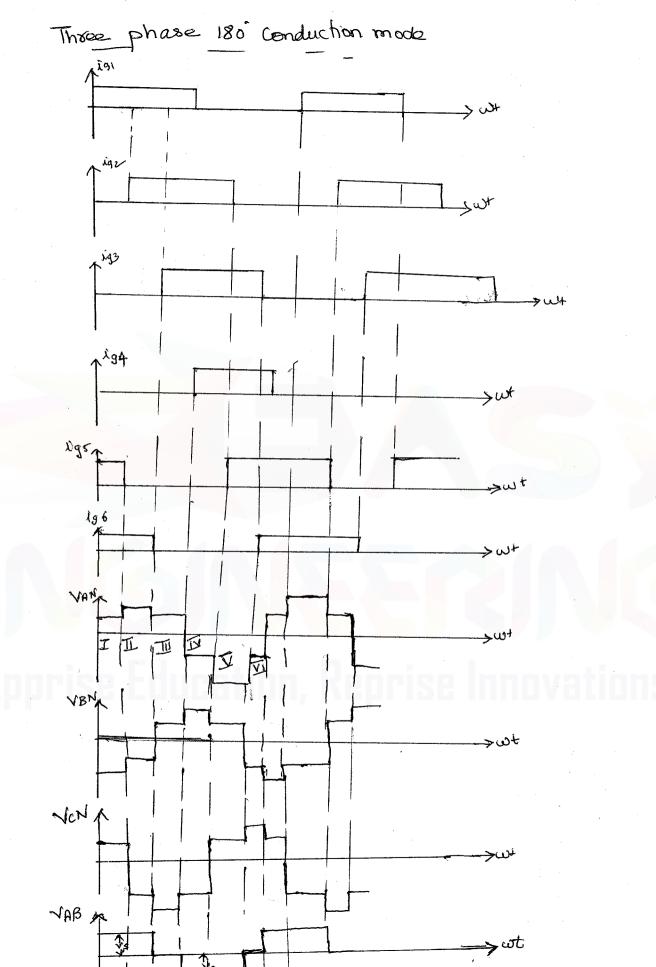

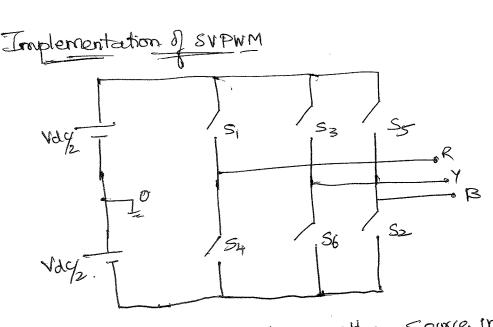

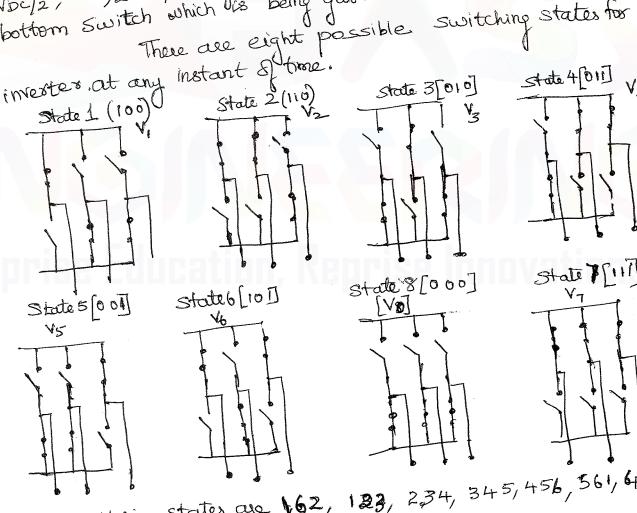

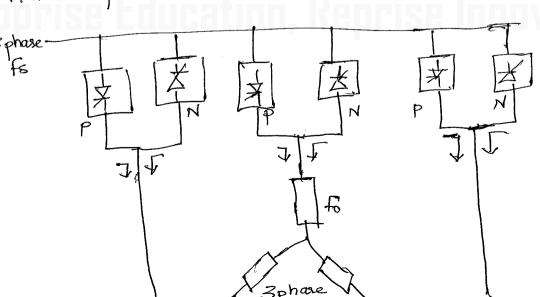

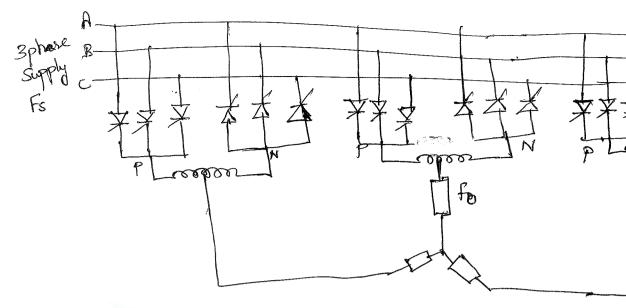

Three phase Bridge Inverters In applications such as UPS and ac motor dures, phase inverters are used. It is possible to supply a threeload by mans of three seperate single phase inverteus, where each inverter produces an oppdisplaced by 120. with respect to each other. The inverter is termed as six boidge inverter. In inverter a step is defined as a change in the fixing foom one thyristor to next thyristor in proper sequence. For a cycle of 360, each step would be of interval for a six step inverter. There are two possible Scheme of gating the thyristors. In one scheme each thyristor conducts for 180, In other scheme each thypis Conducto for 120. P A maximum of these thyristons conduct at any instant 188 conduction mode and each SCR Coorducts For T radians. in every cycle of the o Thypistor pair in each leg, (e) Ti, T4; T3 T6; and TgUT2 are tuened with a time interval of 180°. Each SCR 7, conducts for 180° and SCR 74 for next 180° of a cycle. Therestors in the capper george (fe) 7,173,75 Conduct at an interval of 120°. If SCR 7, is treed or, Tymust be triggered at 120° and 75 at 240°. Source is four for lower group of thyristors.

Tito To - I interval 7, To To > II interval, Tito To - III, 747372 - IV interval 747375, - V interval 747675-VI of si dusation only there sees are conducting

TVO a. Star Connected load, the line to newboal volt must be from determined to find line or phase au Ci) During interval I for 0 ≤ cot € T/3. (T, T6 T5) Reg=RB+(RAILRC) = R+R/2 = 3R  $T_1 = Edc = 2Edc$  RB = RB + RB = RBI=Edc = 2 Edc Reg 3R FAN = ECN = IIR = Edc FBN = - IIR = - 2Eds (ii) II interval  $T_{/3} \le \omega E \le 2\pi/8$  (7.7672) P NB Reg = R + R/2 = 3R/2  $T_{D} = Edc = 2Edc$  Reg = 3R  $T_{-} Edc = RA$   $T_{-} RA$   $T_{-} RA$   $T_{-} RA$ EAN=I2R=2Edc EBN=ECN=-IR=-Edc (Mi) III intowal In swe < x Reg=R+R/2=3R/2 I3= Edc = 2 Edc Req 3R. EAN = EBN = I3R = Fdc ECN = -I3R = -2 Edc 3. Line Valtage FAB=EAN-EBN & EBC=EBN-ECN; ECA=ECN The phase voltages have Six steps per cycle and line ve have one positive pulse and negative pulse per cycle The instantaneous line to line Voltage FAB EAB = E 4 Edc Cos no Sinn (wt + T/6) EBC = 5 4 Fdc Cosming sin n(wt - T/2) Ene to line RMS voltage  $E_L = \begin{cases} 2 & \text{fdc. GS n$\tilde{n}$} & \text{fin} n \text{ (wt-} 7\tilde{n} \text{)} \\ & \text{fine to line RMS voltage} & E_L = \begin{cases} 2 & \text{fdc. a(cut)} = \sqrt{2} & \text{fdc.} \end{cases}$

Comparison of two Conduction mades? Fun 180, when Ig, is seemoved to two off SCRT, at wt =

gating signal Ig4 is Simultaneously applied to two on SC Ty in Same leg. \* Commutation interval must exist between the rem of Ig, and application of Ig4 for proper and reliable operation of this problem can be avoided by 120° mode of Conduction This problem can be avoided by 120° mode of Conduction of This problem can be avoided by 120° mode of Conduction of This problem can be avoided by 120° mode of Conduction of This problem can be avoided by 120° mode of Conduction of This problem can be avoided by 120° mode of Conduction of This problem can be avoided by 120° mode of Conduction of This problem can be avoided by 120° mode of Conduction of This problem can be avoided by 120° mode of Conduction of This problem can be avoided by 120° mode of Conduction of This problem can be avoided by 120° mode of Conduction of This problem can be avoided by 120° mode of Conduction of This problem can be avoided by 120° mode of Conduction of This problem can be avoided by 120° mode of Conduction of This problem can be avoided by 120° mode of Conduction of This problem can be avoided by 120° mode of Conduction of This problem can be avoided by 120° mode of Conduction of burning on of T40 \* SCR T, Can be Commutated Safely. \* No short arcuit occus between the sameleg. and one terminals remains open for all characte \* So 180° is preferred in three phase inverters.

Three phase 120 Conduction mode: Each thylistos conducts for 120°. At any instant, only two this for ordinain on. Like in the above case each Thyristor conducts for 120°. The firing sequence are given below. Iinterval - 7,76 - 15 - Ta Ta - 73 74 -T5 T4 - 75 T6 Each thylister conduct at a firme, one from copper group other from lower group. (1) IInterval, 0< wt < T/3 7,76 Conduct. FAN = Fdc FBN =- Fdc FcN =0 (ii) I interval 7/3 Swt 527/3, 7, 72 Goodwet. EAN = Edc EBN = 0

Edc RB RC FCN = -Edc

The second results of the III interval 27/3 5 wt 5 35/3. To To conduct GAN = 0, EBN = Edc ECN = -Edc/2 The line to newtood voltage GAN = 2 2fdc (osnā sinn (wt FA/6) GBN = 5 2FAC COS NT SIN N (WF-T/2) 62N = = 2 2Fdc Gosna Sinn (wt -71/6) There is a delay of The between the friening of Tound funding of 74.

ELn = 4 Edc Cos no ELi = 4 Edc Cos 30 ELI = 0.7 797 Ede 18x A  $\Rightarrow_b$ 192 K L'SB 8 CANA Bays -264c EUN 2 Fds GO BA

Voltage Control of Investors: The output voltage of inverter may not remain Constant due to the Variations in the input voltage and Voltage does in invector. The methods used are a) External Control of ac output voltage b) External Control of dc input voltage c) Internal Control of Invester. External Control of Ac output voltages \* Ac voltage Controller is insexted between the out terminals of invertex and load terminals. By tontrolling ac voltage confoolles using the firing angle, the voltage is to acload is regulated \* This method produces higher haemonic content in output voltage, when the output voltage from the output voltage from the occivoltage Controller is at low level. Constant

[ Joventes ] Ac Voltage Controlled

[ Controlled | Ac load |

Controlled | Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

Controlled |

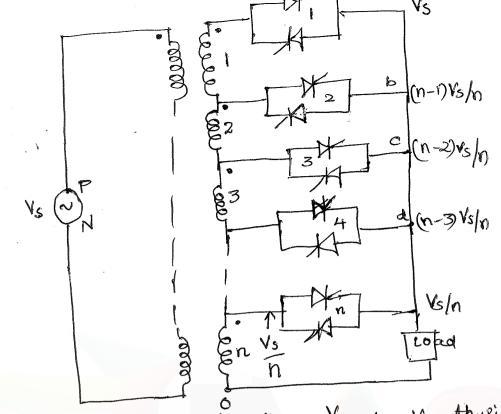

Control Extremal Control of DC Input Voltage through a fully controlled rectifier, uncontrolled rectifier and Chapper, or through an ac voltage controller and an Uncontrolled rectifier. \* In case the available voltage isde, then de inpi Voltage is controlled by chopper. 1. The output voltage waveform and harmonic Content not a ffected as the invertex output voltage is Controlled. Advantages of Vottage control schemes

- Number of power converters varies from two to three. Hence more losses and reduces efficiency of entire so for reducing the ripple content of dc voltage input to inverter, filter circuit is regulated which invertes the cost weight and size and at the same time reduces efficiency and makes the transient response As the dc input is decreased, the Commutating Capacitor voltage decreases. Constant Filly Contoolled > Filter Controlled Invester ac voltage Voltage Constant Uncontrolled Chopper Filter de Inverter ac voltage Constant Ac Voltage | Vniontrolled | Filter | de Voltage | Voltage Constant chapped Filter devoltage Inverter ac voltage Internal Control of Inverters:

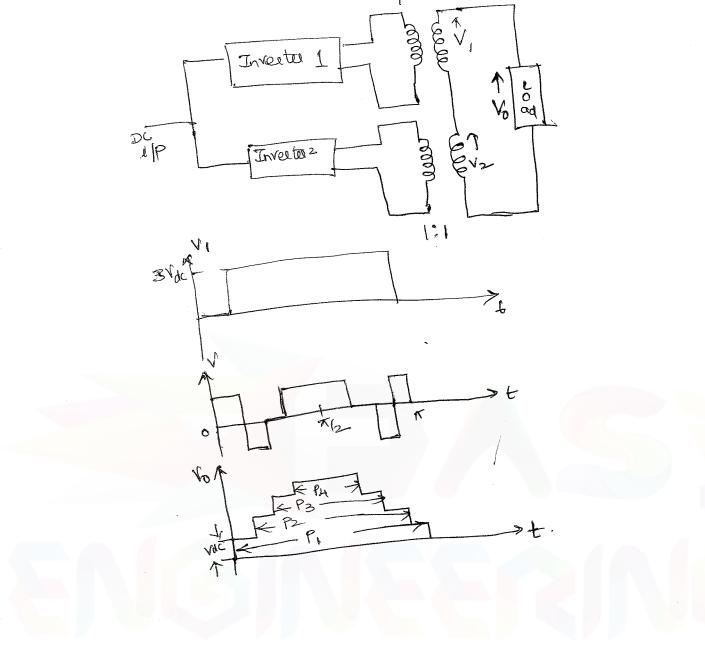

- Invester Controlled Internally by two mether (ii) Pulse width Modulation (ii) Pulse width Control (iii)

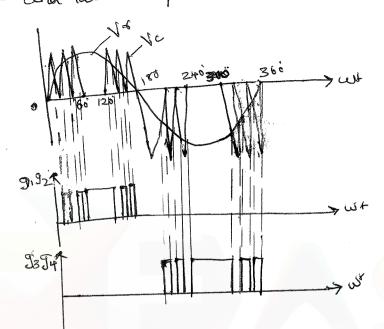

1. Sexies Investex Controlin Trester-1 31/8/01 Invertex-II 3 6 Voz The output voltage of two investers can be summe up with the help of transformers to obtain an adjustable output voltage. The inverter output is fed to two transfor se condaries are connected in series. Vo = [Voit Voz+ 2 Voi Voz GSO]/2 The frequency of VOI NO2 from two inverters is som 0=0, Vo=Vo(+Vo2, Vo= 0 in case Vo1=Vo2 The series connections investes is called mult Converter Control. Palse width Modulated Inverters: The width of the pulses are modulated to ob invertex output voltage control and to reduce its harm Content. Different PWM techniques are (a) single pulse modulation (b) Multiple pulse mod (c) Sinusoidal PWM (d) Modified Sinusoidal PWM. Multiple pulse Modulation; Several equal pulse per half agre, are obtained sina raforance signal with a triangular Gellier

The Carrier Frequency determines the number pulses per half cycle in, whereas the frequency of reference Signal sets the output frequency for 刘东长 The briggering pulses for thyristors are generated based on the intersection of Carrier and reference signal wever. When Vc >Vr pulses are generated. Corrier Frequency Fc determines the number of pulse per half gicle. Modulation is the ratio of Carrier Frequency to reference toequency The number of pulses per half cycle. Variation of Modulation Varies from 0 to 1, Pulse width Vacies form o to T/Np. output voltage from 0 to Vs. The rms ophput voltage VL(rms) = \( \frac{2Np}{2\tau} \) \( \frac{\tage}{2\tau} \) \( \frac{\tage}{2\tage} \) \( ( Np-1)/2 VL(coms)=Vs/Np.P

Sinusoidal pulse width Modulation? in Several pulses per half cycle are usedosin the Ca of Multiple pulse modulation. The width is equal for all pu In case of sinusoidal pulse modulation, pulse width is Sinusoidal function of angular position of the pulse in a \* A high Frequency carrier wave Ve is compared a a sinusoidal reference wave Vr of the desired frequent \* The intersection of Vo and V8 determines the switching instants and commutation of the modulated pulse \* Vc is the peak value of toingular carrier wave Vois the reference or modulating signal. I When modulating signal is higher than towardular signal the pulses will be generated. +. There are N pulses per half cycle. When triangular Carrier wave has its peak Coincident with zem of reference signal. \* The ratio of VX/Vc is called modulation index and it Controls the harmonic Content of of prottage waveform. For MI < 1, largest harmonic amplitudes in the opp voltage are associated with haemonics of order feft+1,00 2N+1. By increasing the number of pulses, order of dominant harmonic Frequency can be raised which an be fittered easily (ii) For MI>9, lower order houmonics appear, since pulse

Modified Sinusoidal Pulse width Modulation;

Sine and Triangular wave are compared to gener the pulse. Triangular is the carrier signal which is applied for first and last 60° per half cycle. (o to 60° and 120° to 18

when Vo > Vc pulses are generated. The output pulses are Fed to inverter.

Advantages:

\* Fundamental Component is increased

\* Harmonics characteristics are improved

\* Reduces the number switching of power semiconductor devices

\* Switching losses are teduced. Reduction of Harmonics in the investor output voltage >

\* The output voltage of investes may have hasmonic a much higher than 5% of its fundamental Component. or filters are connected between the bad and invest

bring the harmonic Content to a reasonable le & For high frequency harmonics, low size filters used; for low frequency harmonics, fittel size inco

on makes the circuit bulky, costly and weight

Harmonic Reduction by Single PWM The width of the pulse is adjusted to reduce the harmonic. The RMS value of the amplitude of harmonic Voltage of a single pulse modulated wave is given by VLn = 4Vdc sinnp = 2\sqrt{2Vdc Sinnp P is width of pulse, To reduce third order harmonic, VL3 =0  $V_{L3} = 2\frac{\sqrt{2} \text{ Vdc}}{3\pi} \sin \frac{3P}{2} = 0$  $\sin \frac{3P}{2} = 0$ Illy to Eliminate 5th harmonic P= 72° Harmonic Reduction by Multiple Commutation in Each Half cyc Instead of having Commutation at the end of half Cycle, some more Commutations can be created in the hat Cycle. By selecting propos values of  $\alpha_1$  and  $\alpha_2$  lower order harmonics can be reliminated. The amplitude of voltage wave Vdc. Multiple Commutation. employs four Commutation per cycle instead of one. For annodulated square ware, the Voltage waveform has quarter wave symmetry. Br=0 An = 4 Kdc Isin nort (down) - I sin nort (down) + I sin nort down  $= \frac{2 \text{ Vdc}}{R} \left| \frac{1 - 2 \cos n x_1 + 2 \cos n x_2}{n} \right|$