# EE 8551 MICROPROCESSORS AND MICROCONTROLLERS L T P C 3 0 0 3

# **OBJECTIVES:**

- To study the Architecture of uP8085 & uC 8051

- To study the addressing modes & instruction set of 8085 & 8051. •

- To introduce the need & use of Interrupt structure 8085 & 8051.

- To develop skill in simple applications development with programming 8085 & 8051 •

- To introduce commonly used peripheral / interfacing •

# **UNIT I 8085 PROCESSOR**

Hardware Architecture, pinouts - Functional Building Blocks of Processor - Memory organization - I/O ports and data transfer concepts- Timing Diagram - Interrupts.

# **UNIT II PROGRAMMING OF 8085 PROCESSOR**

Instruction -format and addressing modes – Assembly language format – Data transfer, data manipulation& control instructions - Programming: Loop structure with counting & Indexing - Look up table - Subroutine instructions stack.

# **UNIT III 8051 MICRO CONTROLLER**

Hardware Architecture, pintouts - Functional Building Blocks of Processor - Memory organization - I/O ports and data transfer concepts- Timing Diagram - Interrupts-Comparison to Programming concepts with 8085.

# **UNIT IV PERIPHERAL INTERFACING**

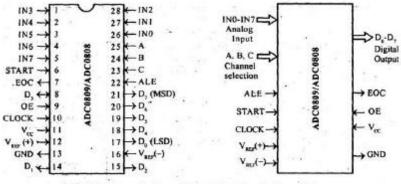

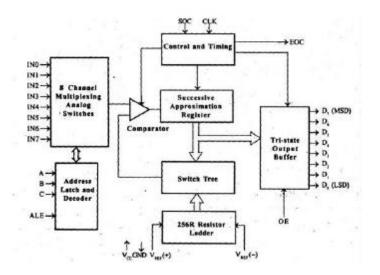

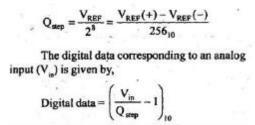

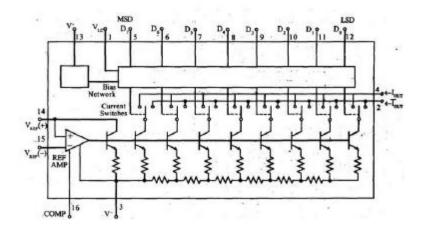

Study on need, Architecture, configuration and interfacing, with ICs: 8255, 8259, 8254, 8237, 8251, 8279, - A/D and D/A converters &Interfacing with 8085& 8051.

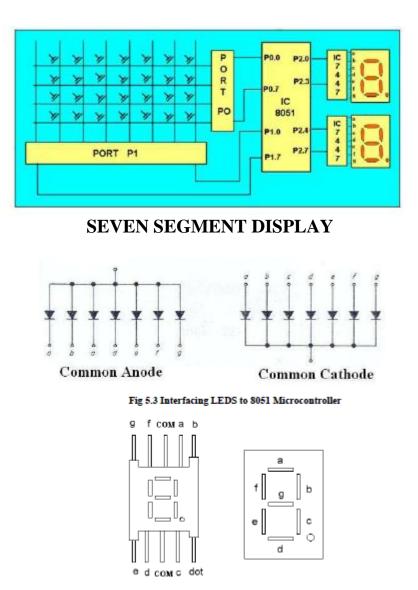

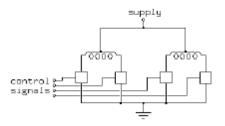

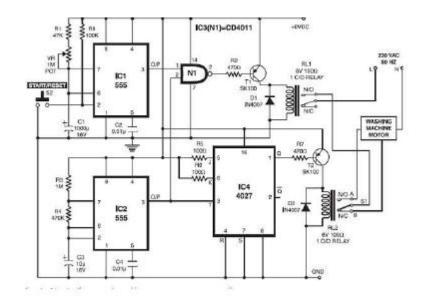

**UNIT V MICRO CONTROLLER PROGRAMMING & APPLICATIONS** Data Transfer, Manipulation, Control Algorithms & I/O instructions – Simple programming exercises key board and display interface - Closed loop control of servo motor- stepper motor control - Washing Machine Control. **TOTAL : 45 PERIODS**

# **OUTCOMES:**

- Ability to understand and analyse, linear and digital electronic circuits.

- To understand and apply computing platform and software for engineering problems.

# **TEXT BOOKS:**

1. Krishna Kant, "Microprocessor and Microcontrollers", Eastern Company Edition, Prentice Hall of India, New Delhi, 2007.

2. R.S. Gaonkar, 'Microprocessor Architecture Programming and Application', with 8085, Wiley Eastern Ltd., New Delhi, 2013.

3. Soumitra Kumar Mandal, Microprocessor & Microcontroller Architecture, Programming & Interfacing using 8085,8086,8051,McGraw Hill Edu,2013.

# **REFERENCES:**

1. Muhammad Ali Mazidi & Janice Gilli Mazidi, R.D.Kinely 'The 8051 Micro Controller and Embedded Systems', PHI Pearson Education, 5th Indian reprint, 2003.

2. N.Senthil Kumar, M.Saravanan, S.Jeevananthan, 'Microprocessors and Microcontrollers', Oxford,2013.

3. Valder - Perez, "Microcontroller - Fundamentals and Applications with Pic," Yeesdee Publishers, Tayler & Francis, 2013.

9

9

#### UNIT I

#### 8085 PROCESSOR

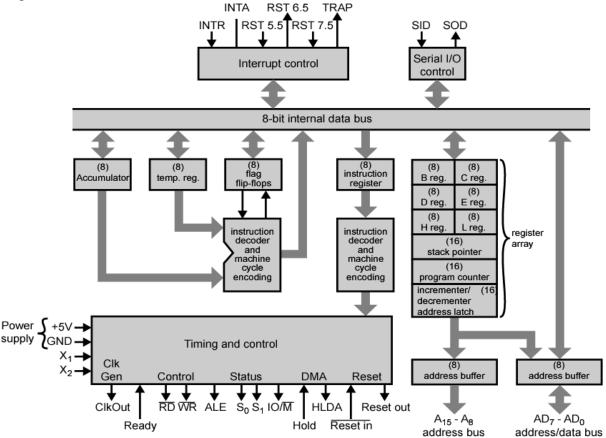

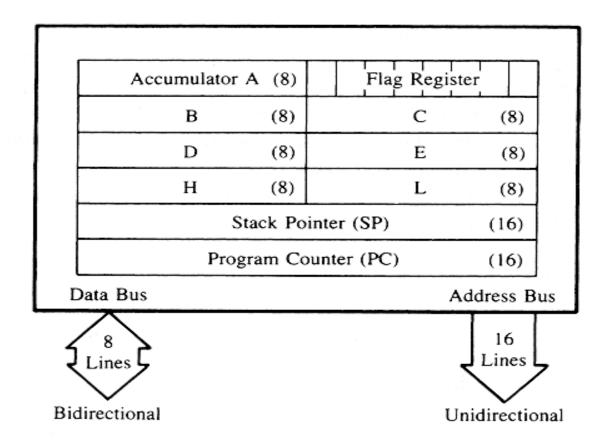

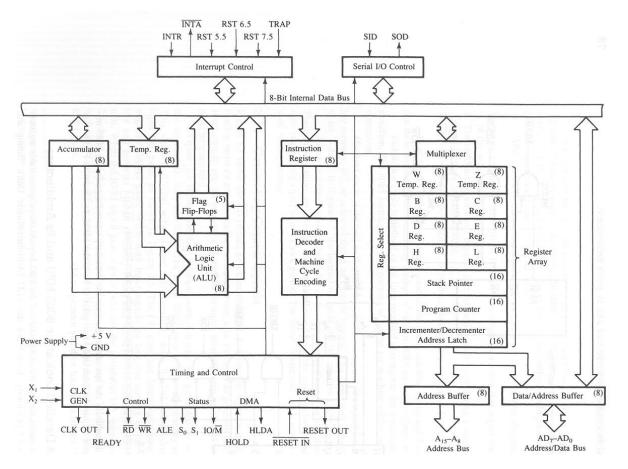

## 1) 8085 Architecture:

The architecture of 8085 consist various components like:

- 1. Accumulator & Register sets.

- 2. Program counter and stack pointer.

- 3. Flag Register.

- 4. ALU.

- 5. Instruction decoder and machine cycle encoder.

- 6. Address buffer.

- 7. Address/data buffer.

- 8. Increment/Decrement latch.

- 9. Interrupt control.

- 10. Serial I/O like SOD,SID.

- 11. Timing and Control circuit.

#### Accumulator:

- The accumulator is an 8-bit register then is part of the arithmetic/logic unit(ALU).

- This register is used to store to store 8-bit data this data is used to perform arithmetic & logical operation.

- The result of an operation is stored in the accumulator.

- The accumulator is also identified as register A.

- The accumulator is used for data transfer between an I/O port and memory location.

#### **Registersets:**

- The 8085 simulator has <u>six general-purpose registers</u> to store 8-bit data; these are identified as B, C, D, E, H and L. They can be combined as register pair likeBC, DE and HL to perform some 16-bit operations.

- The programmer can use these registers to store or copy data into the registers by using data copy instructions.

- Out of these six registers, four 8-bit registers are scratch pad registers which are accessible to the programmer and hence can be used to temporarily store data during a program execution.

- And the two registers **H** and **L** are utilized in indirect addressing mode. In this mode, the memory location i.e. the address is specified by the contents of the registers.

# **Program Counter (PC):**

- 16 bit register which holds the memory address of the next instruction to be executed in the next step.

- This 16-bit register deals with sequencing the execution of instructions. This register is a memory pointer. Memory locations have 16-bit addresses, and that is why this is a 16-bit register.

- The microprocessor uses this register to sequence the execution of the instructions. <u>The function of the program counter is to point to the memory address from which the next instruction is to be fetched.</u> When a byte (machine code) is being fetched, the program counter is incremented by one to point to the next memory location.

## **Stack Pointer (SP):**

- Stack pointer is used during subroutine calling and execution.

- The stack pointer is also a 16-bit register used as a memory pointer. It points to a memory location in R/W memory, called the stack.

#### Flag or status register:

- The ALU includes five flip-flops, which are set or reset after an operation according to data conditions of the result in the accumulator and other registers. They are called Zero(Z), Carry (CY), Sign (S), Parity (P), and Auxiliary Carry (AC) flags.

- The most commonly used flags are Zero, Carry, and Sign. The microprocessor uses these flags to test data conditions.

- For example, after an addition of two numbers, if the sum in the accumulator is larger than eight bits, the flip-flop uses to indicate a carry -- called the Carry flag (CY) -- is set to one.

- When an arithmetic operation results is zero, the flip-flop called the Zero(Z) flag is set to one.

- The Figure shows an 8-bit register, called the flag register, adjacent to the accumulator..

| D <sub>7</sub> | $D_6$ | $D_5$ | $D_4$ | $D_3$ | $D_2$ | D <sub>1</sub> | $D_{o}$ |  |

|----------------|-------|-------|-------|-------|-------|----------------|---------|--|

| S              | Z     |       | AC    |       | Р     |                | CY      |  |

Bit positions of various flags in the flag register of 8085

• **Flag** is an 8-bit register containing 5no.s of 1-bit flags:

1. Sign - If the result of the latest arithmetic operation is having MSB (most- significant bit) '1' (meaning it is a negative number), then the sign flag is set. Otherwise, it is reset to '0' which means it is a positive number.

- 2. Zero If the result of the latest operation is zero, then zero flag will be set; otherwise it be reset.

- 3. Auxiliary carry set if there was a carry out from bit 3 to bit 4 of the result.

4. Parity - set if the parity (the number of set bits in the result) is even. i.e., If the result of the latest operation is having even number of '1's, then this flag will be set. Otherwise this will be reset to '0'. This is used for error checking.

5. Carry - set if there was a carry during addition, or borrow during subtraction/comparison. Otherwise it will be reset.

# Instruction register or Decoder:-

- Instruction register holds the instruction that is currently being processed.

- Once the instruction is fetch from the memory, it is reloaded in the instruction register for some time, after the decoder decode the instruction performing some event or task.

# Address buffer:

• The remaining higher order address lines form the address buffer ranging from[A15-A8]. This is having the unidirectional buffer

# Address/data buffer:

• The address bus will be having 16 address lines[A15-A0] .In which A7-A0 are called as lower addressing lines and these are multiplexed with data lines[D7-D0] to form multiplexed address /data buffer .The address/data buffer is the bidirectional bus.

#### **Increment/Decrement Address Latch:**

• It increments/ decrements the address before sent to the address buffer

#### **Interrupts:**

The processor has 5 interrupts. They are presented below in the order of their priority (from lowest to highest):

- **INTR** is maskable 8080A compatible interrupt. When the interrupt occurs, the processor fetches from the bus one instruction, usually one of these instructions: One of the 8 RST instructions (RST0 RST7). The processor saves current program counter into stack and branches to memory location N \* 8 (where N is a 3-bit number from 0 to 7 supplied with the RST instruction).

- CALL instruction (3 byte instruction). The processor calls the subroutine, address of which is specified in the second and third bytes of the instruction.

- **RST5.5** is a maskable interrupt. When this interrupt is received the processor saves the contents of the PC register into stack and branches to 2CH (hexadecimal) address.

- **RST6.5** is a maskable interrupt. When this interrupt is received the processor saves the contents of the PC register into stack and branches to 34H (hexadecimal) address.

- **RST7.5** is a maskable interrupt. When this interrupt is received the processor saves the contents of the PC register into stack and branches to 3CH (hexadecimal) address.

- **TRAP** is a non-maskable interrupt. When this interrupt is received the processorsaves the contents of the PC register into stack and branches to 24H (hexadecimal) address.

- All maskable interrupts can be enabled or disabled using EI and DI instructions. RST 5.5, RST6.5 and RST7.5 interrupts can be enabled or disabled individually using SIM Instruction

# Serial I/O control

- There are control signals used for controlling 8085 these are subdivided into 2 types:

- 1. SID(serial input data):

This is used for transferring of data into the memory serially.

- 2. SOD(serial output data): This is used for transferring of data from memory to external devices

- Interrupt control is used to transfer the ISR to the CPU.

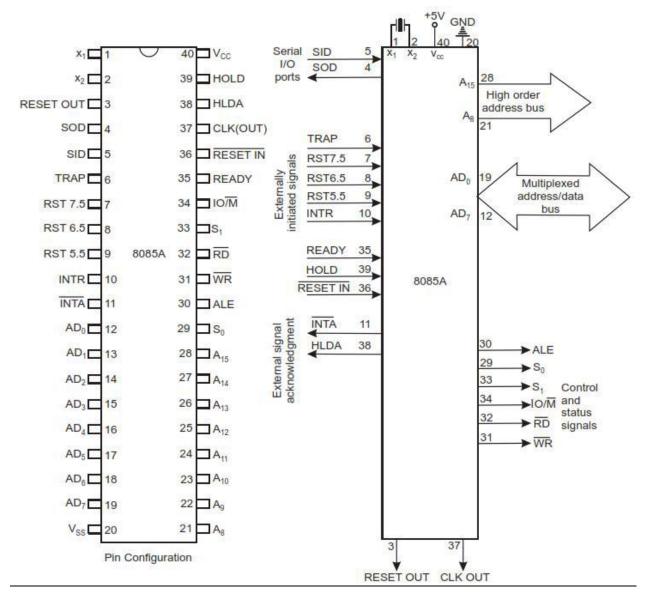

# 2) <u>PIN DIAGRAM</u>

# **Timing and Control Unit:**

• The timing and control unit accepts information from the instruction decoder andgenerates different control signal. This unit synchronizes all the microprocessor operation and generates control and status signal necessary for communication between the microprocessor and peripherals.

# A8 - A15 (Output 3 State):

Address Bus: The most significant 8 bits of the memory address or the 8 bits of the I/0 address,3 stated during Hold and Halt modes.

# AD0 - AD7 (Input / Output 3 state):

- ✓ Multiplexed Address/Data Bus; Lower 8 bits of the memory address (or I/0 address) appear on the bus during the first clock cycle of a machine state.

- ✓ It then becomes the data bus during the second and third clock cycles. 3 stated during Hold and Halt modes.

# ALE (Output):

- ✓ Address Latch Enable: It occurs during the first clock cycle of a machine state and enables the address to get latched into the on chip latch of peripherals.

- ✓ The falling edge of ALE is set to guarantee setup and hold times for the address information. ALE can also be used to strobe the status information. ALE is never 3stated.

# SO, S1 (Output):

Data Bus Status. Encoded status of the bus cycle:

- S1 S0

- 00 HALT

- 01 WRITE

- 10 READ

- 1 1 FETCH S1 can be used as an advanced R/W status.

# RD (Output 3state):

READ: indicates the selected memory or I/0 device is to be read and that the Data Bus is available for the data transfer.

# WR (Output 3state):

- ✓ WRITE: indicates the data on the Data Bus is to be written into the selected memory or I/Olocation.

- $\checkmark$  Data is set up at the trailing edge of WR. 3stated during Hold and Halt modes.

# **READY** (Input):

- ✓ If Ready is high during a read or write cycle, it indicates that the memory or peripheral is readyto send or receive data.

- ✓ If Ready is low, the CPU will wait for Ready to go high before completing the read or write cycle.

# HOLD (Input):

- ✓ HOLD: indicates that another Master is requesting the use of the Address and Data Buses.

- ✓ The CPU, upon receiving the Hold request will relinquish the use of buses as soon as the completion of the current machine cycle.

- ✓ Internal processing can continue. The processor can regain the buses only after the Hold is removed. When the Hold is acknowledged, the Address, Data, RD, WR, and IO/M lines are 3stated.

# HLDA (Output):

- ✓ HOLD ACKNOWLEDGE: indicates that the CPU has received the Hold request and that it willrelinquish the buses in the next clock cycle.

- ✓ HLDA goes low after the Hold request is removed. The CPU takes the buses one half clock cycle after HLDA goes low.

# INTR (Input):

- ✓ INTERRUPT REQUEST is used as a general purpose interrupt. It is sampled only during thenext to the last clock cycle of the instruction. If it is active, the Program Counter (PC) will be inhibited from incrementing and an INTA will be issued.

- ✓ During this cycle a RESTART or CALL instruction can be inserted to jump to the interrupt service routine. The INTR is enabled and disabled by software. It is disabled by Reset and immediately after an interrupt is accepted.

# INTA (Output):

- ✓ INTERRUPT ACKNOWLEDGE: is used instead of (and has the same timing as) RD during theInstruction cycle after an INTR is accepted.

- ✓ It can be used to activate the 8259 Interrupt chip or some other interrupt port.

# **RESTART INTERRUPTS:**

These three inputs have the same timing as INTR except they cause an internal RESTART to be automatically inserted.

- ▶ RST 7.5 Highest Priority

- ▶ RST 6.5

- RST 5.5 Lowest Priority

# **TRAP** (Input):

✓ Trap interrupt is a non maskable restart interrupt. It is recognized at the same time as INTR. It is unaffected by any mask or Interrupt Enable. It has the highest priority of any interrupt.

# **RESET IN (Input):**

- ✓ Reset sets the Program Counter to zero and resets the Interrupt Enable and HLDA flipflops.

- ✓ None of the other flags or registers (except the instruction register) are affected The CPU is held in the reset condition as long as Reset is applied.

# **RESET OUT (Output):**

Indicates CPIJ is being reset. Can be used as a system RESET. The signal is synchronized to the processor clock.

# X1, X2 (Input):

✓ Crystal or R/C network connections to set the internal clock generator X1 can also be an external clock input instead of a crystal. The input frequency is divided by 2 to give the internal operating frequency.

# CLK (Output):

✓ Clock Output for use as a system clock when a crystal or R/C network is used as an input to the CPU. The period of CLK is twice the X1, X2 input period.

# IO/M (Output):

✓ IO/M indicates whether the Read/Write is to memory or I/O Tristated during Hold and Halt modes.

#### SID (Input):

✓ Serial input data line The data on this line is loaded into accumulator bit 7 whenever a RIM instruction is executed.

## **SOD** (output):

✓ Serial output data line. The output SOD is set or reset as specified by the SIM instruction.

Vcc: +5 volt supply. Vss: Ground Reference.

#### 3) MEMORY ORGANIZATION

#### **Memory Interfacing**

The memory is made up of semiconductor material used to store the programs and data. Three types of memory is,

- □ Process memory

- □ Primary or main memory

- □ Secondary memory

# **Typical EPROM and Static RAM**

A typical semiconductor memory IC will have n address pins, m data pins (or output pins).

- □ Having two power supply pins (one for connecting required supply voltage (V and the other for connecting ground).

- □ The control signals needed for static RAM are chip select (chip enable), read control

(output enable) and write control (write enable).

□ The control signals needed for read operation in EPROM are chip select (chip enable) and read control (output enable).

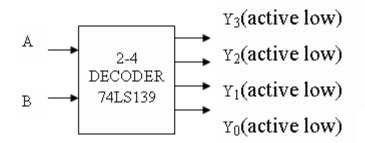

# Decoder

It is used to select the memory chip of processor during the execution of a program. No

of IC's used for decoder is,

- $\Box \quad 2-4 \text{ decoder (74LS139)}$

- □ 3-8 decoder (74LS138)

**Block Diagram of 2-4 Decoder**

#### **Truth Table for 2-4 Decoder**

| toput |    | Output |     |    |    |  |

|-------|----|--------|-----|----|----|--|

| в     | A  | Ŷ,     | Ŧ,  | Ŧ, | Ÿ, |  |

| 0     | 0  | 1      | - 1 | 1  | 0  |  |

| 0     | 1  | 1      | 1   | 0  | 1  |  |

| 1     | 0  | 1      | 0   | 1  | I  |  |

| 1     | .1 | 0      | 1   | 1  | 1  |  |

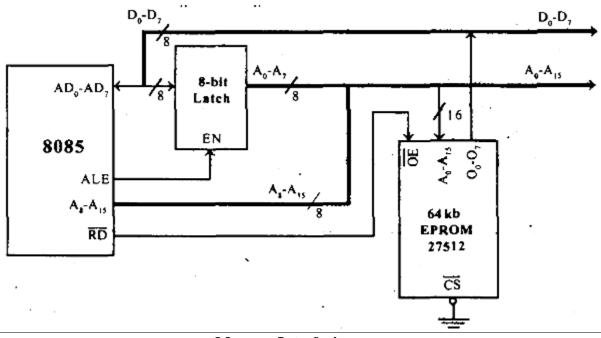

#### **Example for Memory Interfacing**

Consider a system in which the full memory space 64kb is utilized for EPROM memory. Interface the EPROM with 8085 processor.

- □ The memory capacity is 64 Kbytes. i.e

- $\Box$  2^n = 64 x 1000 bytes where n = address lines.

- $\Box \quad \text{So, } n = 16.$

- □ In this system the entire 16 address lines of the processor are connected to address input pins of memory IC in order to address the internal locations of memory.

- □ The chip select (CS) pin of EPROM is permanently tied to logic low (i.e., tied to ground).

- □ Since the processor is connected to EPROM, the active low RD pin is connected to active low output enable pin of EPROM.

- □ The range of address for EPROM is 0000H to FFFFH.

**Memory Interfacing**

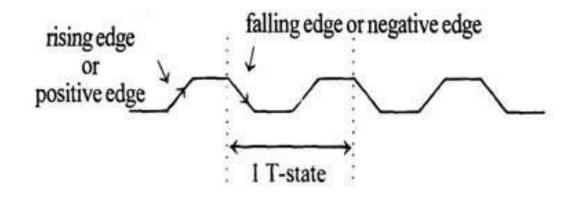

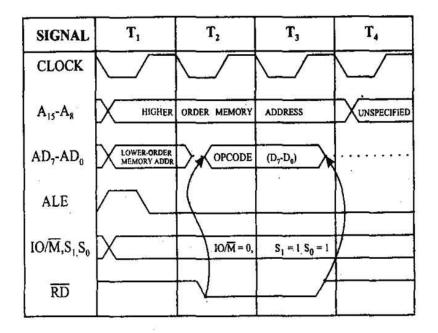

#### 4) **<u>TIMING DIAGRAM</u>**

Timing Diagram is a graphical representation. It represents the execution time taken by each instruction in a graphical format. The execution time is represented in T-states.

#### □ Instruction Cycle

The time required to execute an instruction is called instruction cycle.

#### □ Machine Cycle

The time required to access the memory or input/output devices is called machine cycle.

#### **T-State**

- $\Box$  The machine cycle and instruction cycle takes multiple clock periods.

- □ A portion of an operation carried out in one system clock period is called as T-state.

#### Machine cycles of 8085

The 8085 microprocessor has 5 (seven) basic machine cycles. They are

1. Opcode fetch cycle (4T)

- 2. Memory read cycle (3 T)

- 3. Memory write cycle (3 T)

- 4. I/O read cycle (3 T)

- 5. I/O write cycle (3 T)

# Time period, T = 1/f; where $f = Internal \ clock \ frequency$

#### 1.Opcode fetch machine cycle of 8085 :

- $\Box$  Each instruction of the processor has one byte opcode.

- □ The opcodes are stored in memory. So, the processor executes the opcode fetch machine cycle to fetch the opcode from memory.

- $\Box$  Hence, every instruction starts with opcode fetch machine cycle.

- $\Box$  The time taken by the processor to execute the opcode fetch cycle is 4T.

- □ In this time, the first, 3 T-states are used for fetching the opcode from memory and the remaining T-states are used for internal operations by the processor.

# 2.Memory Read Machine Cycle of 8085:

- □ The memory read machine cycle is executed by the processor to read a data byte from memory.

- $\Box$  The processor takes 3T states to execute this cycle.

The instructions which have more than one byte word size will use the machine cycle after the opcode fetch machine cycle.

| SIGNAL                                       | T <sub>1</sub>             | T <sub>2</sub>                         | Т,                                |

|----------------------------------------------|----------------------------|----------------------------------------|-----------------------------------|

| CLOCK                                        |                            |                                        |                                   |

| A <sub>15</sub> -A <sub>8</sub>              | HIGHER                     | ORDER MEMORY                           | ADDRESS                           |

| AD <sub>7</sub> -AD <sub>0</sub>             | LOWER-ORDER<br>MEMORY ADDR | DATA                                   | (D <sub>7</sub> -D <sub>0</sub> ) |

| ALE                                          | <hr/>                      |                                        |                                   |

| IO/ <b>M</b> ,S <sub>1.</sub> S <sub>0</sub> | ×                          | $10/\overline{M} = 0, \qquad S_1 = 1.$ | S <sub>0</sub> = 0                |

| RD                                           |                            | +\                                     | Ļ/                                |

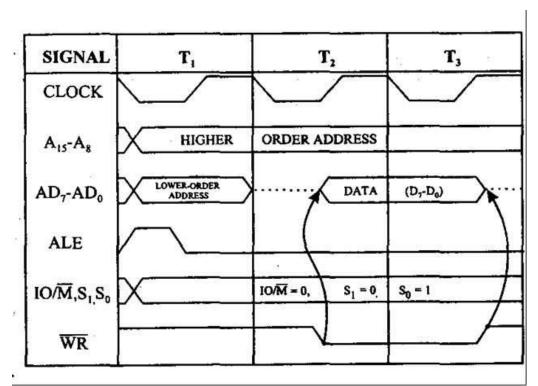

# 3.Memory Write Machine Cycle of 8085

- □ The memory write machine cycle is executed by the processor to write a data byte in a memory location.

- $\Box$  The processor takes, 3T states to execute this machine cycle.

Memory Write Machine Cycle

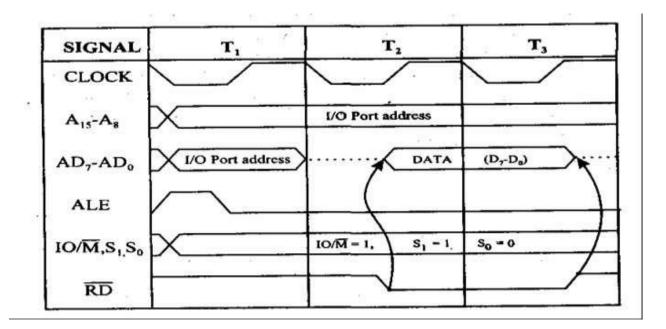

# 4. I/O Read Cycle of 8085

- □ The I/O Read cycle is executed by the processor to read a data byte from I/O port or from the peripheral, which is I/O, mapped in the system.

- $\Box$  The processor takes 3T states to execute this machine cycle.

- $\Box$  The IN instruction uses this machine cycle during the execution.

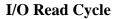

#### **Timing diagram for STA 526AH**

- □ STA means Store Accumulator -The contents of the accumulator is stored in the specified address(526A).

- $\Box$  The opcode of the STA instruction is said to be 32H. It is fetched from the memory

41FFH(see fig). - OF machine cycle

- □ Then the lower order memory address is read(6A). Memory Read Machine Cycle

- □ Read the higher order memory address (52).- Memory Read Machine Cycle

- □ The combination of both the addresses are considered and the content from accumulator is written in 526A. Memory Write Machine Cycle

- $\Box$  Assume the memory address for the instruction and let the content of accumulator is

C7H. So, C7H from accumulator is now stored in 526A.

Timing Diagram for STA 526A H

# Timing diagram for INR M

- □ Fetching the Opcode 34H from the memory 4105H. (OF cycle)

- □ Let the memory address (M) be 4250H. (MR cycle -To read Memory address and data)

- $\Box$  Let the content of that memory is 12H.

- □ Increment the memory content from 12H to 13H. (MW machine cycle)

## 5) **INTERRUPTS:**

- □ Interrupt is signals send by an external device to the processor, to request the processor to perform a particular task or work.

- □ Mainly in the microprocessor based system the interrupts are used for data transfer between the peripheral and the microprocessor.

$\hfill\square$  The processor will check the interrupts always at the 2nd T-state of last machine cycle.

- □ If there is any interrupt it accept the interrupt and send the INTA (active low) signal to the peripheral.

- $\Box$  The vectored address of particular interrupt is stored in program counter.

$\hfill\square$  The processor executes an interrupt service routine (ISR) addressed in program counter.

□ It returned to main program by RET instruction.

#### **Types of Interrupts:**

It supports two types of interrupts.

- □ Hardware

- □ Software

#### Software interrupts:

- □ The software interrupts are program instructions. These instructions are inserted at desired locations in a program.

- □ The 8085 has eight software interrupts from RST 0 to RST 7. The vector address for these interrupts can be calculated as follows.

- $\Box$  Interrupt number \* 8 = vector address

$\Box$  For RST 5,5 \* 8 = 40 = 28H

#### Vector addresses of all interrupts.

| Interrupt | Vector address    |

|-----------|-------------------|

| RST 0     | 0000 <sub>H</sub> |

| RST 1     | 0008 <sub>H</sub> |

| RST 2     | 0010 <sub>H</sub> |

| RST 3     | 0018 <sub>H</sub> |

| RST 4     | 0020 <sub>H</sub> |

| RST 5     | 0028 <sub>H</sub> |

| RST 6     | 0030 <sub>H</sub> |

| RST 7     | 0038 <sub>H</sub> |

#### Hardware interrupts:

□ An external device initiates the hardware interrupts and placing an appropriate signal at the interrupt pin of the processor.

$\hfill\square$  If the interrupt is accepted then the processor executes an interrupt service routine.

The 8085 has five hardware interrupts

| (1) TRAP | (2) RST 7.5 | (3) RST 6.5 | (4) RST 5.5      | (5) INTR |

|----------|-------------|-------------|------------------|----------|

| (-)      | (-)         | (-)         | ( ) = == = = = = | (-)      |

#### (1)**TRAP**:

- □ This interrupt is a non-maskable interrupt. It is unaffected by any mask or interrupt enable.

- □ TRAP bas the highest priority and vectored interrupt.

- □ TRAP interrupt is edge and level triggered. This means hat the TRAP must go high and remain high until it is acknowledged.

- □ In sudden power failure, it executes a ISR and send the data from main memory to backup memory.

- □ The signal, which overrides the TRAP, is HOLD signal. (i.e., If the processor receives HOLD and TRAP at the same time then HOLD is recognized first and then TRAP is recognized).

- □ There are two ways to clear TRAP interrupt.

1.By resetting microprocessor (External signal)

2.By giving a high TRAP ACKNOWLEDGE (Internal signal)

#### (2)RST 7.5:

- □ The RST 7.5 interrupt is a maskable interrupt.

- $\Box$  It has the second highest priority.

- □ It is edge sensitive. ie. Input goes to high and no need to maintain high state until it recognized.

- $\Box$  Maskable interrupt. It is disabled by,

- 1.DI instruction

2.System or processor reset.

3.After reorganization of interrupt.

- $\Box$  Enabled by EI instruction.

#### (3)RST 6.5 and 5.5:

- □ The RST 6.5 and RST 5.5 both are level triggered. . ie. Input goes to high and stay high until it recognized.

- $\Box$  Maskable interrupt. It is disabled by,

#### 1.DI, SIM instruction

2.System or processor reset.

3. After reorganization of interrupt.

- $\Box$  Enabled by EI instruction.

- □ The RST 6.5 has the third priority whereas RST 5.5 has the fourth priority.

- □ INTR is a maskable interrupt. It is disabled by,

1.DI, SIM instruction2.System or processor reset.3.After reorganization of interrupt

- $\Box$  Enabled by EI instruction.

- □ Non-vectored interrupt. After receiving INTA (active low) signal, it has to supply the address of ISR.

- $\Box$  It has lowest priority.

- □ It is a level sensitive interrupts. ie. Input goes to high and it is necessary to maintain high state until it recognized.

The following sequence of events occurs when INTR signal goes high.

1. The 8085 checks the status of INTR signal during execution of each instruction.

2. If INTR signal is high, then 8085 complete its current instruction and sends active low interrupt acknowledge signal, if the interrupt is enabled.

3. In response to the acknowledge signal, external logic places an instruction OPCODE on the data bus. In the case of multibyte instruction, additional interrupt acknowledge machine cycles are generated by the 8085 to transfer the additional bytes into the microprocessor.

4. On receiving the instruction, the 8085 save the address of next instruction on

stack and execute received instruction.

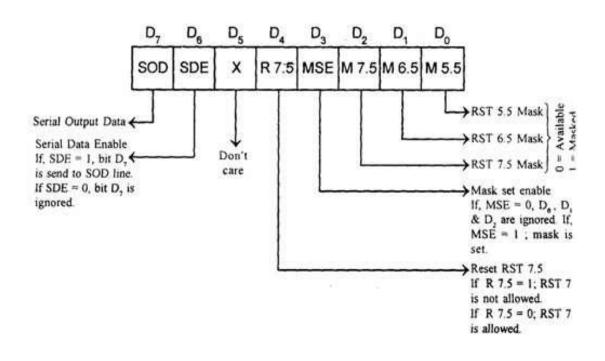

#### SIM and RIM for interrupts:

□ The 8085 provide additional masking facility for RST 7.5, RST 6.5 and RST 5.5 using

SIM instruction.

- $\Box$  The status of these interrupts can be read by executing RIM instruction.

- □ The masking or unmasking of RST 7.5, RST 6.5 and RST 5.5 interrupts can be performed by moving an 8-bit data to accumulator and then executing SIM instruction.

8 bit data to be loaded into the Accumulator

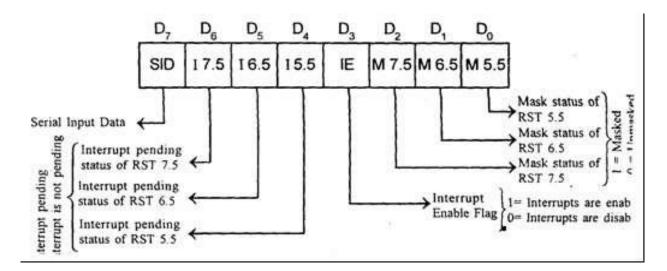

$\hfill\square$  The status of pending interrupts can be read from accumulator after executing RIM instruction.

□ When RIM instruction is executed an 8-bit data is loaded in accumulator, which can be interpreted as shown in fig.

# Format of 8 bit data in Accumulator after executing RIM Instruction

#### 8085 Bus Structure

#### • Address Bus :

- Consists of 16 address lines: A0 A15

- Address locations: 0000 (hex) FFFF (hex)

- Can access 64K (= 216) bytes of memory, each byte has 8 bits

- Can access  $64K \times 8$  bits of memory

- Use memory to map I/O, Same instructions to use for

- accessing I/O devices and memory

#### • Data Bus :

- Consists of 8 data lines: D0 D7

- Operates in bidirectional mode

- The data bits are sent from the MPU to I/O & vice versa

- Data range: 00 (hex) FF (hex)

#### • Control Bus:

Consists of various lines carrying the control signals such as read / write enable, flag bits.

#### UNIT II

#### PROGRAMMING OF 8085 MICROPROCESSOR

#### **1)INSTRUCTION FORMAT**

An **instruction** is a command to the microprocessor to perform a given task on a specified data. Each instruction has two parts: one is task to be performed, called the **operation code** (opcode), and the second is the data to be operated on, called the **operand.** The operand (or data) can be specified in various ways. It may include 8-bit (or 16-bit ) data, an internal register, a memory location, or 8-bit (or 16-bit) address. In some instructions, the operand is implicit.

#### **Instruction word size**

The 8085 instruction set is classified into the following three groups according to word size:

**1.** One-word or 1-byte instructions

- **2.** Two-word or 2-byte instructions

- **3.** Three-word or 3-byte instructions

In the 8085, "byte" and "word" are synonymous because it is an 8-bit microprocessor. However, instructions are commonly referred to in terms of bytes rather than words.

#### **2.1.1 One-Byte Instructions**

A 1-byte instruction includes the opcode and operand in the same byte. Operand(s) are internal register and are coded into the instruction

| Task                                                               | Op<br>code | Operand | Binary<br>Code | Hex<br>Code |

|--------------------------------------------------------------------|------------|---------|----------------|-------------|

| Copy the contents of the accumulator in the register C.            | MOV        | C,A     | 0100 1111      | 4FH         |

| Add the contents of register B to the contents of the accumulator. | ADD        | В       | 1000 0000      | 80H         |

| Invert (compliment) each bit in the accumulator.                   | CMA        |         | 0010 1111      | 2FH         |

These instructions are 1-byte instructions performing three different tasks. In the first instruction, both operand registers are specified. In the second instruction, the operand B is specified and the accumulator is assumed. Similarly, in the third instruction, the accumulator is assumed to be the implicit operand. These instructions are stored in 8-bit binary format in memory; each requires one memory location.

# MOV rd, rs

rd <-- rs copies contents of rs into rd.

Coded as 01 ddd sss where ddd is a code for one of the 7 general registers which is

the destination of the data, sss is the code of the source register.

Example: MOV A,B

Coded as 01111000 = 78H = 170 octal (octal was used extensively in instruction

design of such processors).

# ADD r

A <-- A + r

# **Two-Byte Instructions**

In a two-byte instruction, the first byte specifies the operation code and the second byte specifies the operand. Source operand is a data byte immediately following the opcode. For example

| Task                                              | Opcode | Operand | Binary<br>Code | Hex Code   |                           |

|---------------------------------------------------|--------|---------|----------------|------------|---------------------------|

| Load an 8-bit data<br>byte in the<br>accumulator. | MVI    | A, Data | 0011 1110      | 3E<br>Data | First Byte<br>Second Byte |

|                                                   |        |         | DATA           |            | -                         |

The instruction would require two memory locations to store in memory. **MVI r,data**

# r <-- data

Example: MVI A,30H coded as 3EH 30H as two contiguous bytes. This is an example of immediate addressing.

# ADI data

A <--- A + data OUT port 0011 1110 DATA

where port is an 8-bit device address. (Port) <-- A. Since the byte is not the data but points directly to where it is located this is called direct addressing.

# **Three-Byte Instructions**

In a three-byte instruction, the first byte specifies the opcode, and the following two bytes specify the 16-bit address. Note that the second byte is the low-order address and the third byte is the high-order address.

opcode + data byte + data byte

| Task         | Opcode | Operand | Binary code | Hex Code |             |

|--------------|--------|---------|-------------|----------|-------------|

| Transfer the | JMP    | 2085H   |             | C3       | First byte  |

| program      |        |         | 1100 0011   |          |             |

| sequence to  |        |         | 1000 0101   | 85       | Second Byte |

| the memory   |        |         | 1000 0101   |          |             |

| location     |        |         | 0010 0000   | 20       | Third Byte  |

| 2085H.       |        |         |             |          | -           |

This instruction would require three memory locations to store in memory.

Three byte instructions - opcode + data byte + data byte

# LXI rp, data16

rp is one of the pairs of registers BC, DE, HL used as 16-bit registers. The two data

bytes are 16-bit data in L H order of significance.

rp <-- data16

LXI H,0520H coded as 21H 20H 50H in three bytes. This is also immediate

addressing.

# LDA addr

A <-- (addr) Addr is a 16-bit address in L H order.

Example: LDA 2134H coded as

3AH 34H 21H. This is also an example of direct addressing.

# 2) THE 8085 ADDRESSING MODES

The instructions MOV B, A or MVI A, 82H are to copy data from a source into a destination. In these instructions the source can be a register, an input port, or an 8-bit number (00H to FFH). Similarly, a destination can be a register or an output port. The sources and destination are operands. The various formats for specifying operands are called the ADDRESSING MODES. For 8085, they are:

- 1. Immediate addressing.

- 2. Register addressing.

- 3. Direct addressing.

- 4. Indirect addressing.

# (1)Immediate addressing

Data is present in the instruction. Load the immediate data to the destination provided.

Example: MVI R,data

## (2)Register addressing

Data is provided through the registers.

Example: MOV Rd, Rs

#### (3)Direct addressing

Used to accept data from outside devices to store in the accumulator or send the data

stored in the accumulator to the outside device. Accept the data from the port 00H and

store them into the accumulator or Send the data from the accumulator to the port

01H.

# **Example:** IN 00H or OUT 01H

#### (4)Indirect Addressing

This means that the Effective Address is calculated by the processor. And the contents of the address (and the one following) is used to form a second address. The second address is where the data is stored. Note that this requires several memory accesses; two accesses to retrieve the 16-bit address and a further access (or accesses) to retrieve the data which is to be loaded into the register.

# 3) INSTRUCTION SET CLASSIFICATION

An **instruction** is a binary pattern designed inside a microprocessor to perform a specific function. The entire group of instructions, called the **instruction set**, determines what functions the microprocessor can perform. These instructions can be classified into the following five functional categories: data transfer (copy) operations, arithmetic operations, logical operations, branching operations, and machine-control operations.

#### **Data Transfer Croup**

The data transfer instructions move data between registers or between memory and registers.

MOV Move

MVI Move Immediate

LDA Load Accumulator Directly from Memory

STA Store Accumulator Directly in Memory

LHLD Load H & L Registers Directly from Memory

SHLD Store H & L Registers Directly in Memory

An 'X' in the name of a data transfer instruction implies that it deals with a register pair (16-bits);

LXI Load Register Pair with Immediate data

LDAX Load Accumulator from Address in Register Pair

STAX Store Accumulator in Address in Register Pair

XCHG Exchange H & L with D & E

XTHL Exchange Top of Stack with H & L

#### **Arithmetic Group**

The arithmetic instructions add, subtract, increment, or decrement data in registers or memory.

ADD Add to Accumulator

ADI Add Immediate Data to Accumulator

ADC Add to Accumulator Using Carry Flag

ACI Add Immediate data to Accumulator Using Carry

SUB Subtract from Accumulator

SUI Subtract Immediate Data from Accumulator

SBB Subtract from Accumulator Using Borrow (Carry) Flag

SBI Subtract Immediate from Accumulator Using Borrow (Carry) Flag

INR Increment Specified Byte by One

DCR Decrement Specified Byte by One

INX Increment Register Pair by One

DCX Decrement Register Pair by One

DAD Double Register Add; Add Content of Register

Pair to H & L Register Pair

#### **Logical Group**

This group performs logical (Boolean) operations on data in registers and memory and on

condition flags.

The logical AND, OR, and Exclusive OR instructions enable you to set specific bits in the

accumulator ON or OFF.

ANA Logical AND with Accumulator

ANI Logical AND with Accumulator Using Immediate Data

ORA Logical OR with Accumulator

OR Logical OR with Accumulator Using Immediate Data

XRA Exclusive Logical OR with Accumulator

XRI Exclusive OR Using Immediate Data

The Compare instructions compare the content of an 8-bit value with the contents of the

accumulator;

**CMP** Compare

CPI Compare Using Immediate Data

The rotate instructions shift the contents of the accumulator one bit position to the left or right:

RLC Rotate Accumulator Left

**RRC** Rotate Accumulator Right

RAL Rotate Left Through Carry

RAR Rotate Right Through Carry

Complement and carry flag instructions:

CMA Complement Accumulator

CMC Complement Carry Flag

STC Set Carry Flag

#### **Branch Group**

The branching instructions alter normal sequential program flow, either unconditionally or

conditionally. The unconditional branching instructions are as follows:

JMP Jump

CALL Call

**RET Return**

Conditional branching instructions examine the status of one of four condition flags to determine

whether the specified branch is to be executed. The conditions that may be specified are as

follows:

NZ Not Zero (Z = 0)

Z Zero (Z = 1)

NC No Carry (C = 0)

C Carry (C = 1)

PO Parity Odd (P = 0)

PE Parity Even (P = 1)

P Plus (S = 0)

M Minus (S = 1)

Thus, the conditional branching instructions are specified as follows:

Jumps Calls Returns

C CC RC (Carry)

INC CNC RNC (No Carry)

JZ CZ RZ (Zero)

JNZ CNZ RNZ (Not Zero)

JP CP RP (Plus)

JM CM RM (Minus)

JPE CPE RPE (Parity Even)

JP0 CPO RPO (Parity Odd)

Two other instructions can affect a branch by replacing the contents or the program counter:

PCHL Move H & L to Program Counter

**RST Special Restart Instruction Used**

with Interrupts

POP Pop Two Bytes of Data off the Stack XTHL Exchange Top of Stack with H & L SPHL Move content of H & L to Stack Pointer **I/0 instructions** IN Initiate Input Operation OUT Initiate Output Operation **Machine Control instructions** EI Enable Interrupt System DI Disable Interrupt System HLT Halt NOP No Operation

#### SAMPLE PROGRAM

(1)Write an assembly program to add two numbers Program MVI D, 8BH MVIC, 6FH MOV A, C 1100 0011 1000 0101 0010 0000 ADD D OUT PORT1 HLT (2)Write an assembly program to multiply a number by 8 Program **MVI A, 30H** RRC RRC RRC **OUT PORT1** HLT (3)Write an assembly program to find greatest between two numbers Program MVIB, 30H MVIC, 40H MOV A, B CMP C JZ EOU JC GRT **OUT PORT1** HLT EQU: MVI A, 01H **OUT PORT1**

HLT GRT: MOV A, C OUT PORT1 HLT 2.5 Programming using Loop structure with Counting and Indexing (i) 16 bit Multiplication ADDRESS LABEL **MNEMONICS** OPCODE **START** L1 L2 LHLD 4200 SPHL LHLD 4202 XCHG LXI H,0000 LXI B,0000 DAD SP JNC L2 INX B DCX D MOV A,E ORA D JNZ L1 SHLD 4204 MOV L,C MOV H,B SHLD 4206 HLT (ii)Finding the maximum number in the given array ADDRESS LABEL **MNEMONICS** OPCODE **START** L2 L3 L1 LDA 4500 MOV C, A LXI H, 4501 MOV A, M DCR C INX H

| 1711                                               |

|----------------------------------------------------|

| JZL1                                               |

| CMP M                                              |

| JC L2                                              |

| JMP L3                                             |

| STA 4520                                           |

| HLT                                                |

| (iii) To sort the array of data in ascending order |

| ADDRESS                                            |

|                                                    |

| LABEL                                              |

| MNEMONICS                                          |

| START                                              |

| L3                                                 |

| L2                                                 |

| L1                                                 |

| MVI B, 00                                          |

| LXI H, 4200                                        |

|                                                    |

| MOV C, M                                           |

| DCR C                                              |

| INX H                                              |

| MOV A, M                                           |

| INX H                                              |

| CMP M                                              |

| JC L1                                              |

| MOV D, M                                           |

| MOV M, A                                           |

| DCX H                                              |

|                                                    |

| MOV M, D                                           |

| INX H                                              |

| MVI B, 01                                          |

| DCR C                                              |

| JNZ L2                                             |

| DCR B                                              |

| JZ L3                                              |

| HLT                                                |

| 2.6 Programming using subroutine Instructions      |

|                                                    |

| Generation of Square waveform using DAC            |

| ADDRESS                                            |

| LABEL                                              |

| MNEMONICS                                          |

| START                                              |

| DELAY                                              |

| L2                                                 |

| L1                                                 |

| MVI A,00H                                          |

| OUT C8                                             |

| CALL DELAY                                         |

| CALL DELA I                                        |

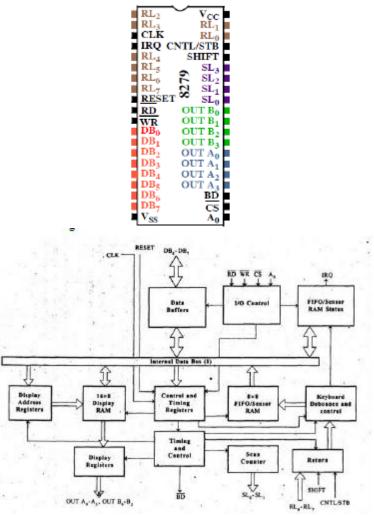

MVI A,FF OUT C8 CALL DELAY JMP START MVI B,05H MVI C,FF DCR C JNZ L1 DCR B JNL L2 RET 2.7 Programming using Look up table ADDRESS LABEL **MNEMONICS** OPCODE **START** L2 **MVI B,08** MVI A,00(DISPLAY MODE SETUP) OUT C2 MVI A,CC(CLEAR DISPLAY) OUT C2 MVI A,90(WRITE DISPLAY RAM) OUT C2 MVI A, FF(CLEAR DISPLAY RAM) OUT C0 DCR B JNZ L1 IN C2 **ANI 07** JZ L2 MVI A, 40(SET TO READ FIFO RAM) OUT C2 IN C0 ANI OF MOV L, A **MVI H, 42** MOV A, M OUT CO JMP L2 LOOKUP TABLE

4200 0C 9F 4A 0B 4204 99 29 28 8F 4208 08 09 88 38 420C 6C 1A 68 E8

# **UNIT III**

# **8051 MICROCONTROLLER**

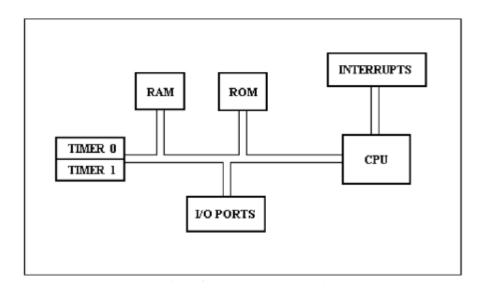

# 1)ARCHITECTURE OF 8051:

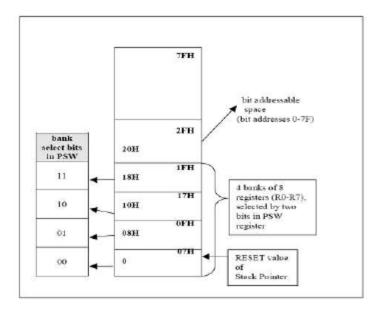

#### **Memory Organization**

- Logical separation of program and data memory -Separate address spaces for Program (ROM) and Data (RAM) Memory

Allow Data Memory to be accessed by 8-bit addresses quickly and manipulated by

8-bit CPU

□ Program Memory

-Only be read, not written to

-The address space is 16-bit, so maximum of 64K bytes

-Up to 4K bytes can be on-chip (internal) of 8051 core

-PSEN (Program Store Enable) is used for access to external Program Memory

□ Data Memory

-Includes 128 bytes of on-chip Data Memory which are more easily accessible

directly by its instructions

-There is also a number of Special Function Registers (SFRs)

-Internal Data Memory contains four banks of eight registers and a special 32byte long segment which is bit addressable by 8051 bit-instructions

-External memory of maximum 64K bytes is accessible by "movx"

# **Interrupt Structure**

- The 8051 provides 4 interrupt sources

- Two external interrupts

- Two timer interrupts

# **Port Structure**

- The 8051 contains four I/O ports

- All four ports are bidirectional

■ Each port has SFR (Special Function Registers P0 through P3) which works like a latch, an output driver and an input buffer

■ Both output driver and input buffer of Port 0 and output driver of Port 2 are used for accessing external memory

■ Accessing external memory works like this

■ Port 0 outputs the low byte of external memory address (which is timemultiplexed with the byte being written or read)

- Port 2 outputs the high byte (only needed when the address is 16 bits wide)

- Port 3 pins are multifunctional

- The alternate functions are activated with the 1 written in the corresponding bit in the port SFR

| Port Pin | Alternate Function                     |  |

|----------|----------------------------------------|--|

| P3.2     | ~INT0 (external interrupt)             |  |

| P3.3     | ~INT1 (external interrupt)             |  |

| P3.4     | T0 (Timer/Counter 0 external input)    |  |

| P3.5     | T1 (Timer/Counter 1 external input)    |  |

| P3.6     | ~WR (external Data Memory writestrobe) |  |

| P3.7     | ~RD (external DataMemory readstrobe)   |  |

#### **Timer/Counter**

- The 8051 has two 16-bit Timer/Counter registers

- Timer 0

- Timer 1

- Both can work either as timers or event counters

- Both have four different operating modes

#### 2) INSTRUCTION FORMAT

An instruction is a command to the microprocessor to perform a given task on a

specified data. Each instruction has two parts: one is task to be performed, called the

operation code (opcode), and the second is the data to be operated on, called the

operand. The operand (or data) can be specified in various ways. It may include 8-bit

(or 16-bit ) data, an internal register, a memory location, or 8-bit (or 16-bit) address. In some instructions, the operand is implicit.

#### **Instruction word size**

The 8051 instruction set is classified into the following three groups according to word size:

- 1. One-word or 1-byte instructions

- **2.** Two-word or 2-byte instructions

- **3.** Three-word or 3-byte instructions

#### **One-Byte Instructions**

A 1-byte instruction includes the opcode and operand in the same byte. Operand(s) are internal register and are coded into the instruction.

These instructions are 1-byte instructions performing three different tasks. In the first instruction, both operand registers are specified. In the second instruction, the operand B is specified and the accumulator is assumed. Similarly, in the third instruction, the accumulator is assumed to be the implicit operand. These instructions are stored in 8-bit binary format in memory; each requires one memory location.

#### **Two-Byte Instructions**

In a two-byte instruction, the first byte specifies the operation code and the second byte specifies the operand. Source operand is a data byte immediately following the opcode.

#### **Three-Byte Instructions**

In a three-byte instruction, the first byte specifies the opcode, and the following two bytes specify the 16-bit address. Note that the second byte is the low-order address and the third byte is the high-order address.

# 3) Addressing Modes of 8051 The 8051 provides a total of five distinct addressing modes. (1) immediate (2) register (3) direct (4) register indirect (5) indexed (1) Immediate Addressing Mode The operand comes immediately after the op-code.

• The immediate data must be preceded by the pound sign, "#".

MOV A,#25H ;load 25H into A MOV R4,#62 ;load the decimal value 62 into R4 MOV B,#40H ;load 40H into B MOV DPTR,#4521H ;DPTR=4512H

#### (2) Register Addressing Mode

• Register addressing mode involves the use of registers to hold the data to be manipulated

MOV A,R0 ;copy the contents of R0 into A MOV R2,A ;copy the contents of A into R2 ADD A,R5 ;add the contents of R5 to contents of A ADD A,R7 ;add the contents of R7 to contents of A MOV R6,A ;save accumulator in R6

#### (3)Direct Addressing Mode

- It is most often used to access RAM locations 30 - 7FH.

-This is due to the fact that register bank locations are accessed by the register names of R0 - R7.

-There is no such name for other RAM locations so must use direct addressing

-In the direct addressing mode, the data is in a RAM memory location whose address is known, and this address is given as a part of the instruction

| MOV | A,4  | ;is same as                 |

|-----|------|-----------------------------|

| MOV | A,R4 | ;which means copy R4 into A |

| MOV | A,7  | ;is same as                 |

| MOV | A,R7 | ;which means copy R7 into A |

#### (4)Register Indirect Addressing Mode

- A register is used as a pointer to the data.

- If the data is inside the CPU, only registers R0 and R 1 are used for this purpose.

- R2 R7 cannot be used to hold the address of an operand located in RAM when using indirect addressing mode.

- When RO and R 1 are used as pointers they must be preceded by the @ sign.

## (5) Indexed Addressing Mode

- Indexed addressing mode is widely used in accessing data elements of look-up table entries located in the program ROM space of the 8051.

- The instruction used for this purpose is :

- MOVC A, @ A+DPTR

- The 16-bit register DPTR and register A are used to form the address of the data element stored in on-chip ROM.

- Because the data elements are stored in the program (code) space ROM of the 8051, the instruction MOVC is used instead of MOV. The "C" means code.

- In this instruction the contents of A are added to the 16-bit register DPTR to form the 16-bit address of the needed data

# 4) Interrupt Structure

- 8051 provides 4 interrupt sources

- 2 external interrupts

- 2 timer interrupts

- They are controlled via two SFRs, IE and IP

■ Each interrupt source can be individually enabled or disabled by setting or clearing a bit in IE (Interrupt Enable). IE also exists a global disable bit, which can be cleared to disable all interrupts at once

■ Each interrupt source can also be individually set to one of two priority levels by setting or clearing a bit in IP (Interrupt Priority)

• A low-priority interrupt can be interrupted by high-priority interrupt, but not by another low-priority one

A high-priority interrupt can't be interrupted by any other interrupt source

■ If interrupt requests of the same priority level are received simultaneously, an internal polling sequence determines which request is serviced, so within each priority lever there is a second priority structure

■ This internal priority structure is determined by the polling sequence, shown in the following table

| Source | Priority Within Level |

|--------|-----------------------|

| IE0    | highest               |

| TF0    | 077                   |

| IE1    |                       |

| TF1    | lowest                |

#### **External Interrupt**

- External interrupts ~INT0 and ~INT1 have two ways of activation

- Level-activated

- Transition-activated

- This depends on bits IT0 and IT1 in TCON

- The flags that actually generate these interrupts are bits IE0 and IE1 in TCON

• On-chip hardware clears that flag that generated an external interrupt when the service routine is vectored to, but only if the interrupt was transition-activated

■ When the interrupt is level-activated, then the external requesting source is controlling the request flag, not the on-chip hardware

#### **Handling Interrupt**

• When interrupt occurs (or correctly, when the flag for an enabled interrupt is found to be set (1)), the interrupt system generates an LCALL to the appropriate location in Program Memory, unless some other conditions block the interrupt

- Several conditions can block an interrupt

- An interrupt of equal or higher priority level is already in progress

- The current (polling) cycle is not the final cycle in the execution of the instruction in progress

- The instruction in progress is RETI or any write to IE or IP registers

■ If an interrupt flag is active but not being responded to for one of the above conditions, must be still active when the blocking condition is removed, or the

denied interrupt will not be serviced

■ Next step is saving the registers on stack. The hardware-generated LCALL causes only the contents of the Program Counter to be pushed onto the stack, and reloads the PC with the beginning address of the service routine

■ In some cases it also clears the flag that generated the interrupt, and in other cases it doesn"t. It clears an external interrupt flag (IE0 or IE1) only if it was transitionavtivated.

• Having only PC be automatically saved gives programmer more freedom to decide how much time to spend saving other registers. Programmer must also be more careful with proper selection, which register to save.

■ The service routine for each interrupt begins at a fixed location. The interrupt locations are spaced at 8-byte interval, beginning at 0003H for External Interrupt 0, 000BH for Timer 0, 0013H for External Interrupt 1 and 001BH for Timer 1.

## **I/O Ports**

- The 8051 contains four I/O ports

- All four ports are bidirectional

■ Each port has SFR (Special Function Registers P0 through P3) which works like a latch, an output driver and an input buffer

■ Both output driver and input buffer of Port 0 and output driver of Port 2 are used for accessing external memory

■ Accessing external memory works like this

■ Port 0 outputs the low byte of external memory address (which is timemultiplexed with the byte being written or read)

- Port 2 outputs the high byte (only needed when the address is 16 bits wide)

- Port 3 pins are multifunctional

■ The alternate functions are activated with the 1 written in the corresponding bit in the port SFR

#### Timers

The 8051 comes equipped with two timers, both of which may be controlled, set, read, and configured individually. The 8051 timers have three general functions: 1) Keeping time and/or calculating the amount of time between events, 2) Counting the events themselves, or 3) Generating baud rates for the serial port.

one of the primary uses of timers is to measure time. We will discuss this use of timers first and will subsequently discuss the use of timers to count events. When a timer is used to measure time it is also called an "interval timer" since it is measuring the time of the interval between two events.

#### **Timer SFR**

8051 has two timers which each function essentially the same way. One timer is TIMER0 and the other is TIMER1. The two timers share two SFRs (TMOD and TCON) which control the timers, and each timer also has two SFRs dedicated solely to itself (TH0/TL0 and TH1/TL1). Table 4.4 SFR

#### 13-bit Time Mode (mode 0)

Timer mode "0" is a 13-bit timer. This is a relic that was kept around in the 8051 to maintain compatability with its predecesor, the 8048. Generally the 13-bit timer mode is not used in new development.

When the timer is in 13-bit mode, TLx will count from 0 to 31. When TLx is incremented from 31, it will "reset" to 0 and increment THx. Thus, effectively, only 13 bits of the two timer bytes are being used: bits 0-4 of TLx and bits 0-7 of THx. This also means, in essence, the timer can only contain 8192 values. If you set a 13-bit timer to 0, it will overflow back to zero 8192 Machine cycles later.

Again, there is very little reason to use this mode and it is only mentioned so you wont be surprised if you ever end up analyzing archaeic code which has been passed down through the generations (a generation in a programming shop is often on the order of about 3 or 4 months). SFR Name Description SFR Address

TH0 Timer 0 High Byte 8Ch TL0 Timer 0 Low Byte 8Ah TH1 Timer 1 High Byte 8Dh TL1 Timer 1 Low Byte 8Bh TCON Timer Control 88h TMOD Timer Mode 89h

#### 16-bit Time Mode (mode 1)

Timer mode "1" is a 16-bit timer. This is a very commonly used mode. It functions just like 13-bit mode except that all 16 bits are used.

TLx is incremented from 0 to 255. When TLx is incremented from 255, it resets to 0 and causes THx to be incremented by 1. Since this is a full 16-bit timer, the timer may contain up to 65536 distinct values. If you set a 16-bit timer to 0, it will overflow back to 0 after 65,536 machine cycles.

#### 8-bit Time Mode (mode 2)

Timer mode "2" is an 8-bit auto-reload mode. What is that, you may ask? Simple. When a timer is in mode 2, THx holds the "reload value" and TLx is the timer itself. Thus, TLx starts counting up. When TLx reaches 255 and is subsequently incremented, instead of resetting to 0 (as in the case of modes 0 and 1), it will be reset to the value stored in THx.

#### Split Timer Mode (mode 3)

Timer mode "3" is a split-timer mode. When Timer 0 is placed in mode 3, it essentially becomes two separate 8-bit timers. That is to say, Timer 0 is TL0 and Timer 1 is TH0. Both timers count from 0 to 255 and overflow back to 0. All the bits that are related to Timer 1 will now be tied to TH0.

While Timer 0 is in split mode, the real Timer 1 (i.e. TH1 and TL1) can be put into modes 0, 1 or 2 normally--however, you may not start or stop the real timer 1 since the bits that do that are now linked to TH0. The real timer 1, in this case, will be incremented every machine cycle no matter what.

#### USING TIMERS AS EVENT COUNTERS

We've discussed how a timer can be used for the obvious purpose of keeping track of

time. However, the 8051 also allows us to use the timers to count events. How can this be useful? Let's say you had a sensor placed across a road that would send a pulse every time a car passed over it. This could be used to determine the volume of traffic on the road. We could attach this sensor to one of the 8051's I/O lines and constantly monitor it, detecting when it pulsed high and then incrementing our counter when it went back to a low state. This is not terribly difficult, but requires some code. Let's say we hooked the sensor to P1.0; the code to count cars passing would look something like this: JNB P1.0,\$ ;If a car hasn't raised the signal, keep waiting JB P1.0,\$ ;The line is high which means the car is on the sensor right now INC COUNTER ;The car has passed completely, so we count it

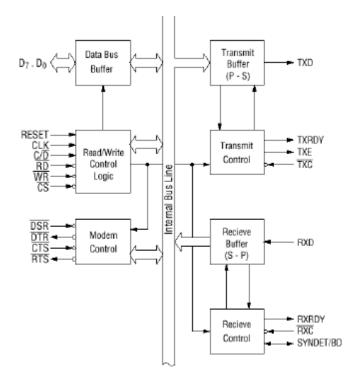

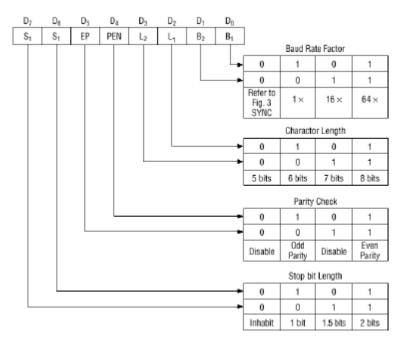

#### **Serial Communication**

Some of the external I/0 devices receive only the serial data.Normally serial communication is used in the Multi Processor environment.8051 has two pins for serial communication.

(1)SID- Serial Input data.

(2)SOD-Serial Output data.

# UNIT IV PERIPHERAL INTERFACING

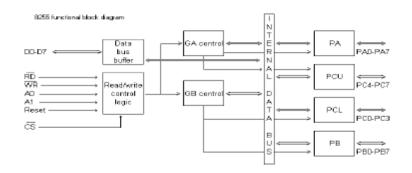

## 1)Architecture of 8255

The parallel input-output port chip 8255 is also called as programmable peripheral input output port. The Intel"s 8255 is designed for use with Intel"s 8-bit, 16-bit and higher capability microprocessors. It has 24 input/output lines which may be individually programmed in two groups of twelve lines each, or three groups of eight lines. The two groups of I/O pins are named as Group A and Group B. Each of these two groups contains a subgroup of eight I/O lines called as 8-bit port and another subgroup of four lines or a 4-bit port. Thus Group A contains an 8-bit port A along with a 4-bit port. C upper. The port A lines are identified by symbols PA0-PA7 while the port C lines are identified as PC4-PC7. Similarly, Group B contains an 8-bit port B, containing lines PB0-PB7 and a 4-bit port C with lower bits PC0- PC3. The port C upper and port C lower can be used in combination as an 8-bit port C. Both the port C are assigned the same address. Thus one may have either three 8-bit I/O ports or two 8-bit and two 4-bit ports from 8255. All of these ports can function independently either as input or as output ports. This can be achieved by programming the bits of an internal register of 8255 called as control word register ( CWR ). This buffer receives or transmits data upon the execution of input or output instructions by the microprocessor. The control words or status information is also transferred through the buffer.

# 2) PIN DIAGRAM OF 8255

The signal description of 8255 are briefly presented as follows :

• **PA7-PA0**: These are eight port A lines that acts as either latched output or buffered input lines depending upon the control word loaded into the control word register.

• **PC7-PC4** : Upper nibble of port C lines. They may act as either output latches or input buffers lines. This port also can be used for generation of handshake lines in mode 1 or mode 2.

• PC3-PC0 : These are the lower port C lines, other details are the same as PC7-PC4 lines.

• **PB0-PB7** : These are the eight port B lines which are used as latched output lines or buffered input lines in the same way as port A.

• **RD** : This is the input line driven by the microprocessor and should be low to indicate read operation to 8255.

• WR : This is an input line driven by the microprocessor. A low on this line indicates write operation.

**CS** : This is a chip select line. If this line goes low, it enables the 8255 to respond to RD and WR signals, otherwise RD and WR signal are neglected

**A1-A0** : These are the address input lines and are driven by the microprocessor. These lines A1-A0 with RD, WR and CS from the following operations for 8255. These address lines are used for addressing any one of the four registers, i.e. three ports and a control word register as given in table below

• In case of 8086 systems, if the 8255 is to be interfaced with lower order data bus, the A0 and A1 pins of 8255 are connected with A1 and A2 respectively.

#### **D0-D7**:

These are the data bus lines those carry data or control word to/from the Microprocessor.

#### **RESET** :

A logic high on this line clears the control word register of 8255. All ports are set as input ports by default after reset.

# **Operational Modes of 8255**

There are two main operational modes of 8255: 1. Input/output mode 2. Bit set/reset mode

#### **Input/Output Mode**

There are three types of the input/output mode. They are as follows:

#### • Mode 0

In this mode, the ports can be used for simple input/output operations without handshaking. If both port A and B are initialized in mode 0, the two halves of port C can be either used together as an additional 8-bit port, or they can be used as individual 4-bit ports. Since the two halves of port C are independent, they may be used such that one-half is initialized as an input port while the other half is initialized as an output port. The input output features in mode 0 are as follows: 1. O/p are latched. 2. I/p are buffered not latched. 3. Port do not have handshake or interrupt capability.

#### • Mode 1

When we wish to use port A or port B for handshake (strobed) input or output operation, we initialise that port in mode 1 (port A and port B can be initialised to operate in different modes, ie, for eg, port A can operate in mode 0 and port B in mode 1). Some of the pins of port C function as handshake lines.

For port B in this mode (irrespective of whether is acting as an input port or output port), PC0, PC1 and PC2 pins function as handshake lines.

If port A is initialised as mode 1 input port, then, PC3, PC4 and PC5 function as handshake signals. Pins PC6 and PC7 are available for use as input/output lines.

The mode 1 which supports handshaking has following features: 1. Two ports i.e. port A and B can be use as 8-bit i/o port. 2. Each port uses three lines of port c as handshake signal and remaining two signals can be function as i/o port. 3. interrupt logic is supported. 4. Input and Output data are latched.

## • Mode 2

Only group A can be initialised in this mode. Port A can be used for bidirectional handshake data transfer. This means that data can be input or output on the same eight lines (PA0 - PA7). Pins PC3 - PC7 are used as handshake lines for port A. The remaining pins of port C (PC0 - PC2) can be used as input/output lines if group B is initialised in mode 0. In this mode, the 8255 may be used to extend the system bus to a slave microprocessor or to transfer data bytes to and from a floppy disk controller.

## Bit Set/Reset (BSR) mode

In this mode only port b can be used (as an output port). Each line of port C (PC0 - PC7) can be set/reset by suitably loading the command word register.no effect occurs in input-output mode. The individual bits of port c can be set or reset by sending the signal OUT instruction to the control register.

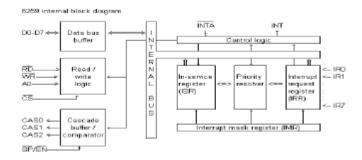

# 3)PROGRAMMABLE INTERRUPT CONTROLLER(8259)

8 levels of interrupts.

- Can be cascaded in master-slave configuration to handle 64 levels of interrupts.

- Internal priority resolver.

- Fixed priority mode and rotating priority mode.

- Individually maskable interrupts.

- Modes and masks can be changed dynamically.

• Accepts IRQ, determines priority, checks whether incoming priority > current level being serviced, issues interrupt signal.

- In 8085 mode, provides 3 byte CALL instruction. In 8086 mode, provides 8 bit vector number.

- Polled and vectored mode.

- Starting address of ISR or vector number is programmable.

- No clock required

| CS.  | -1 |      | 10 | Vec   |

|------|----|------|----|-------|

|      |    |      |    |       |

| WR.  | 2  |      | 27 | AD    |

| RD   | 3  |      | 26 | INTA  |

| D7   | 4  |      | 25 | IR7   |

| D6   | 5  |      | 24 | IR5   |

| D6   | Б  |      | 23 | 165   |

| D4   | 7  | B259 | 22 | IR4   |

| DG   | в  | PIC  | 21 | IR3   |

| D2   | 9  |      | 20 | IR2   |

| D1   | 10 |      | 19 | IR1   |

| DO.  | 11 |      | 1B | IR0   |

| CASE | 12 |      |    | INT   |

| CAS1 | 13 |      | 16 | SP/EN |

| gnd  | 14 |      | 15 | CAS2  |

# Pin diagram

| D0-D7              | Bi-directional, tristated, buffered data lines. Connected to data bus directly or through<br>buffers                                                                                                         |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RD-bar             | Active low read control                                                                                                                                                                                      |

| WR-bar             | Active low write control                                                                                                                                                                                     |

| A0                 | Address input line, used to select control register                                                                                                                                                          |

| CS-bar             | Active low chip select                                                                                                                                                                                       |

| CAS0-2             | Bi-directional, 3 bit cascade lines. In master mode, PIC places slave ID no. on these<br>lines. In slave mode, the PIC reads slave ID no. from master on these lines. It may be<br>regarded as slave-select. |

| SP-bar /<br>EN-bar | Slave program / enable. In non-buffered mode, it is SP-bar input, used to distinguish master/slave PIC. In buffered mode, it is output line used to enable buffers                                           |

| INT                | Interrupt line, connected to INTR of microprocessor                                                                                                                                                          |

| INTA-bar           | Interrupt ack, received active low from microprocessor                                                                                                                                                       |

| IR0-7              | Asynchronous IRQ input lines, generated by peripherals.                                                                                                                                                      |

#### ICW1 (Initialisation Command Word One)

| A0 | D7 | D6 | D5 | D4 | D3   | D2  | DI   | D0  |

|----|----|----|----|----|------|-----|------|-----|

| 0  | A7 | A6 | A5 | 1  | LTIM | ADI | SNGL | IC4 |

D0: IC4: 0=no ICW4, 1=ICW4 required

D1: SNGL: 1=Single PIC, 0=Cascaded PIC D2: ADI: Address interval. Used only in 8085, not 8086. 1=ISR's are 4 bytes apart (0200, 0204, etc) 0=ISR's are 8 byte apart (0200, 0208, etc)

D3: LTIM: level triggered interrupt mode: 1=All IR lines level triggered. 0=edge triggered D4-D7: A5-A7: 8085 only. ISR address lower byte segment. The lower byte is

A7 A6 A5 A4 A3 A2 A1 A0

of which A7, A6, A5 are provided by D7-D5 of ICW1 (if ADI=1), or A7, A6 are provided if ADI=0. A4-A0 (or A5-A0) are set by 8259 itself:

ADI=1 (spacing 4 bytes)

| ALDI=1 (spacing 4 bytes) |            |    |            |            |    |            |            |    |  |  |  |  |

|--------------------------|------------|----|------------|------------|----|------------|------------|----|--|--|--|--|

| IRQ                      | <b>A</b> 7 | A6 | A5         | <b>A</b> 4 | A3 | <b>A</b> 2 | <b>A</b> 1 | A0 |  |  |  |  |

| IR0                      | <b>A</b> 7 | A6 | <b>A</b> 5 | 0          | 0  | 0          | 0          | 0  |  |  |  |  |

| IR1                      | <b>A</b> 7 | A6 | <b>A</b> 5 | 0          | 0  | 1          | 0          | 0  |  |  |  |  |

| IR2                      | <b>A</b> 7 | A6 | <b>A</b> 5 | 0          | 1  | 0          | 0          | 0  |  |  |  |  |

| IR3                      | <b>A</b> 7 | A6 | A5         | 0          | 1  | 1          | 0          | 0  |  |  |  |  |

| IR4                      | <b>A</b> 7 | A6 | <b>A</b> 5 | 1          | 0  | 0          | 0          | 0  |  |  |  |  |

| IR5                      | <b>A</b> 7 | A6 | <b>A</b> 5 | 1          | 0  | 1          | 0          | 0  |  |  |  |  |

| IR6                      | <b>A</b> 7 | A6 | <b>A</b> 5 | 1          | 1  | 1          | 0          | 0  |  |  |  |  |

| IR7                      | <b>A</b> 7 | A6 | <b>A</b> 5 | 1          | 1  | 1          | 0          | 0  |  |  |  |  |

|     | ADI=0 (spacing 8 bytes) |    |            |           |            |            |            |            |  |  |  |  |  |  |

|-----|-------------------------|----|------------|-----------|------------|------------|------------|------------|--|--|--|--|--|--|

| IRQ | <b>A</b> 7              | A6 | <b>A</b> 5 | <b>A4</b> | <b>A</b> 3 | <b>A</b> 2 | <b>A</b> 1 | <b>A</b> 0 |  |  |  |  |  |  |

| IR0 | <b>A</b> 7              | A6 | 0          | 0         | 0          | 0          | 0          | 0          |  |  |  |  |  |  |

| IR1 | <b>A</b> 7              | A6 | 0          | 0         | 1          | 0          | 0          | 0          |  |  |  |  |  |  |

| IR2 | <b>A</b> 7              | A6 | 0          | 1         | 0          | 0          | 0          | 0          |  |  |  |  |  |  |

| IR3 | <b>A</b> 7              | A6 | 0          | 1         | 1          | 0          | 0          | 0          |  |  |  |  |  |  |

| IR4 | <b>A</b> 7              | A6 | 1          | 0         | 0          | 0          | 0          | 0          |  |  |  |  |  |  |

| IR5 | <b>A</b> 7              | A6 | 1          | 0         | 1          | 0          | 0          | 0          |  |  |  |  |  |  |

| IR6 | <b>A</b> 7              | A6 | 1          | 1         | 0          | 0          | 0          | 0          |  |  |  |  |  |  |

| IR7 | A7                      | A6 | 1          | 1         | 1          | 0          | 0          | 0          |  |  |  |  |  |  |

|     |                         |    |            |           |            |            |            |            |  |  |  |  |  |  |

| 1                   | R                                       | SL         | EOI |                        |          |             | 0                                        | L3          | L2          | L1              |  |  |

|---------------------|-----------------------------------------|------------|-----|------------------------|----------|-------------|------------------------------------------|-------------|-------------|-----------------|--|--|

|                     |                                         |            |     | R                      | SL       | EOI         | Action                                   |             |             |                 |  |  |

|                     |                                         | 0          | 0   | 1                      | Non spec | ific EOI (  | L3L2L1=0                                 | )00)        |             |                 |  |  |

| EOI                 | 0                                       | 1          | 1   | Specific l<br>given by |          | nand (Inter | rupt to clear                            |             |             |                 |  |  |

|                     |                                         |            |     |                        | 0        | 1           | Rotate priorities on non-specific EOI    |             |             |                 |  |  |

| Auto rot<br>(L3L2L1 | ation of prio                           | priorities |     | 1                      | 0        | 0           | Rotate pr                                | iorities in | auto EOI    | mode set        |  |  |

| (25222)             |                                         |            |     |                        |          | 0           | Rotate priorities in auto EOI mode clear |             |             |                 |  |  |

| Spacific            | Specific rotation of priorities (Lowest |            |     |                        |          | 1           | Rotate pr<br>(resets cu                  | -           | -           | OI command      |  |  |

|                     | ISR=L3L2I                               |            |     | 1                      | 1        | 0           | Set priori                               | ty (does n  | ot reset cu | urrent ISR bit) |  |  |

|                     |                                         | (-LJL2L1)  |     |                        | 1        | 0           | No opera                                 | tion        |             |                 |  |  |

#### OCW3 (Operational Command Word Three)

| AO | D7 | D6   | D5  | D4 | D3 | D2   | Dl  | D0  |

|----|----|------|-----|----|----|------|-----|-----|

| 1  | D7 | ESMM | SMM | 0  | 1  | MODE | RIR | RIS |

| ESMM | SMM | Effect             |

|------|-----|--------------------|

| 0    | х   | No effect          |

| 1    | 0   | Reset special mask |

| 1    | 1   | Set special mask   |

#### ICW2 (Initialisation Command Word Two)

Higher byte of ISR address (8085), or 8 bit vector address (8086).

| A0 | D7  | D6  | D5  | D4  | D3  | D2  | D1 | D0 |

|----|-----|-----|-----|-----|-----|-----|----|----|

| 1  | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 |

#### ICW3 (Initialisation Command Word Three)

| AO |        | D7 | D6 | D5 | D4 | D3 | D2  | D1  | D0 |

|----|--------|----|----|----|----|----|-----|-----|----|

| 1  | Master | S7 | S6 | S5 | S4 | S3 | S2  | S1  | S0 |