# Digital Logic Circuits Unit 1

# 2. Course Objectives

- To introduce various number systems and methods to simplify the logical expressions using Boolean functions

- To understand the combinational circuits

- To design various synchronous and asynchronous circuits.

- To introduce asynchronous sequential circuits and PLDs

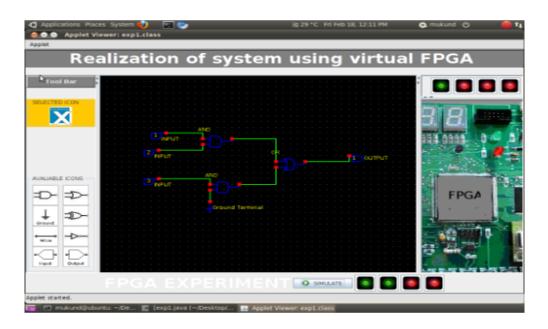

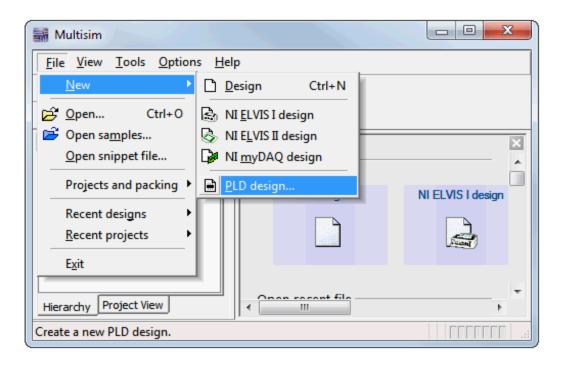

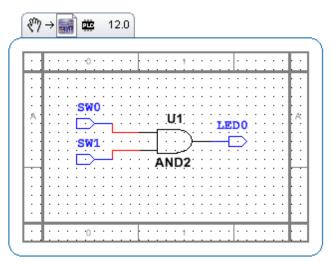

- To introduce digital simulation for development of application oriented logic circuits

- 3. Pre Requisites (Course Names with Code)

- The pre requisite course is:

- Circuit Theory EE 8251

#### 4. Syllabus (With Subject Code, Name, LTPC details) DIGITAL LOGIC CIRCUITS LTPC © EE8351

# 2203

# UNIT I NUMBER SYSTEMS AND DIGITAL LOGIC FAMILIES 6+6

Review of number systems, binary codes, error detection and correction codes (Parity and Hamming code) - Digital Logic Families -comparison of RTL, DTL, TTL, ECL and MOS families -operation, characteristics of digital logic family.

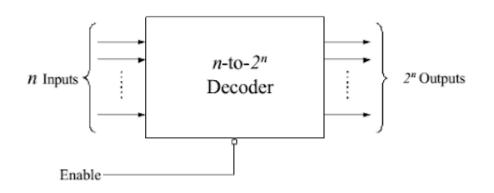

# UNIT II COMBINATIONAL CIRCUITS

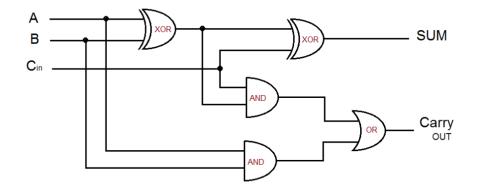

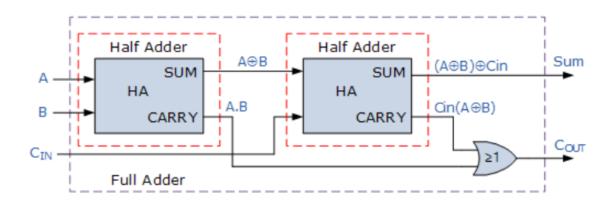

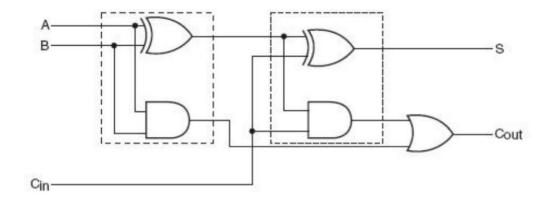

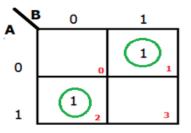

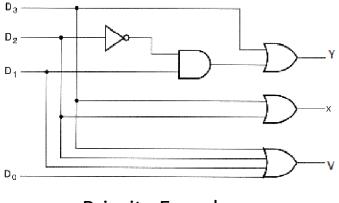

Combinational logic - representation of logic functions-SOP and POS forms, K-map representations - minimization using K maps – simplification and implementation of combinational logic –multiplexers and de multiplexers – code converters, adders, subtractors, Encoders and Decoders.

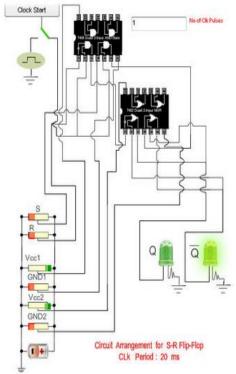

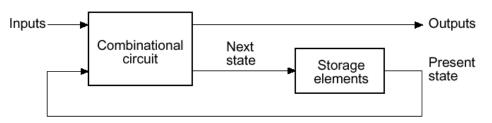

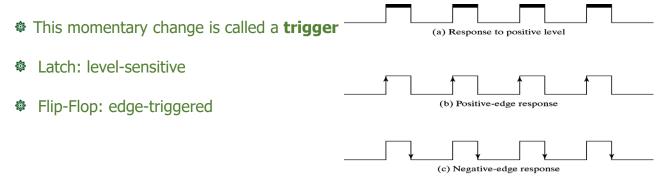

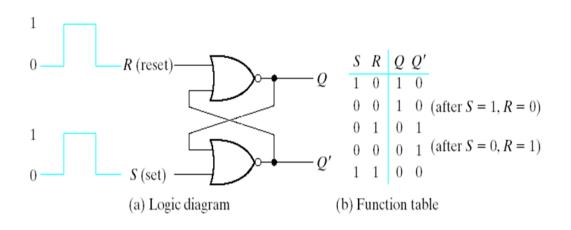

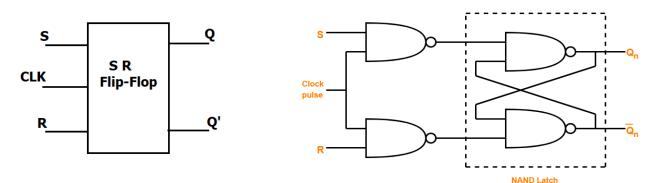

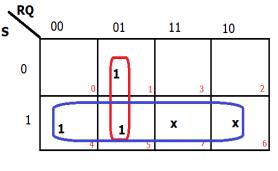

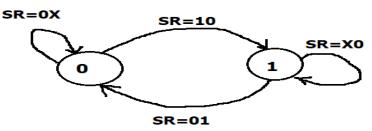

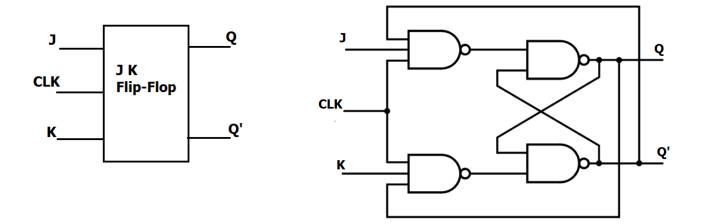

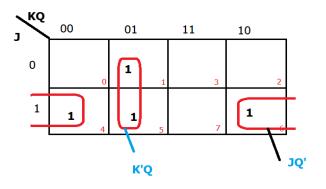

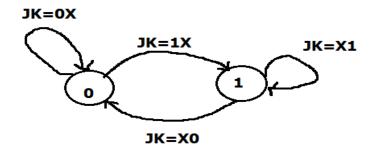

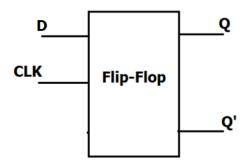

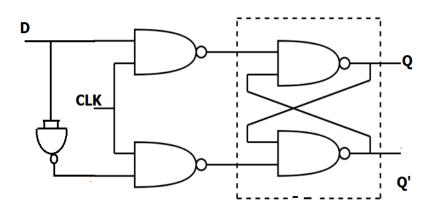

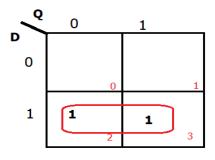

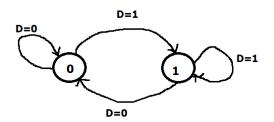

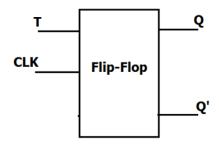

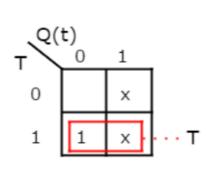

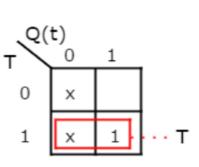

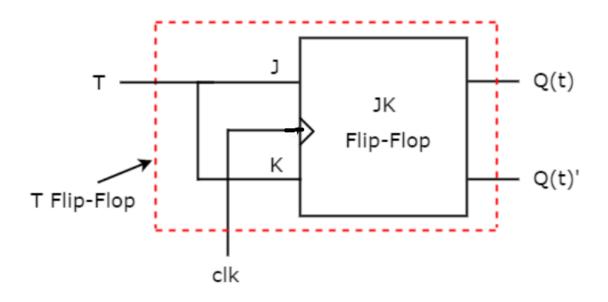

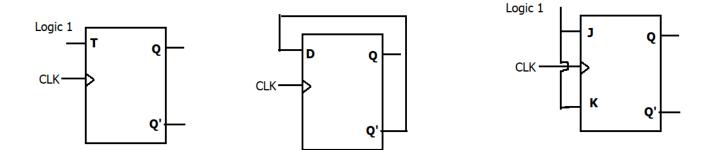

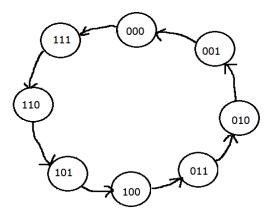

#### UNIT III SYNCHRONOUS SEQUENTIAL CIRCUITS 6+6 Sequential logic- SR, JK, D and T flip flops - level triggering and edge triggering -

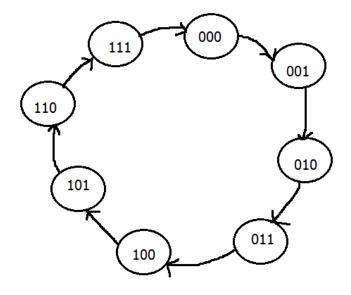

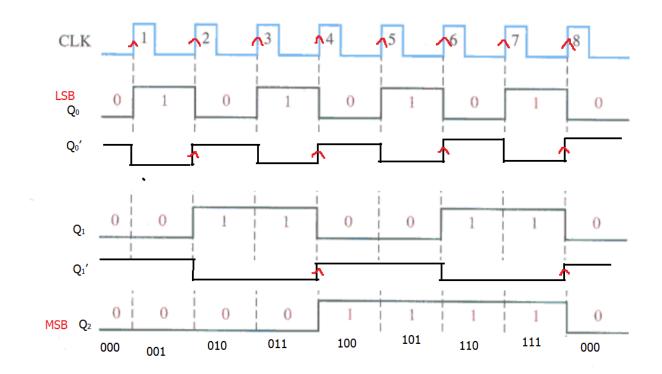

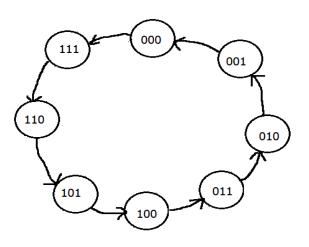

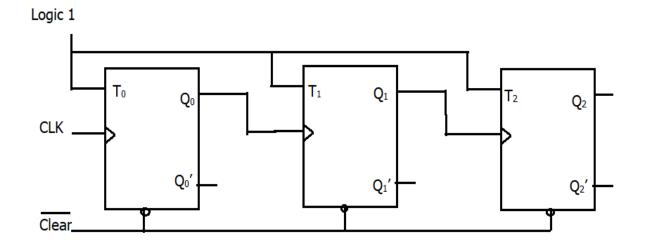

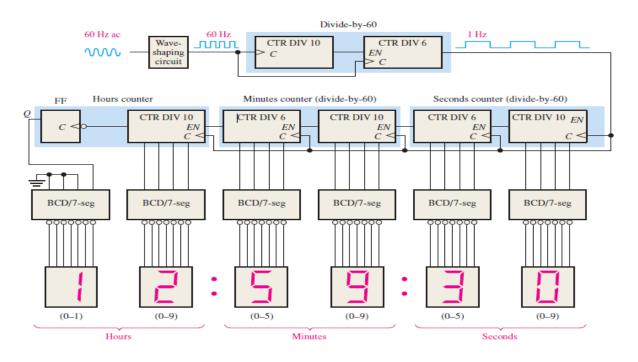

counters -asynchronous and synchronous type - Modulo counters - Shift registers design of synchronous sequential circuits – Moore and Melay models- Counters, state diagram; state reduction; state assignment.

#### 🕸 UNIT ASYNCHRONOUS SEQUENTIAL UNIT IV ASYN PROGRAMMABILITY CIRCUITS AND LOGIC DEVICES 6+6

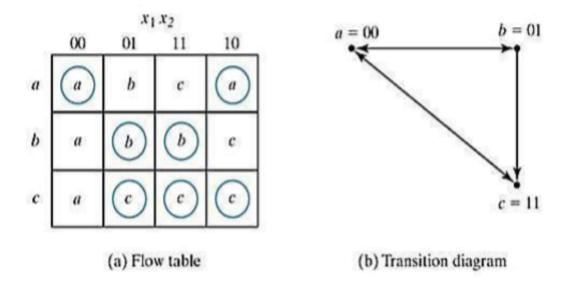

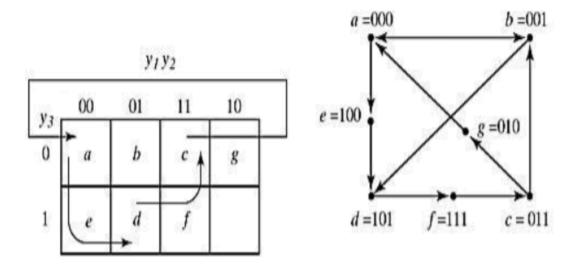

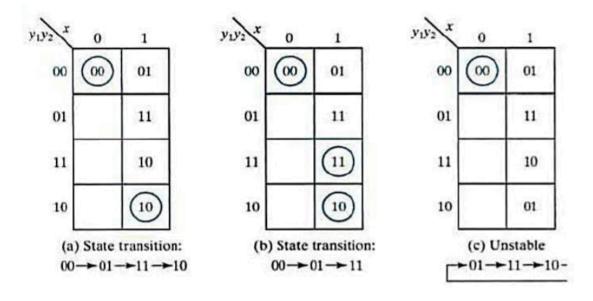

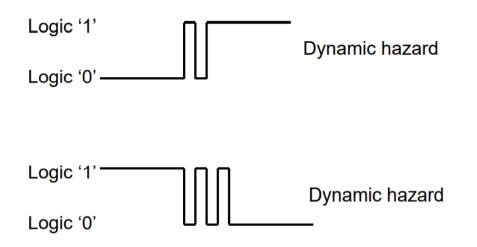

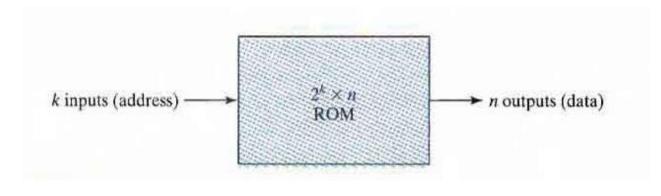

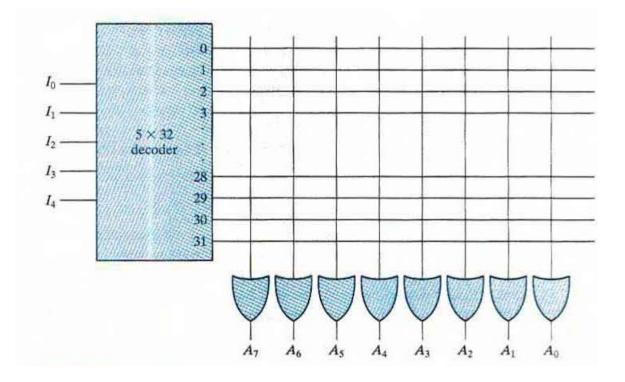

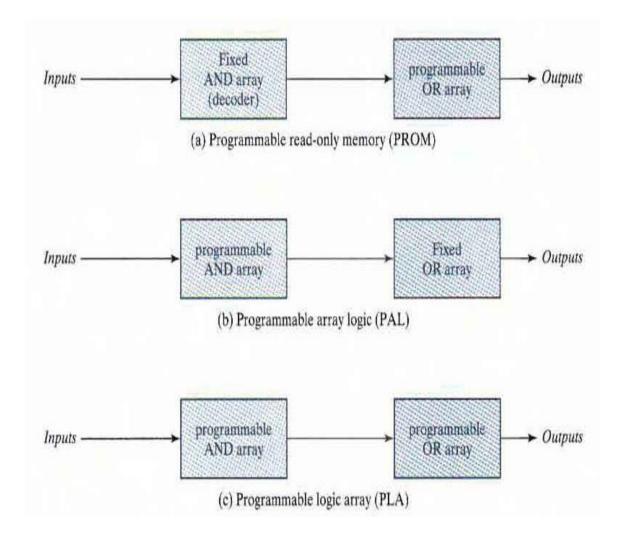

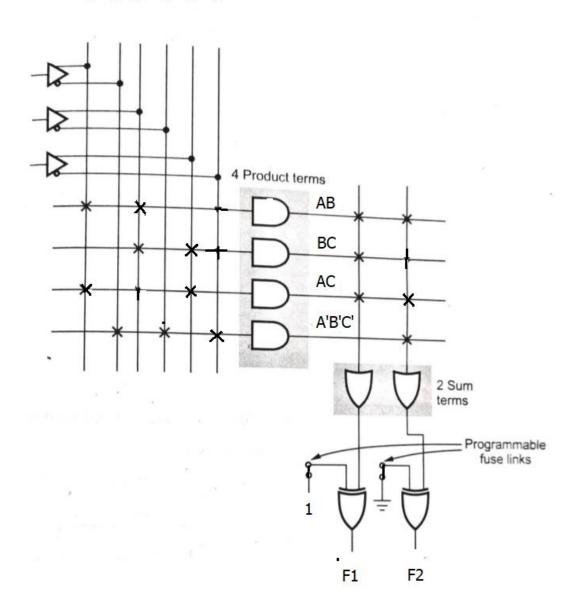

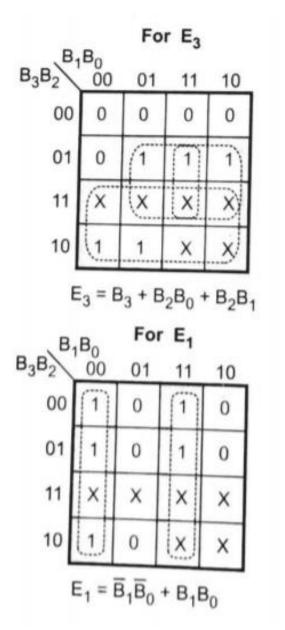

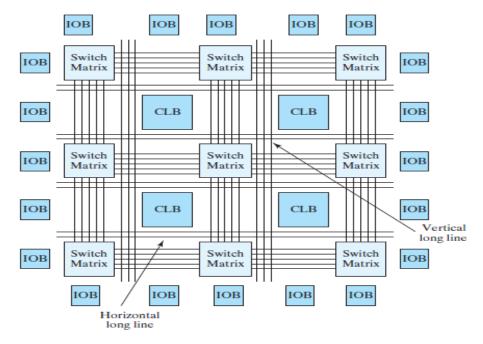

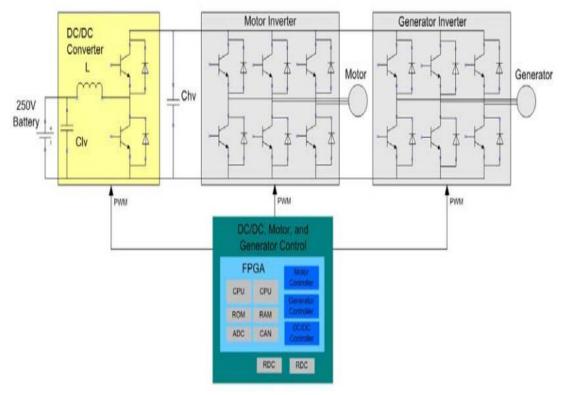

Asynchronous sequential logic circuits-Transition stability, flow stability-race conditions, hazards & errors in digital circuits; analysis of asynchronous sequential logic Circuits, introduction to Programmability Logic Devices: PROM - PLA - PAL, CPLD-FPGA.

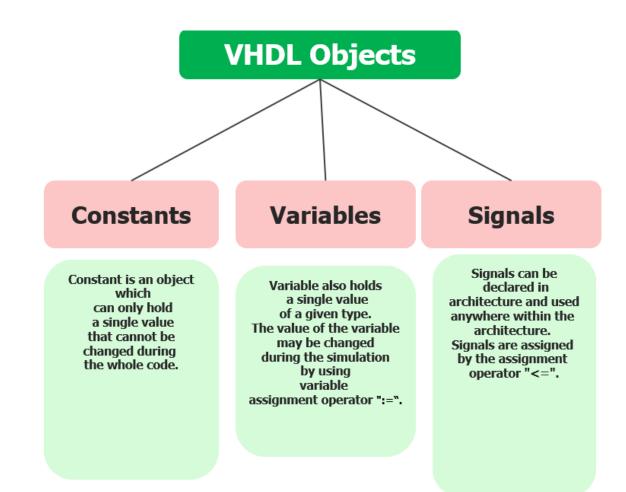

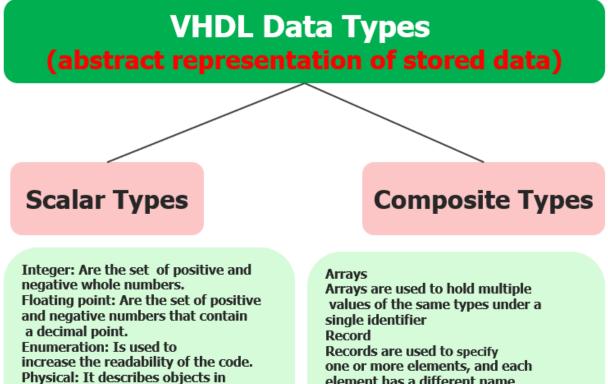

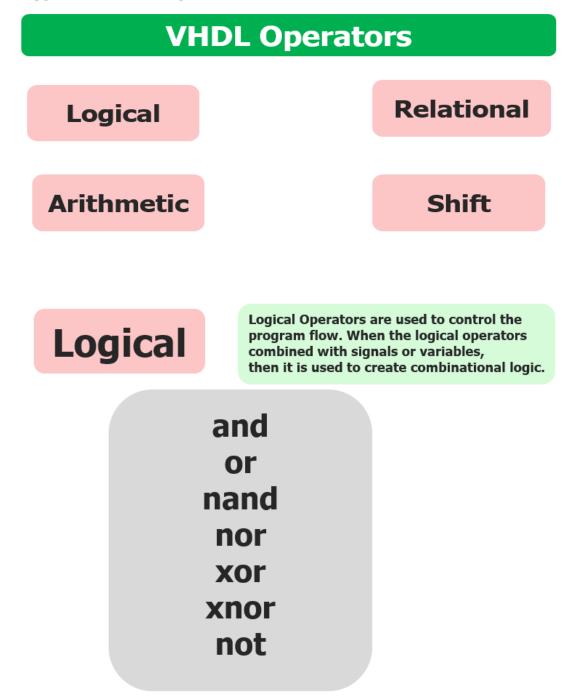

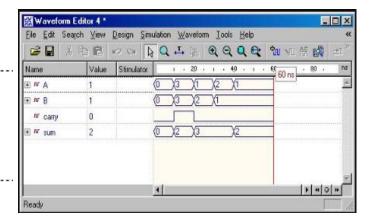

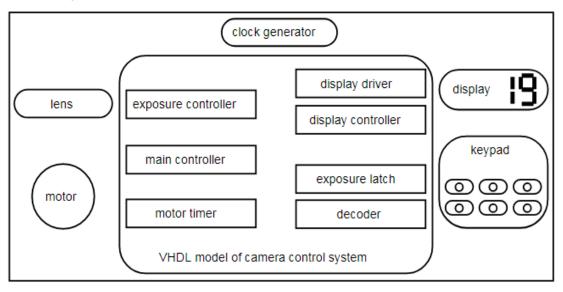

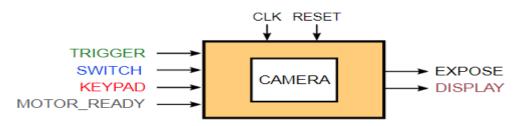

# UNIT V VHDL

RTL Design – combinational logic – Sequential circuit – Operators – Introduction to Packages – Subprograms – Test bench. (Simulation /Tutorial Examples: adders, counters, flip flops, Multiplexers & De multiplexers).

# TOTAL: 60 PERIODS

6+6

6+6

- TEXT BOOKS:

- 1.James W. Bignel, Digital Electronics, Cengage learning, 5th Edition, 2007.

- 2.M. Morris Mano, 'Digital Design with an introduction to the VHDL', Pearson Education, 2013.

- 3.Comer "Digital Logic & State Machine Design, Oxford, 2012.

#### REFERENCES

- 1.Mandal, "Digital Electronics Principles & Application, McGraw Hill Edu, 2013.

- 2.William Keitz, Digital Electronics-A Practical Approach with VHDL, Pearson, 2013.

- 3.Thomas L.Floyd, 'Digital Fundamentals', 11th edition, Pearson Education, 2015.

- 4.Charles H.Roth, Jr, Lizy Lizy Kurian John, 'Digital System Design using VHDL, Cengage, 2013.

# 8. Activity based learning

Basic level –

Play with Binary Numbers using Binary Puzzles http://www.binarypuzzle.com/

Binary to create on-off pictures, Binary magic tricks

https://www.digitaltechnologieshub.edu.au

- Troubleshooting Logic Gates for

- 1.Open Input

- 2. Open Output conditions

- Logic Gate Testing using Multisim software

- Practice using open source DEEDS: <u>https://www.digitalelectronicsdeeds.com/</u>

# 9. Lecture Notes **Table of Contents**

# **© UNIT I NUMBER SYSTEMS AND DIGITAL LOGIC FAMILIES**

- Review of number systems

- Binary codes

- Error detection and correction codes

- Parity and

- Hamming code

- Digital Logic Families

- RTL, DTL, TTL, ECL and MOS -operation, characteristics of digital logic family

- Comparison of RTL, DTL, TTL, ECL and MOS families

# **Digital System Introduction**

- We are in the digital era and digital systems are used in the industries, internet, medical treatment, space applications, communication, and all possible areas of automation.

- A few examples of digital systems start with a basic calculator to digital computer, digital telephones, digital media, digital money, digital control systems, home appliances, etc.

- A digital system is an interconnection of digital modules to give a required output or to do a specified operation.

- A basic knowledge of digital circuits and their logical function is required to understand the operation of each digital module.

- Digital System manipulates discrete elements of information represented in binary form.

- Discrete elements of information are represented with groups of bits called binary codes.

- The signals in most present-day electronic digital systems use just two discrete values 0 and 1 represented by a binary digit, called a bit.

- The natural signals generated by the nature are mostly continuous in nature like Temperature, Voltage, Current (can be converted to discreet)

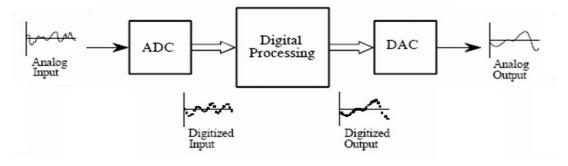

- The processing in a digital system basically has the following sections:

Input: Analog-to-Digital (A/D) converter at the input end.

Processing: Done using a digital system.

Output: Digital-to-Analog (D/A) converter at the output end.

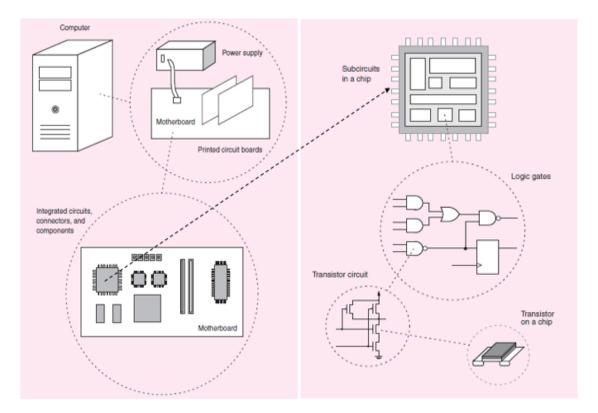

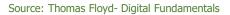

# The Hardware Levels of Digital System

- The levels of the hardware system from a CPU to a single transistor layout is shown below.

- The design level, logical representation and the elements that form the circuit at each level are also shown below.

# NUMBER SYSTEMS AND DIGITAL LOGIC FAMILIES

# 1. Review of number systems

# 1.1 Introduction:

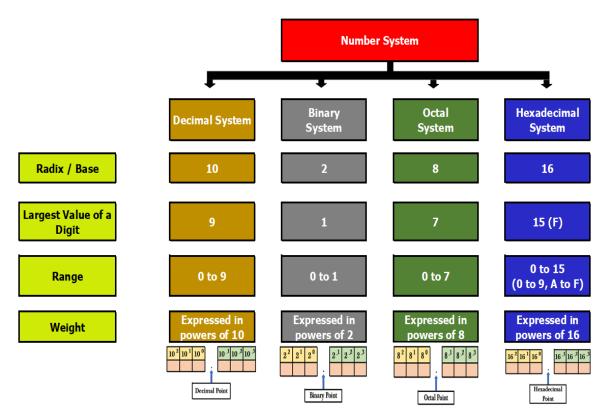

- 1. Number System defines a set of values used to represent a quantity.

- 2. Number System is a basis for counting various items.

- 3. Digits: A collection of various symbols in a number system is called digits.

- 4. Radix / Base: The number of unique digits (including Digit 0) used to represent the numbers in a positional number system is called radix or base of a number system.

# (or)

The number of values that a digit (one character) can assume in a positional number system is called radix or base of a number system.

- 5. The largest value of a digit is always one less than radix / base of a number system.

- 6. Weight / Value: In a positional number system, the position of a digit with reference to the decimal point determines the weight / value.

- a. Usually weight / value is expressed in powers of radix / base.

- b. The sum of all digits multiplied by their weight gives the total number being represented.

- Most Significant Digit / Bit: The leftmost digit / bit which has the greatest weight is called Most Significant Digit / Bit (MSD / MSB).

- 8. Least Significant Digit / Bit: The rightmost digit / bit which has the least weight is called Least Significant Digit / Bit (LSD / LSB).

# 1.2 Classification of Number System:

# 1.2.1 Decimal Number System:

- 1. Base: Base 10 System / Radix 10 System.

- a. Number of values assumed by each digit: 10

- b. Range: Uses ten digits: 0,1,2,3,4,5,6,7,8,9.

- c. Each digit in the Decimal Number System will assume 10 different values from 0 to 9.

- 2. Largest Value of a digit: The largest value a digit can take is 9.

- a. If larger values than 9 are needed, extra columns are added to the left.

Each column value is now ten times the value of the column to its right.

For example, the decimal value 47 is written 47 (4 tens + 7 ones).

- 3. Positional Weights: The positional weight of each digit is represented in the power of 10.

# 1.2.2 Binary Number System:

- 1. Base: Base 2 System / Radix 2 System.

- a. Number of values assumed by each digit: 2

- b. Range: Uses two digits: 0,1.

- c. Each digit in the Binary Number System will assume 2 different values either 0 or 1.

- 2. Largest Value of a digit: The largest value a digit can take is 1.

- a. If larger values than 1 are needed, extra columns are added to the left.

Each column value is now two times the value of the column to its right.

For example, the decimal value 2 is written 10 in binary (1 twos + 0 ones).

- 3. Positional Weights: The positional weight of each digit is represented in the power of 2.

# 1.2.3 Octal Number System:

- 1. Base: Base 8 System / Radix 8 System.

- a. Number of values assumed by each digit: 8

- b. Range: Uses ten digits: 0,1,2,3,4,5,6,7.

- c. Each digit in the Octal Number System will assume 8 different values from 0 to 7.

- 2. Largest Value of a digit: The largest value a digit can take is 7.

- a. If larger values than 7 are needed, extra columns are added to the left.

Each column value is now eight times the value of the column to its right.

For example, the decimal value 27 is written 33 in octal (3 eights + 3 ones).

- 3. Positional Weights: The positional weight of each digit is represented in the power of 8.

# 1.2.4 Hexadecimal Number System:

- 1. Base: Base 16 Number System / Radix 16 Number System.

- a. Number of values assumed by each digit: 16

- b. Range: Uses ten digits: 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F.

- c. Each digit in the Octal Number System will assume 16 different values from 0 to 9, A to F.

- 2. Largest Value of a digit: The largest value a digit can take is F.

- a. If larger values than F are needed, extra columns are added to the left.

Each column value is now sixteen times the value of the column to its right. For example, the decimal value 68 is written as 44 in hexadecimal (4 sixteens + 4 ones).

- 3. Positional Weights: The positional weight of each digit is represented in the power of 16.

| Radix / Base | Characters / Range              | Largest Value |

|--------------|---------------------------------|---------------|

| 2            | 0 ,1                            | 1             |

| 3            | 0,1,2                           | 2             |

| 4            | 0,1,2,3                         | 3             |

| 5            | 0,1,2,3,4                       | 4             |

| 6            | 0,1,2,3,4,5                     | 5             |

| 7            | 0,1,2,3,4,5,6                   | 6             |

| 8            | 0,1,2,3,4,5,6,7                 | 7             |

| 9            | 0,1,2,3,4,5,6,7,8               | 8             |

| 10           | 0,1,2,3,4,5,6,7,8,9             | 9             |

| 11           | 0,1,2,3,4,5,6,7,8,9,A           | A(10)         |

| 12           | 0,1,2,3,4,5,6,7,8,9,A,B         | B(11)         |

| 13           | 0,1,2,3,4,5,6,7,8,9,A,B,C       | C(12)         |

| 14           | 0,1,2,3,4,5,6,7,8,9,A,B,C,D     | D(13)         |

| 15           | 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E   | E(14)         |

| 16           | 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F | F(15)         |

# 1.2.5 Other Number Systems:

# 1.3 Conversion Between Number Systems:

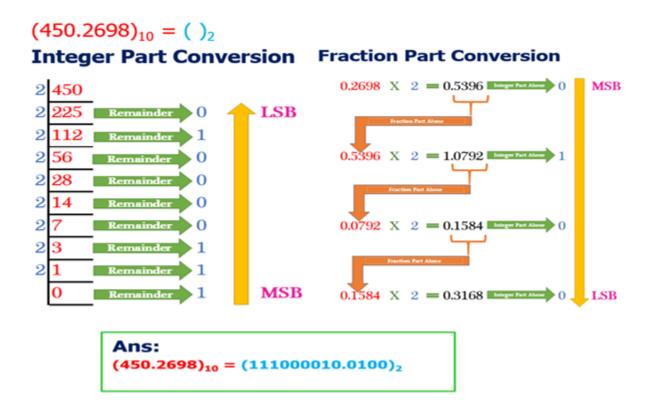

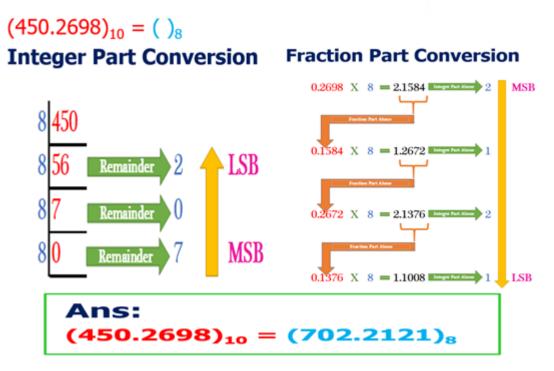

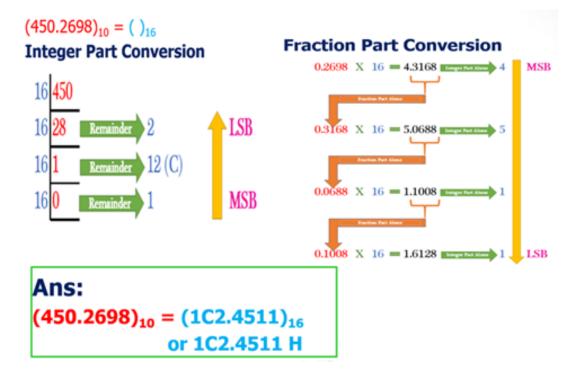

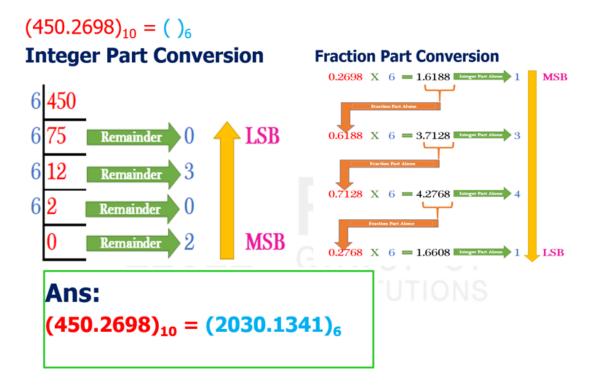

# 1.3.1 Decimal to Other Number System Conversion:

# Integer Part Conversion:

- 1. Successively divide by the base of the other number system.

- 2. Bottom to top approach.

#### Fraction Part Conversion:

- 1. Successively multiply by the base of the other number system.

- 2. Top to bottom approach.

# Decimal to Binary Conversion:

# Decimal to Octal Conversion:

# Decimal to Hexadecimal Conversion:

# Decimal to Any Other Number System Conversion:

# Remember!!!!

| Decimal | Binary |

|---------|--------|

| 0       | 0000   |

| 1       | 0001   |

| 2       | 0010   |

| 3       | 0011   |

| 4       | 0100   |

| 5       | 0101   |

| 6       | 0110   |

| 7       | 0111   |

| 8       | 1000   |

| 9       | 1001   |

| 10      | 1010   |

| 11      | 1011   |

| 12      | 1100   |

| 13      | 1101   |

| 14      | 1110   |

| 15      | 1111   |

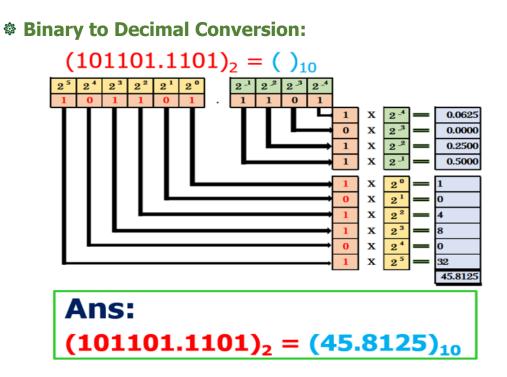

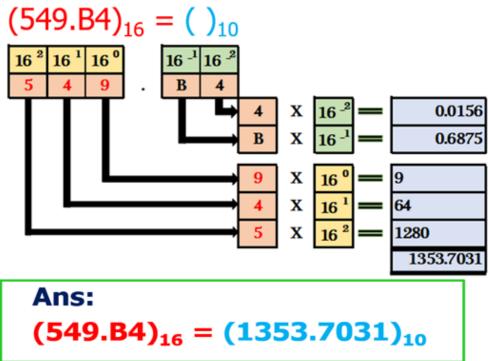

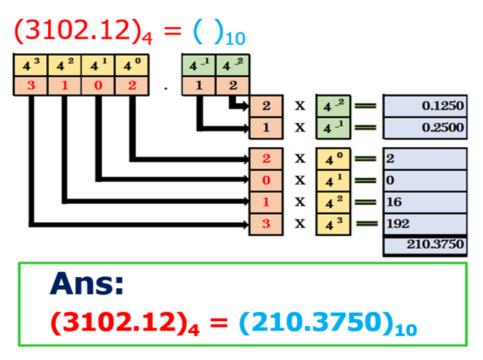

# 1.3.2 Other Number System to Decimal Conversion:

Express in powers of base of other number system.

Octal to Decimal Conversion:

$(475.25)_8 = ()_{10}$ 8<sup>2</sup> 8 0 8 8 8 -2 2 5 8 -2 5 0.0781 х 2 х 0.2500 8 х 8° 5 5 х 81 56 7 8<sup>2</sup> 256 х 317.3281 Ans:  $(475.25)_8 = (317.3281)_{10}$

# Hexadecimal to Decimal Conversion:

# Any Other Number System to Decimal Conversion:

# 1.3.3 Binary to Other Number System Conversion:

## Binary to Octal Conversion:

Group 3 binary bits and write the octal equivalent.

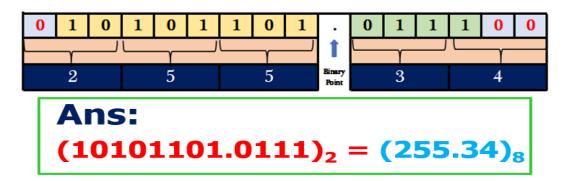

# $(10101101.0111)_2 = ()_8$

# Binary to Hexadecimal Conversion:

Group 4 binary bits and write the hexadecimal equivalent.

# $(1110101101.01111)_2 = ()_{16}$

| 0 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 |                 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|-----------------|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   | 1 |   |   | γ |   |                 |   | r |   |   |   |   |   |   |

|   |   | 3 |   |   | ł | ł |   |   | l | D |   | Einary<br>Point |   | 1 | 7 |   |   | 8 | 3 |   |

Ans: (1110101101.01111)<sub>2</sub> = (3AD.78)<sub>16</sub> or 3AD.78 H

# 1.3.4 Octal to Other Number System Conversion:

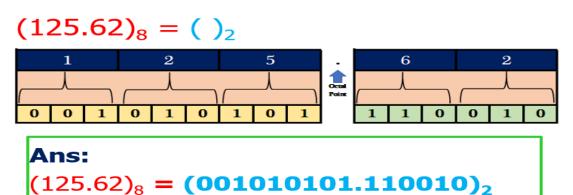

#### Octal to Binary Conversion:

Write the 3 bit binary equivalent for each of the octal digit.

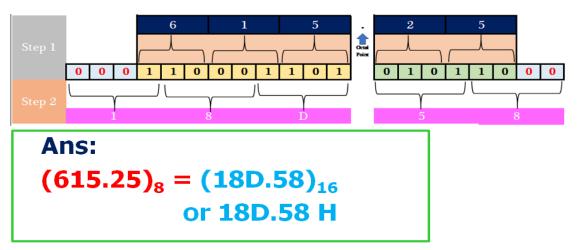

#### Octal to Hexadecimal Conversion:

- Step 1: Octal to Binary Conversion.

- Step 2: Binary to Hexadecimal Conversion.

# $(615.25)_8 = ()_{16}$

# 1.3.4 Hexadecimal to Other Number System Conversion:

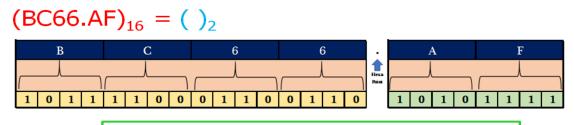

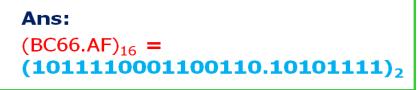

### Hexadecimal to Binary Conversion:

Write the 4 bit binary equivalent for each of the hexadecimal digit.

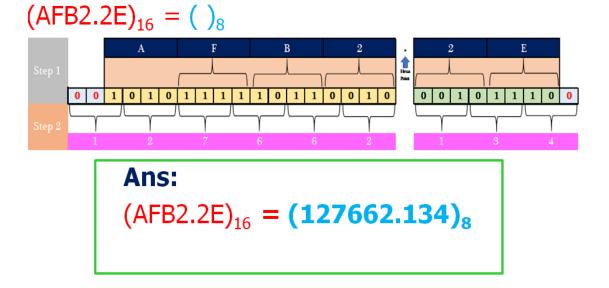

#### Hexadecimal to Octal Conversion:

Step 1: Hexadecimal to Binary Conversion.

Step 2: Binary to Octal Conversion.

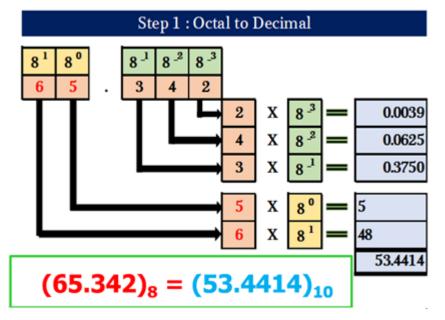

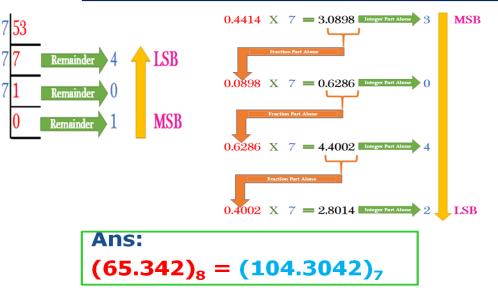

# I.3.4 Any Other Number System 1 to Any Other Number System 2 Conversion:

- Step 1: Any Other Number System 1 to Decimal Conversion.

- Step 2: Decimal to Any Other Number System 2 Conversion.

# $(65.342)_8 = ()_7$

# 2. Representation of Signed Number

#### 2.1 Signed magnitude

For Positive number - sign bit will be 0

- For negative number sign bit will be 1

- The various ways of representing negative numbers are:

- 1.sign magnitude

- 2. 1's complement

- 3. 2's complement

- Sign magnitude 1 101001

- 1's complement 1 010110

- 2's complement 1 010111

#### 2.2 1'S COMPLEMENT SUBTRACTION:

Subtraction of smallest number from largest number

Ex 1: 43-21 = 22

43 in Binary 101011

21 in Binary 010101

1's complement of 21 = 101010

101011

101010 +

=1010101 = 010101 + 1 (End around Carry)

#### = 010110

- If carry is present. The answer is positive.

- For 1's complement you have to do End around carry.

Ans =+22

Subtraction of largest number from smallest number.

Ex 2: 21-43

Soln:

21 in Binary 010101

43 in Binary 101011

43 in Binary 101011

1's complement of 43 = 010100

010101

010101

010100 +

= 101001

There is no carry. Answer is negative.

Ans = -(1's complement 101001)

=-010110 = - 22

### © 2.3 2'S COMPLEMENT SUBTRACTION:

Subtraction of smallest number from largest number using 2's complement.

Ex:1) 43-21 = 22

43 in Binary 101011

21 in Binary 010101

2's complement of 21 = 1's complement of 21 + 1

= 101010 + 1 = 101011

101010

1 +

= 101011

(1+1+1 = 10+1 = 11)

101011 43 in Binary

101011+2's complement of 21

= 1 010110 (Ignore Carry)

010110

If carry is present. The answer is positive.

For 2's complement you have to do Ignore carry.

Ans =+22

Subtraction of largest number from smallest number using 2's complement.

✤ Ex: 2) 21-43

Soln:

21 in Binary 010101

43 in Binary 101011

2's complement of 43 = 1's complement of 43

+1

= 010100 +1 =010101

010101 21 in Binary 010101 + 2's complement of 43

There is no carry. Answer is negative.

Ans = -(2's complement 101010)

010101 +1 = 010110

=-(010110) =-22

# 3. Binary Codes

- In the coding, when numbers, letters or words are represented by a specific group of symbols, it is said that the number, letter or word is being encoded. The group of symbols is called as a code.

- The digital data is represented, stored and transmitted as group of binary bits. This group is also called as **binary code**. The binary code is represented by number as well as alphanumeric letter.

#### Advantages of Binary Code

Binary codes are suitable for computer applications.

Binary codes are suitable for the digital communications.

Binary codes make the analysis and designing of digital circuits easier since only 0 & 1 are being used.

# 3.1 Classification of binary codes

The codes are broadly categorized into following four categories.

- Weighted Codes

- Non-Weighted Codes

- Binary Coded Decimal Code

- Alphanumeric Codes

- Error Detecting Codes

- Error Correcting Codes

#### 3.1.1 Weighted Codes

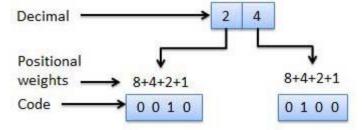

Weighted binary codes are those binary codes which obey the positional weight principle. Each position of the number represents a specific weight. Several systems of the codes are used to express the decimal digits 0 through 9. In these codes each decimal digit is represented by a group of four bits.

#### 3.1.2 Non-Weighted Codes

In this type of binary codes, the positional weights are not assigned.

The examples of non-weighted codes are Excess-3 code and Gray code.

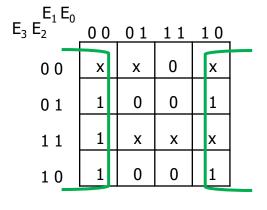

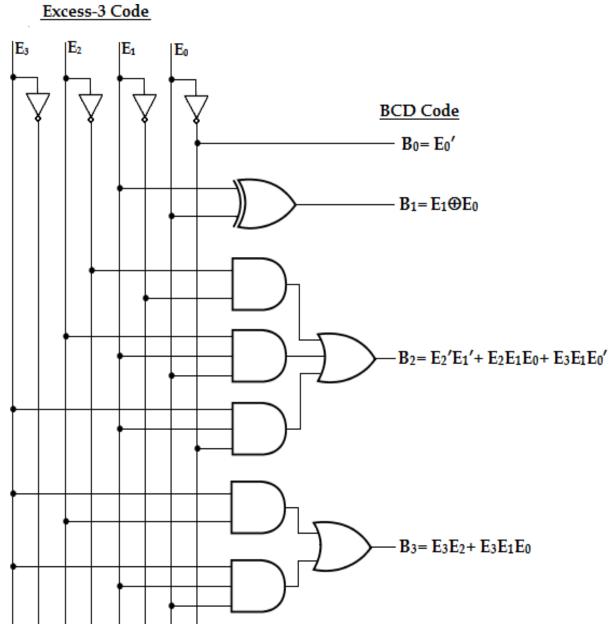

#### Excess-3 code

The Excess-3 code is also called as XS-3 code. It is non-weighted code used to express decimal numbers. The Excess-3 code words are derived from the 8421 BCD code words adding 00112 or 3 10 to each code word in 8421. The excess-3 codes are obtained as follows –

| Decimal | BCD     | Excess-3   |  |  |  |

|---------|---------|------------|--|--|--|

|         | 8421    | BCD + 0011 |  |  |  |

| 0       | 0 0 0 0 | 0011       |  |  |  |

| 1       | 0 0 0 1 | 0 1 0 0    |  |  |  |

| 2<br>3  | 0 0 1 0 | 0 1 0 1    |  |  |  |

| 3       | 0 0 1 1 | 0 1 1 0    |  |  |  |

| 4       | 0 1 0 0 | 0 1 1 1    |  |  |  |

| 5       | 0 1 0 1 | 1000       |  |  |  |

| 6       | 0 1 1 0 | 1001       |  |  |  |

| 7       | 0 1 1 1 | 1 0 1 0    |  |  |  |

| 8       | 1000    | 1 0 1 1    |  |  |  |

| 9       | 1001    | 1 1 0 0    |  |  |  |

#### Gray Code

It is the non-weighted code and it is not arithmetic codes. That means there are no specific weights assigned to the bit position. It has a very special feature that, only one bit will change each time the decimal number is incremented as shown in fig. As only one bit changes at a time, the gray code is called as a unit distance code. The gray code is a cyclic code. Gray code cannot be used for arithmetic operation.

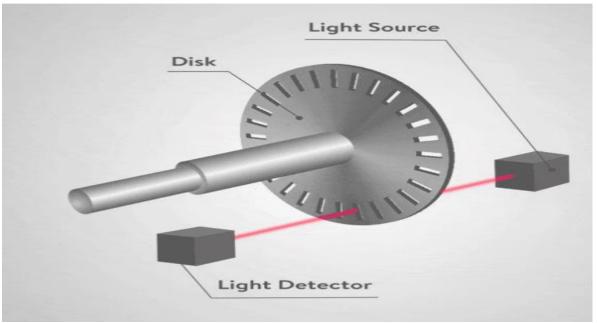

# Application of Gray code

Gray code is popularly used in the shaft position encoders.

A shaft position encoder produces a code word which represents the angular position of the shaft

| Decimal | BCD     | Gray    |  |  |  |  |

|---------|---------|---------|--|--|--|--|

| 0       | 0 0 0 0 | 0 0 0 0 |  |  |  |  |

| 1       | 0001    | 0 0 0 1 |  |  |  |  |

| 2       | 0 0 1 0 | 0 0 1 1 |  |  |  |  |

| 3       | 0 0 1 1 | 0 0 1 0 |  |  |  |  |

| 4       | 0 1 0 0 | 0 1 1 0 |  |  |  |  |

| 5       | 0 1 0 1 | 0 1 1 1 |  |  |  |  |

| 6       | 0 1 1 0 | 0 1 0 1 |  |  |  |  |

| 7       | 0 1 1 1 | 0 1 0 0 |  |  |  |  |

| 8       | 1000    | 1 1 0 0 |  |  |  |  |

| 9       | 1001    | 1 1 0 1 |  |  |  |  |

#### 3.3 Binary Coded Decimal BCD code

In this code each decimal digit is represented by a 4-bit binary number. BCD is a way to express each of the decimal digits with a binary code. In the BCD, with four bits we can represent sixteen numbers 0000to1111. But in BCD code only first ten of these are used 0000to1001. The remaining six code combinations i.e. 1010 to 1111 are invalid in BCD

| Decimal | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    |

|---------|------|------|------|------|------|------|------|------|------|------|

| BCD     | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 |

#### Advantages of BCD Codes

It is very similar to decimal system.

We need to remember binary equivalent of decimal numbers 0 to 9 only.

#### Disadvantages of BCD Codes

The addition and subtraction of BCD have different rules. The BCD arithmetic is little more complicated.

BCD needs more number of bits than binary to represent the decimal number. So BCD is less efficient than binary.

#### 3.4 Alphanumeric codes

- A binary digit or bit can represent only two symbols as it has only two states '0' or '1'. But this is not enough for communication between two computers because there we need many more symbols for communication. These symbols are required to represent 26 alphabets with capital and small letters, numbers from 0 to 9, punctuation marks and other symbols.

- The alphanumeric codes are the codes that represent numbers and alphabetic characters. Mostly such codes also represent other characters such as symbol and various instructions necessary for conveying information. An alphanumeric code should at least represent 10 digits and 26 letters of alphabet i.e. total 36 items. The following three alphanumeric codes are very commonly used for the data representation.

- American Standard Code for Information Interchange ASCII.

- Extended Binary Coded Decimal Interchange Code EBCDIC.

- Five bit Baudot Code.

- ASCII code is a 7-bit code whereas EBCDIC is an 8-bit code. ASCII code is more commonly used worldwide while EBCDIC is used primarily in large IBM computers.

# 3.5 Error Detecting and Correcting Codes

#### Error Detection

- Error detection means to decide whether the received data is correct or not without having a copy of the original message.

- Error detection uses the concept of redundancy, which means adding extra bits for detecting errors at the destination.

#### Error Codes

- Parity method of error detection

- Hamming code for error detection and correction

# 3.5.1 Parity Method for Error Detection

- Any group of bit contain either an even or an odd number of 1s.

- A parity bit is attached to a group of bits to make the total number of 1s in a group always even or always odd.

- An even parity bit makes the total number of 1s even, and an odd parity bit makes the total odd.

- The parity bit can be attached to the code at either the beginning or the end, depending on system design.

- The total number of 1s, including the parity bit, is always even for even parity and always odd for odd parity.

### 3.5.2 Hamming Code

- In the Hamming code, P parity bits are added to an m -bit data word, forming a new word of m + P bits.

- The bit positions are numbered in sequence from 1 to m + P.

- Those positions numbered as a power of 2 are reserved for the parity bits.

- The remaining bits are the data bits.

- The code can be used with words of any length.

#### 3.5.2.1 Single-bit error detection

- To correct an error, the receiver reverses the value of the altered bit. To do so, it must know which bit is in error.

- Number of redundancy (parity) bits needed

- Let data bits = m

- Parity bits = P

- Total message sent = m + p

- The value of P must satisfy the following relation:

#### 2<sup>P</sup>≥ m+P+1

- The parity bits, P1, P2, P4, and P8, are in positions 1, 2, 4, ... respectively (2<sup>0</sup>, 2<sup>1</sup>, 2<sup>2</sup>, ...)

- The data bits are in the remaining positions.

- Each parity bit is calculated as follows:

- P1 = XOR of bits (3, 5, 7, 9, 11)

- P2 = XOR of bits (3, 6, 7, 10, 11)

- P4 = XOR of bits (5, 6, 7, 12)

- P8 = XOR of bits (9, 10, 11, 12)

- Exclusive-OR operation

- I for an odd number of 1's (Error)

- =0 for an even number of 1's (No Error)

- Each parity bit is set so that the total number of 1's in the checked positions, including the parity bit, is always even

#### 3.5.2.2 Single-Bit Error Correction

#### Error Correction

It can be handled in two ways:

1)Receiver can have the sender retransmit the entire data unit.

2)Receiver can use an error-correcting code, which automatically corrects certain errors.

- To correct an error, the receiver reverses the value of the altered bit.

- To do so, it must know which bit is in error.

- Number of redundancy (parity) bits needed

- Let data bits = m

- Parity bits = P

- Total message sent = m + P

- The value of P must satisfy the following relation:

#### 2<sup>P</sup>≥ m+P+1

Each parity bit is calculated as follows:

- P1 = XOR of bits (3, 5, 7, 9, 11)

P2 = XOR of bits (3, 6, 7, 10, 11)

P4 = XOR of bits (5, 6, 7, 12)

P8 = XOR of bits (9, 10, 11, 12)

- The check bits are evaluated as follows:

- ✤ C1 = XOR of bits (1, 3, 5, 7, 9, 11)

- ♥ C2 = XOR of bits (2, 3, 6, 7, 10, 11)

(XOR is done along with the Parity bit received)

### **Examples**

Hamming Error Detecting and Correcting Codes

1. Encode the data bit 1101 using Hamming Error correcting and Detecting codes.

Step 1 : To find the number of Parity bits required.  $2^{p} >= m+P+1$  m=4Let p=2 2<sup>2</sup> = 4 m+P+1 = 4+2+1 =7

Let P=3 2<sup>3</sup> = 8 m+P+1 = 4+3+1 =8

Now 2<sup>p</sup> = m+P+1

3 -parity bits are enough to transmit 4-bit data.

Total bits =m+P =4 +3 =7

Step2: Construct a Bit location table:

Parity Bit = 2<sup>0</sup>, 2<sup>1</sup>, 2<sup>2</sup>

|                     | P1  | P2  | D1  | P3                | D2                | D3                | D4                 |

|---------------------|-----|-----|-----|-------------------|-------------------|-------------------|--------------------|

| <b>Bit Position</b> | 1   | 2   | 3   | 4                 | 5                 | 6                 | 7                  |

| Binary              | 001 | 010 | 011 | <mark>1</mark> 00 | <mark>1</mark> 01 | <mark>11</mark> 0 | 1 <mark>1</mark> 1 |

| Position            |     |     |     |                   |                   |                   |                    |

| Number              |     |     |     |                   |                   |                   |                    |

| Data Bits           |     |     | 1   |                   | 1                 | 0                 | 1                  |

| Parity Bits         | 1   | 0   |     | 0                 |                   |                   |                    |

| 7-bit               | 1   | 0   | 1   | 0                 | 1                 | 0                 | 1                  |

| Hamming             |     |     |     |                   |                   |                   |                    |

| code                |     |     |     |                   |                   |                   |                    |

2. A hamming code is received as 1010111. Determine the correct code when even parity is used.

- Step1: Construct a Bit location table:

- Parity Bit = 2<sup>0</sup>, 2<sup>1</sup>, 2<sup>2</sup>

|                              | P1                | P2                 | D1                 | P3                | D2                        | D3          | D4  |

|------------------------------|-------------------|--------------------|--------------------|-------------------|---------------------------|-------------|-----|

| Bit Position                 | 1                 | 2                  | 3                  | 4                 | 5                         | 6           | 7   |

| Binary<br>Position<br>Number | 00 <mark>1</mark> | 0 <mark>1</mark> 0 | 0 <mark>1</mark> 1 | <mark>1</mark> 00 | <b>1</b> 0 <mark>1</mark> | <b>11</b> 0 | 111 |

| Received code                | 1                 | 0                  | 1                  | 0                 | 1                         | 1           | 1   |

| Corrected code               | 1                 | 0                  | 1                  | 0                 | 1                         | 0           | 1   |

Step 2: Find the Error Bit

Checking for Even Parity

- E1 (P1) ------ 1, 3, 5, 7----- 1 1 1 1 1 ----- No Error 0 (LSB)

- E2 (P2) ------ 2, 3, 6, 7----- 0 1 1 1 ----- Error ---1

- E3 (P3) ------ 4,5,6,7----- 0 1 1 1 ----- Error ---1 (MSB)

Error Bit -----110

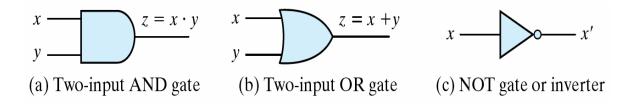

# 4.Binary Logic – The Logic Gates

#### Graphic Symbols and Input-Output Signals for Logic gates:

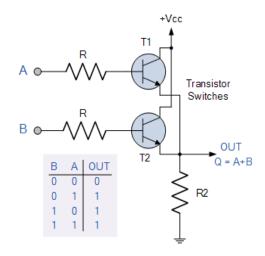

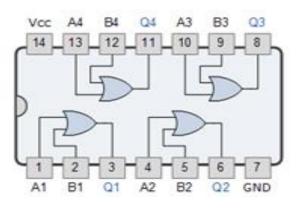

- The OR gate IC which has 4 (Quad) OR gates is shown below.

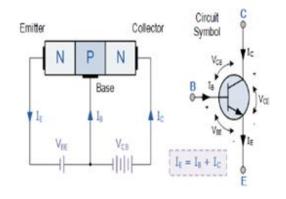

- The OR gate in its circuit form has 2 NPN transistors as the logic switches

- The NPN transistor is also shown separately

# 2-Input Logic OR Gate

| Symbol                     | Truth Table            |   |   |  |

|----------------------------|------------------------|---|---|--|

|                            | В                      | A | Q |  |

| Ac                         | 0                      | 0 | 0 |  |

| Bo 21 OQ                   | 0                      | 1 | 1 |  |

| 2-input OR Gate            | 1                      | 0 | 1 |  |

|                            | 1                      | 1 | 1 |  |

| Boolean Expression Q = A+B | Read as A OR B gives Q |   |   |  |

2-input Transistor OR Gate

### IC 7432 Quad 2-input Logic OR Gate

#### NPN structure of a Transistor in OR Gate

# **5. DIGITAL LOGIC FAMILIES**

# Integrated circuits

Integrated Circuits are used for producing several different circuit configurations and production technologies. The semiconductor chip consists of electronic components used for constructing circuits. Integrated circuits are classified into

Linear Integrated Circuits

Digital Integrated Circuits

Both operate with continuous and discrete signals respectively and are used to construct various electronic circuits.

There are different levels of Integration, based on the number of logic gates in a single IC package.

Small scale Integration (SSI)

These IC's contain fewer logic gates (0 to 10). The input and output pins can be directly connected to the pins in the package.

Medium Scale Integration (MSI)

These IC's have approximately around 10 to 1000 gates in one package, which performs some specific functions.

(Ex: adders, multiplexers)

Large Scale Integration (LSI)

These IC's contain thousands of gates in a single package.

(Ex: processors, memory chips and programmable logic devices)

Very Large Scale Integrated Devices (VLSI)

These IC's contain hundreds of thousands of gates in a single package.

(Ex: memory arrays, computer chips)

#### Classification of Logic Families

Based on the circuit technology digital IC's are classified into various types

- RTL (Resistor Transistor Logic)

- DTL (Diode Transistor Logic)

- TTL (Transistor Transistor Logic)

- ECL (Emitter Coupled Logic)

- MOS (Metal Oxide Semiconductor Logic)

#### Characteristics of Logic Families

The following are the important characteristics of digital IC's

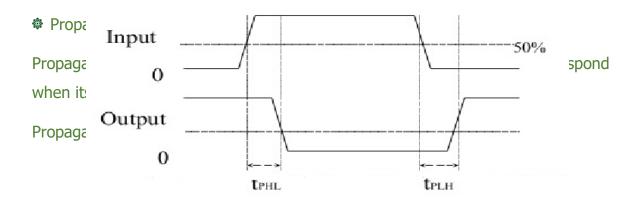

- Propagation Delay (or) Operating Speed

- Voltage and Current parameters

- Power Dissipation

- Fan-in

- Fan-out

- Noise Margin

- Operating Temperature

- Power Supply Requirements

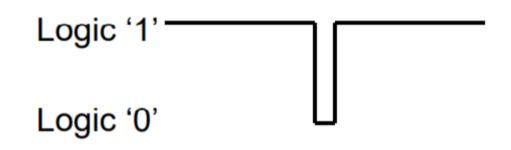

$t_{PLH}$ : Propagation delay time from low level(0) to high level(1)

$t_{PHL}$ : Propagation delay time from high level(1) to low level(0)

The delay in output is a measure of relative speed of logic circuits.

Average propagation delay  $P_{D avg} = (t_{PLH} + t_{PHL})/2$

Voltage and Current Parameters:

Digital logic gates have a certain range of voltage and current levels

corresponding to 0(low level)) and 1(high level)

Voltage and current levels:

High level input voltage and current: The minimum input voltage recognised as logic 1(high level) by the logic gates (2V - 3V range) and the corresponding current is high level input current.

Low level input voltage and current: The maximum input voltage recognised as logic 0(low level) by the logic gates (around 0.8V) and the corresponding current is low level input current.

High level output voltage and current: The minimum voltage available at the output corresponding to logic 1 and the corresponding current is high level output current.

Low level output voltage and current: The minimum voltage available at the output corresponding to logic 0 and the corresponding current is low level output current.

Power Dissipation:

Power dissipation is the measure of power consumed by the logic gate when fully driven by all its inputs. It is expressed in milliwatts or nanowatts.

Average power dissipation  $P_{dc avg} = V_{cc} \times I_{avg}$

V<sub>cc</sub> - DC supply voltage

$I_{\mbox{\scriptsize avg}}$  – Average current taken from the supply

#### Fan-in:

Fan-in is the number of inputs available in a gate

Fan-out:

Fan-out is the number of similar logic gates that the output of a gate can drive without affecting the normal operation.

Noise Margin:

Noise margin is the maximum external noise voltage added to the input signal that does not cause any undesirable change in the circuit operation.

Operating Temperature:

All integrated circuits are semiconductor devices sensitive to temperature

- Operating range

- 0°C to +70° for consumer applications

- -55° to +125°C for military applications

Power Supply Requirements:

The amount of power required by the IC.

#### **\$ 5.1 RESISTOR TRANSISTOR LOGIC (RTL)**

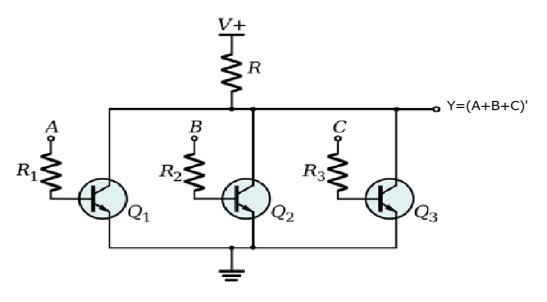

The following diagram shows the Resistor Transistor Logic (RTL) of NOR logic function.

Basic diagram of RTL NOR consists of transistor and resistors.

Here it is three input NOR gates logic diagram using RTL [i.e., A, B, C].

This follows the NOR gates truth table in its operation. i.e., whenever any one of the input is "HIGH" then it produce low output (or) all inputs are low, it produces "Low" output. This is similar to NOR logic truth table shown below.

| INF | OUTPUT |          |

|-----|--------|----------|

| A   | В      | Y=(A+B)' |

| 0   | 0      | 1        |

| 0   | 1      | 0        |

| 1   | 0      | 0        |

| 1   | 1      | 0        |

#### Operation:

When all inputs are zero (or) low, then output Q = 0.

Since, all these transistors Q1, Q2, Q3 are in OFF condition; its collector output is high.

When any one of the input is high (ort all inputs are high, then its corresponding transistor is going to ON condition. Also, it is connected with ground and collector potential which is approximately zero.

Anyhow, the base current is practically independent of the emitter junction characteristic. When the resistors increase the input resistance and reduce the switching speed of the circuit. This reduces the rise and fall times of any input pulse.

In practice, this approach to increase the speed of an RTL is to connect a capacitor called a speed-up capacitor which is parallel to resistance connected in base.

Operation Table

|   | Inputs |        |          | Transistor Status |           |            |  |

|---|--------|--------|----------|-------------------|-----------|------------|--|

| Α | В      | С      | Q1 Q2 Q3 |                   | Q3        | (Y=A+B+C)' |  |

| 0 | 0      | 0      | OFF      | OFF               | OFF       | 1(HIGH)    |  |

| 1 | 0 or 1 | 0 or 1 | ON       | ON or OFF         | ON or OFF | 0(LOW)     |  |

#### Drawbacks:

In this logic family, some disadvantages are there, they are:

(i) It reduces current-hogging by load transistors, which is purely because of mismatch of junction voltages. Hence it permits large fan-out.

(ii) One more problem is that load transistor in a RTL gate are driven heavily into saturation. Hence it results in long-turn-off delays.

Characteristics of RTL Family

1. Speed of operation is low, i.e., Propagation delay is of the order 500 ns. Hence it cannot operate the system speed above 4 MHz.

2. For switching delay of 50 ns, the fan-in is 4 (or) 5 and fan-out is 4.

3. Because of Base resistor in transistor, the power dissipation is more. This can be reduced by introducing DCTL (Direct coupled transistor logic).

4. It is highly sensitive to temperature.

5. Poor in nose immunity

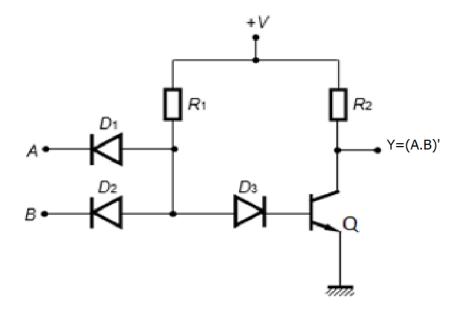

#### **5.2 DIODE TRANSISTOR LOGIC (DTL)**

This DTL logic family reduces the problem of decreasing output voltage with increasing load.

The following diagram shows the DTL NAND logic circuit using diode and transistor.

- A and B are the inputs.

- D1 D2 forms AND equivalent circuit and transistor (Q) acts as a inverter. Therefore, the combinations of AND and NOT gates forms a logical NAND circuit hence it follows the following NAND truth table.

| INF | OUTPUT |          |

|-----|--------|----------|

| A   | В      | Y=(A.B)' |

| 0   | 0      | 1        |

| 0   | 1      | 1        |

| 1   | 0      | 1        |

| 1   | 1      | 0        |

Operation:

As per the above circuit diagram, the operation is as follows:

When A = B = 1

Diodes D1 D2 are in reverse biased conditions [i.e., acts as open circuit].

Therefore D3 conduct. Hence the transistor base gets current flow and which is turned ON.

Q output in low cut-off

When A = B = 0 (or) A = 0 and B = \* (0 or 1)

When all inputs are zero, the D1 and D2 is in ON condition. Hence there is no input current to base of the transistor. Q, hence it is in OFF condition. Thereby the output in collector terminal of transistor Q is high, called saturated state.

Similarly if any one of the input is low (0) that makes the above operation. So output is high (1)

Therefore, the final expression is Y = (A.B)' Then above operation is tabulated by using functional operation table

#### Operation table

| Inputs |   |     | Device | Output |     |          |

|--------|---|-----|--------|--------|-----|----------|

| Α      | В | D1  | D2     | D3     | Q   | (Y=A.B)' |

| 0      | 0 | ON  | ON     | OFF    | OFF | 1(HIGH)  |

| 0      | 1 | ON  | OFF    | OFF    | OFF | 1(HIGH)  |

| 1      | 0 | OFF | ON     | OFF    | OFF | 1(HIGH)  |

| 1      | 1 | OFF | OFF    | ON     | ON  | 0(LOW)   |

#### Characteristics of DTL Family

Propagation Delay:

The turn-off delay is considerably more than the turn-on-delay. Hence propagation delay is 25 ns.

Fan-in and Fan-out.

Fan-in is less than 8.

Fan-out is high i.e., upto 8.

Noise immunity:

Noise margin is high. This is due to the additional diodes.

Anyhow, whatever the drawbacks, can be reduced (or) improved in TTL family.

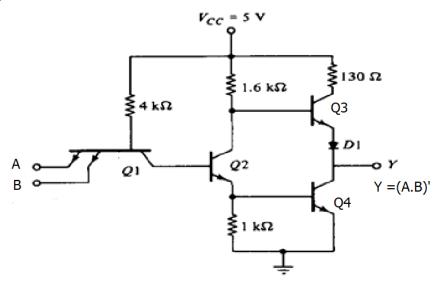

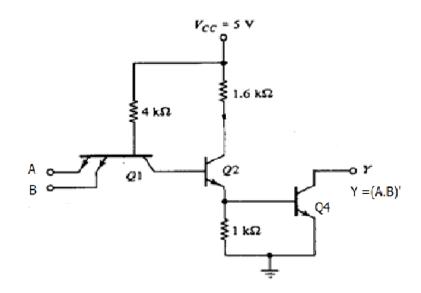

#### **5.3 TRANSISTOR TRANSISTOR LOGIC (TTL)**

The speed limitation of DTL is overcome by TTL family. It is the commonly used saturating family and hence operating speed is high.

Basic gate for TTL logic is NAND gate

#### 2-Input TTL NAND Gate

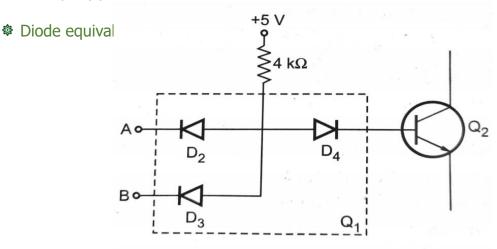

The figure shows the circuit diagram of 2-input NAND gate. Its input structure consists of multiple-emitter transistor and output structure consists of totem-pole output. Here, Q1 is an NPN transistor having two emitters, one for each input to the gate. Although this circuit looks complex, we can simplify its analysis by using the diode equivalent of the multiple-emitter transistor Q1, as shown in figure. Diodes D2 and D3 represent the two E-B junctions of Q1 an d4 is the collector-base (C-B) junction

- The input voltages A and B are either LOW (ideally grounded) or HIGH (ideally + 5 volts). If either A or B or both are low, the corresponding diode conducts and the base of Q1 is pulled down to approximately 0.7 V. This reduces the base voltage of Q2 to almost zero. Therefore, Q2 cuts off. With Q2 open, Q4 goes into cut-off and the Q3 base is pulled HIGH. Since Q3 acts as an emitter follower, the Y output is pulled up to a HIGH voltage. On the other hand, when A and B both are HIGH, the emitter diode of Q1 are reversed biased making them off. This causes the collector diode D4 to go into forward conduction. This forces Q2 base to go HIGH. In turn, Q4 goes into saturation producing a low output.

- Without diode D1 in the circuit, Q3 will conduct slightly when the output is low. To prevent this diode is used; its voltage keeps the base-emitter diode of Q3 revere biased only Q4 conducts when output is low.

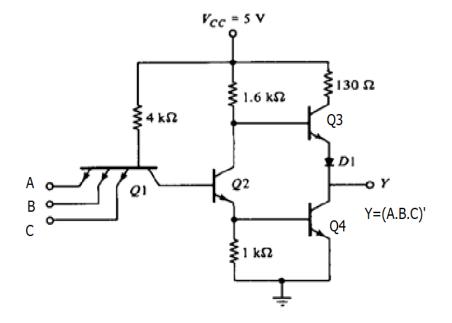

- 3-input TTL NAND Gate

The figure shows the three input TTL NAND gate. The operation of three input TTL NAND is same as that of two output TTL NAND gate except that is Q1 (NPN) transistor has three emitters instead of two. For three input NAND gate if all the inputs are logic 1 then and then only output is logic 0; otherwise output is logic 1. The operation is similar to the 2-input NAND gate. The table show the truth table for 3-input NAND gate.

|   | Inputs |        |     | Dev | Output |     |            |

|---|--------|--------|-----|-----|--------|-----|------------|

| A | В      | С      | Q1  | Q2  | Q3     | Q4  | (Y=A.B.C)' |

| 0 | 0      | 0      | ON  | OFF | ON     | OFF | 1(HIGH)    |

| 0 | 0 or 1 | 0 or 1 | ON  | OFF | ON     | OFF | 1(HIGH)    |

| 1 | 1      | 1      | OFF | ON  | OFF    | ON  | 0(LOW)     |

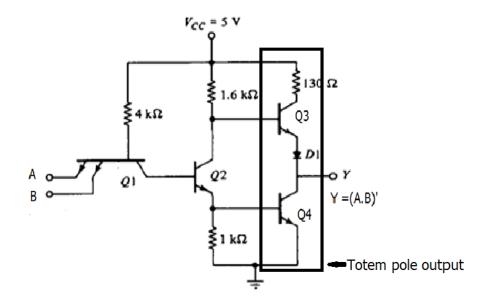

#### Totem-Pole Output

- The figure shows a highlighted output configuration.

- Transistor Q3 and Q4 form a totem-pole. Such a configuration is known as active pull-up or totem pole output.

- The active pull-up formed by Q3 and Q4 has specific advantage.

- Totem-pole transistors are used because they produce LOW output impedance

- Either Q3 acts as a emitter follower (HIGH output) or Q4 is saturated (LOW output)

- When Q3 is conducting, the output impedance is approximately 70Ω; when Q4 is saturated, the output impedance is only 12Ω.

- Either way, the output impedance is low. This means that the output voltage can change quickly from one state to the other because any stray output capacitance is rapidly charged or discharged through the low output impedance. Thus the propagation delay is low in totem-pole TTL logic.

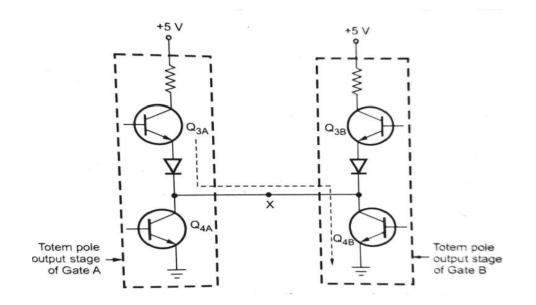

- Open-Collector Output

- One problem with totem pole output is that two outputs cannot be tied together. See the figure, where the totem pole outputs of two separate gates are connected together at point X. Suppose that the output of gate A is high (Q3A ON and Q4A OFF) and the output of gate B is low (Q3B OFF and Q4B ON). In this situation transistor Q4B acts as a load for Q3A. Since Q4B is a low resistance load, it draws high current around 55 mA. This current might not damage Q3A or Q4B immediately, but over a period of time can cause overheating and deterioration in performance and eventual device failure.

Some TTL devices provide another type of output called open collector output. The outputs of two difference gates with open collector output can be tied together. This known as wired logic. Figure shows a 2-input NAND gate with an open-collector output eliminates the pull-up transistor Q3, D1 and R4. The output is taken from the open collector terminal of transistor Q4.

Because the collector of Q4 is open, a gate like this will not work properly until you connect an external pull-up resistor, as shown in fig. When Q4 is ON, output is low and when Q4 is OFF output is tied to VCC through an external pull up resistor.

#### Comparison between Totem-Pole and Open-Collector Outputs

| Totem-pole                                                                                           | Open collector                                                      |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Output stage consists of pull-up transistor<br>(Q3), diode resistor and pull-down<br>transistor (Q4) | Output stage consists of only pull-down transistor.                 |

| External pull-up resistor is not required.                                                           | External pull-up resistor is required for proper operation of gate. |

| Output of two gates cannot be tied together.                                                         | Output of two gates can be tied together using wired AND technique. |

| Operating speed is high.                                                                             | Operating speed is low.                                             |

- Table summarizes the difference between totem-pole and open collector outputs.

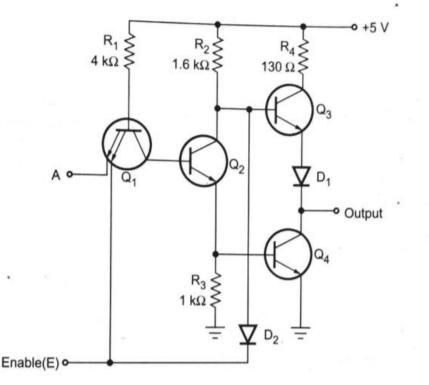

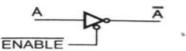

- Tri-Slate TTL Inverter

- The tristate configuration is a third type of TTL output configuration. It utilizes the high-speed operation of the totem-pole arrangement while permitting outputs to be wired-ANDed (connected together). It is called tristate TTL because it allows three possible output stages: HIGH, LOW and high impedance. We know the transistor Q3 is ON when output is HIGH and Q4 is ON when output is LOW. In the high impedance state both transistors, transistors Q3 and Q4 in the totem-pole arrangement are turned OFF. As a result, the output is open or floating, it is neither LOW nor HIGH.

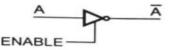

Logic symbol for active high enable input

The figure shows the simplified circuit for tristate inverter. It has two inputs A and E.

A is the normal logic output whereas E is an ENABLE input. When ENABLE input ٢ is HIGH, the circuit works as a normal inverter. Because when E is HIGH, the state of the transistor Q1 (either ON or OFF) depends on the logic input A, and the additional component diode is open circuited as its cathode is at logic HIGH. When ENABLE input is LOW, regardless of the state of logic input A, the base-emitter junction of Q1 is forward biased and as a result it turns ON. This shunts the current through R1 away from Q2 making it OFF. As Q2 is OFF, there is no sufficient drive for Q4 to conduct and hence Q4 turns off. The LOW at ENABLE input also forward-biases diode D2 which shunt the current away from the base of Q3, making it OFF. In this way, when ENABLE input is LOW, both transistors are OFF and output is at high impedance state. Fig shows the logic symbols for tristate inverter. In above case circuit operation is enabled when ENABLE input is HIGH. Therefore, ENBLE input is active high. The logic symbol for high enable input is shown in figure. In some circuits ENABLE input can be active LOW, i.e. circuit operates when ENABLE input is LOW. The logic symbol for active low ENABLE input is shown in the figure.

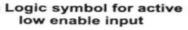

The internal temperature – and voltage -compensated bias network supplies a reference voltage (Bias voltage  $V_{BB} = -1.3$  V) to the differential amplifier. The best noise immunity is obtained by connecting  $V_{CC}$  to ground and  $V_{EE}$  to -5.2 V.

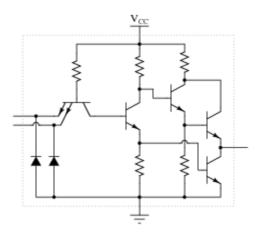

#### 5.4 ECL – Emitter coupled logic:

Emitter Coupled Logic (ECL) is a non saturated digital logic family. It achieves the propagation delay of 2ns. Its required high speed system operation. The output provides both OR and NOR functions. Each input is connected to the base of transistor. The two voltage levels are about -0.8 V for the high state and -1.8V for the low state.

#### The circuit consists of

- Differential amplifier

- Temperature and voltage -compensated bias network

- Emitter follower

- The Emitter follower output requires a pull down resistor for current to flow. This is obtained from the input resistor, R<sub>p</sub> of other similar gates or from an external resistor connected to a negative voltage supply.

Working:

- If any of the input is high the corresponding input transistor is turned ON and transistor Q<sub>3</sub> is OFF.

- Ex: if V<sub>A</sub> = -0.8V, the transistor Q<sub>1</sub> starts conducting, So the V<sub>BE</sub>(Q<sub>1</sub>) = 0.8V. Now  $V_{E}(Q1) = V_{A} V_{BE}(Q_{1}) = -0.8V 0.8V = -1.6V$

- ✤ Next to find the V<sub>BE</sub>(Q<sub>3</sub>). V<sub>BE</sub>(Q<sub>3</sub>) = V<sub>B</sub>(Q<sub>3</sub>) V<sub>E</sub>(Q<sub>3</sub>) = -1.3 -(-1.6) =0.3V. Thus the transistor Q<sub>3</sub> is OFF. So the transistor Q<sub>1</sub> is remains ON. The output voltage of the transistor Q1 is low. So the input voltage of transistor Q6 is Low. Since the transistor Q6 is a Emitter follower so the output of the transistor Q6 is also Low. This output produce the NOR output of the circuit.

- The transistor Q<sub>3</sub> is OFF. The output voltage of the transistor Q3 is high. So the input voltage of transistor Q5 is high. Since the transistor Q5 is a Emitter follower so the output of the transistor Q5 is also high. This output produce the OR output of the circuit.

- 2. If both the inputs are low, transistors Q1 and Q2 are turned OFF and transistor  $Q_3$  is ON.

- Ex: if V<sub>A</sub> = V<sub>B</sub> = -1.8V, the transistor Q<sub>1</sub> and Q<sub>2</sub> = OFF, the transistor Q<sub>3</sub> is ON. So the V<sub>BE</sub>(Q<sub>3</sub>) = 0.8V. Now V<sub>E</sub>(Q<sub>3</sub>) = V<sub>BB</sub> V<sub>BE</sub>(Q<sub>1</sub>) = -1.3V 0.8V = -2.1V

- Next to find the  $V_{BE}(Q_1)$  or  $V_{BE}(Q_2)$ .  $V_{BE}(Q_1) = V_B(Q_1) V_E(Q_1) = -1.8 (-2.1) = 0.3V$ . Thus the transistor  $Q_1$  is OFF. So the transistor  $Q_3$  is remains ON. The output voltage of the transistor  $Q_3$  is low. So the input voltage of transistor  $Q_3$  is Low. Since the transistor Q5 is a Emitter follower so the output of the transistor Q5 is also Low. This output produce the OR output of the circuit.

- The transistor Q<sub>1</sub> is OFF. The output voltage of the transistor Q1 is high. So the input voltage of transistor Q6 is high. Since the transistor Q6 is a Emitter follower so the output of the transistor Q6 is also high. This output produce the NOR output of the circuit.

#### Operation Table

| INPUT |       | Q1  | Q2  | Q3  | Q5  | Q6  | NOR<br>OUTPUT | OR<br>OUTPUT |

|-------|-------|-----|-----|-----|-----|-----|---------------|--------------|

| VA    | VB    |     |     |     |     |     |               |              |

| -1.8V | -1.8V | OFF | OFF | ON  | OFF | ON  | HIGH          | LOW          |

| -1.8V | -0.8V | OFF | ON  | OFF | ON  | OFF | LOW           | HIGH         |

| -0.8V | -1.8V | ON  | OFF | OFF | ON  | OFF | LOW           | HIGH         |

| -0.8V | -0.8V | ON  | ON  | OFF | ON  | OFF | LOW           | HIGH         |

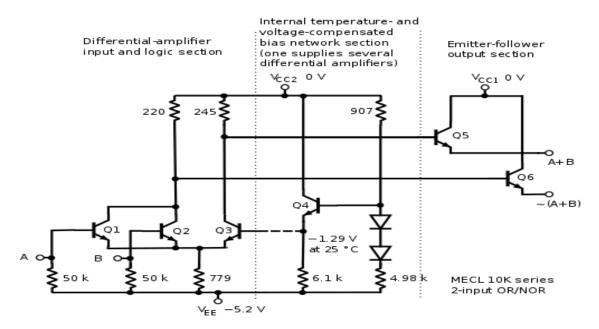

#### 5.5 CMOS Families

- Complementary MOS (CMOS) logic uses the MOSFET in complementary pairs as its basic element.

- A complementary pair uses both *p*-channel and *n*-channel enhancement MOSFETs

- CMOS AS INVERTER

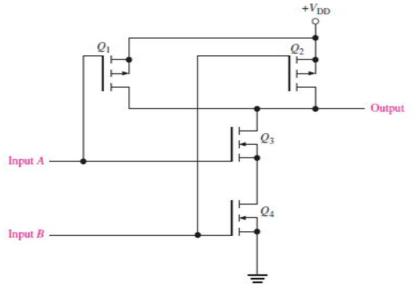

#### CMOS AS NAND LOGIC

- When both inputs are LOW, Q1 and Q2 are on, and Q3 and Q4 are off.

- The output is pulled HIGH through the *on* resistance of Q1 and Q2 in parallel.

- When input A is LOW and input B is HIGH, Q1 and Q4 are on, and Q2 and Q3 are off.

| Α            | В            | Q1   | Q2   | Q3   | Q4   | Y |

|--------------|--------------|------|------|------|------|---|

| (Q1 &<br>Q3) | (Q2 &<br>Q4) | PMOS | PMOS | NMOS | NMOS |   |

| 0            | 0            | ON   | ON   | OFF  | OFF  | 1 |

| 0            | 1            | ON   | OFF  | OFF  | ON   | 1 |

| 1            | 0            | OFF  | ON   | ON   | OFF  | 1 |

| 1            | 1            | OFF  | OFF  | ON   | ON   | 0 |

- The output is pulled HIGH through the low *on* resistance of *Q*1.

- When input A is HIGH and input B is LOW, Q1 and Q4 are off, and Q2 and Q3 are on.

- The output is pulled HIGH through the low *on* resistance of  $Q^2$ .

- When both inputs are HIGH, *Q*1 and *Q*2 are off, and *Q*3 and *Q*4 are on.

- The output is pulled LOW through the *on* resistance of *Q*3 and *Q*4 in series to ground.

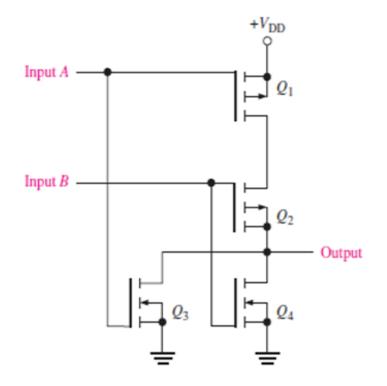

#### CMOS AS NOR LOGIC

- When both inputs are LOW, Q1 and Q2 are on, and Q3 and Q4 are off.

- The output is pulled HIGH through the *on* resistance of Q1 and Q2 in series.

| Α            | В            | Q1   | Q2   | Q3   | Q4   | Y |

|--------------|--------------|------|------|------|------|---|

| (Q1 &<br>Q3) | (Q2 &<br>Q4) | PMOS | PMOS | NMOS | NMOS |   |

| 0            | 0            | ON   | ON   | OFF  | OFF  | 1 |

| 0            | 1            | ON   | OFF  | OFF  | ON   | 0 |

| 1            | 0            | OFF  | ON   | ON   | OFF  | 0 |

| 1            | 1            | OFF  | OFF  | ON   | ON   | 0 |

- When input A is LOW and input B is HIGH, Q1 and Q4 are on, and Q2 and Q3 are off.

- The output is pulled LOW through the low *on* resistance of *Q*<sup>4</sup> to ground.

- When input A is HIGH and input B is LOW, Q1 and Q4 are off, and Q2 and Q3 are on.

- The output is pulled LOW through the *on* resistance of *Q*<sup>3</sup> to ground.

- When both inputs are HIGH, *Q*1 and *Q*2 are off, and *Q*3 and *Q*4 are on. The output is

- pulled LOW through the *on* resistance of *Q*3 and *Q*4 in parallel to ground.

### **Comparison between Various Digital Logic Families**

| Parameter                                 | RTL                            | DTL                                 | TTL                                  | ECL                                                                      | CMOS                                                                               |

|-------------------------------------------|--------------------------------|-------------------------------------|--------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Components<br>used                        | Resistors<br>and<br>transistor | Resistor<br>diode and<br>transistor | Resistor,<br>diode and<br>transistor | Resistor and<br>transistor                                               | N-channel<br>and P-<br>channel<br>MOSFET                                           |

| Circuit<br>Complexity                     | Simple                         | Moderate                            | Complex                              | Complex                                                                  | Moderate                                                                           |

| Noise<br>margin<br>[Noise<br>immunity]    | Nominal                        | Good                                | Very good                            | Good                                                                     | Very good                                                                          |

| Fan-out                                   | Low<br>(4)                     | Medium<br>(8)                       | More<br>(10)                         | High<br>(25)                                                             | 50                                                                                 |

| Power<br>dissipation<br>in mW per<br>gate | 12                             | 8 – 12                              | 10                                   | 40 – 55                                                                  | 0.1                                                                                |

| Basic gate                                | NOR                            | NAND                                | NAND                                 | OR-NOR                                                                   | NAND/NOR                                                                           |

| Propagation<br>delay in ns                | 12                             | 30                                  | 10                                   | 2 (ECL 10 K)<br>0.75 (ECL<br>100K)                                       | 70                                                                                 |

| Speed<br>power<br>product (PJ)            | 144                            | 300                                 | 100                                  | 100 (ECL 10 K)<br>40 (ECL 100 K)                                         | 0.7                                                                                |

| Applications                              | Absolute                       | Absolute                            | Laboratory<br>instruments            | High speed<br>switching<br>applications<br>(low<br>propagation<br>delay) | Portable<br>instrument<br>with battery<br>supply (low<br>power<br>consumption<br>) |

| Number of<br>functions                    | High                           | Fairly high                         | Very high                            | High                                                                     | Low                                                                                |

| Clock rate<br>MHz                         | 8                              | 12 – 30                             | 15 – 60                              | 60 – 400                                                                 | 5                                                                                  |

#### 9. Lecture Notes

#### E-Books

Digital Fundamentals\_ Global Ed - Thomas L Floyd Digital Principles And Application - Leach & Malvino Digital Design - M. Morris Mano and Michael D. Ciletti Fundamentals of Digital Logic with Verilog Design-Stephen Brown and Zonko Vranesic

#### ONLINE LEARNING MATERIALS:

- 1:http://nptel.iitm.ac.in/ video.php? subject Id=117106086

- 2:http://nptel.iitm.ac.in/courses/117101001

- 3: https://youtu.be/C-oAyXibnJU

- **4** https://youtu.be/oYRMYSIVj1o

- 5: https://www.youtube.com/watch?v=XZmGGAbHqa0

- 6:https://www.youtube.com/watch?v=KymIDyQiXZI

#### Video Links

https://drive.google.com/open?id=1qCP5dBvi1LZxd6S7FAUxt788iMmLLpbg https://drive.google.com/open?id=1hrXWfXKWnhidFbnDPDtd75hQt9OzOG6O

#### 10. Assignments

- ✤ 1. Describe the procedure to get the Hamming code for the binary word 1101100.

- 2. A 12 bit Hamming code word containing 8 bits of data and 4 parity bits is read from memory. What was the original 8 bit data word that was written into memory if the 12 bit word read out is as (i) 101110010100 and (ii) 11111110100

- 3. The following is an internal schematic of a TTL logic gate. Analyse the transistor circuit and determine what type of gate (AND, OR, NAND, NOR, XOR, etc.) it is:

- A certain gate has a propagation delay of 5 ns and ICCH = 1 mA and ICCL = 2.5 mA with a dc supply voltage of 5 V. Determine the speed-power product.

- Draw the paths of all currents in this circuit with the input in a "low" state and in a high state:

## 11. Part A Q & A (with K level and CO)

| PART A                                                                                                                                                                                                                                                              |                 |     |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|--|--|--|--|--|

| Questions and Answers                                                                                                                                                                                                                                               | Blooms<br>Level | COs |  |  |  |  |  |

| 1. What is a binary number system ?<br>The number system with base (or radix) two is known as the binary<br>number system. Only two symbols are used to represent the<br>numbers in the system and these are 0 and 1.                                               | K1              | CO1 |  |  |  |  |  |

| 2. What is an Excess3 code?<br>The excess3 code is a non weighted code which is obtained from the<br>8-4-2-1 code by adding 3(0011) to each of the codes.                                                                                                           | K1              | CO1 |  |  |  |  |  |

| 3. What is the difference between analog and digital systems?<br>In a digital system the physical quantities or signals can assume only<br>discrete values, while in analog systems the physical quantities<br>or signals vary continuously over a specified range. | K1              | CO1 |  |  |  |  |  |

| 4. Subtract X = 1010100 and Y = 1000011 using 2's compliment $X = 1010100$ , 2's complement of Y = + 0111101 Sum = 10010001, Discard end carry, X - Y = 0010001                                                                                                     | К1              | CO1 |  |  |  |  |  |

| 5. Subtract X = 1010100 and Y = 1000011, using 1's complement.<br>X = 1010100, 1's complement of Y = $+$ 0111100<br>Sum = 10010000, End -around carry = $+$ 1, X - Y = 0010001                                                                                      | K1              | CO1 |  |  |  |  |  |

| 6. What is meant by parity bit?<br>A parity bit is an extra bit included with a message to make the total<br>number of 1's either even or odd.                                                                                                                      | K1              | CO1 |  |  |  |  |  |

| 7. Represent binary number 1101.101 in power of 2 and find its decimal equivalent<br>$N_3 = 1 \times 2^3 + 1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0 + 1 \times 2^{-1} + 0 \times 2^{-2} + 1 \times 2^{-1}$<br>= 13.625                                            | K1              | CO1 |  |  |  |  |  |

| 8. What is the difference between binary code and BCD?<br><u>Binary:</u> Any distinct element can be represented by a binary code. No<br>limitation for the minimum or maximum number of elements<br>required for coding the element.<br><u>BCD</u> : Only a decimal digit can be represented. It is a four bit<br>representation | K1 | CO1 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

| 9. Convert 0.640625 decimal number to its octal equivalent.<br>0.640625 x 8 = 5.125, 0.125 x 8 = 1.0<br>Ans. = 0.640 625 10 = 0.51                                                                                                                                                                                                | K1 | CO1 |

| 10. What is a gray code?<br>A gray code is a non weighted code which has the property<br>that the codes for successive decimal digits differ in exactly one bit.                                                                                                                                                                  | K1 | CO1 |

| 11. Define noise margin<br>It is the maximum noise voltage added to an input signal of a digital<br>circuit that does not cause an undesirable change in the circuit<br>output. It is expressed in volts.                                                                                                                         | K1 | CO1 |

| 12. Define fan-out<br>Number of logic gates at the next stage that can be loaded to<br>a given logic gate output so that voltages for each of the possible<br>logic state remain within the defined limits                                                                                                                        | K1 | CO1 |

| 13. Mention the important characteristics of digital IC's.<br>Fan out, Power dissipation, Propagation Delay, Noise Margin , Fan In,<br>Operating temperature ,Power supply requirements.                                                                                                                                          | K1 | CO1 |

| 14. What is propagation delay?<br>Propagation delay for a logic output from a logic gate means<br>the time interval between change in a defined reference point input<br>voltage and reflection of its effect at the output.                                                                                                      | K1 | CO1 |

| 15. Classify the logic family by operation?<br>The RTL, DTL, TTL, I2L, HTL logic comes under the saturated logic<br>family. The Schottky TTL, and ECL logic comes under the unsaturated<br>logic family.                                                                                                                          | K1 | CO1 |

| 16. Convert 0.1289062 decimal number to its hex equivalent<br>$0.1289062 \times 16 = 2.0625$<br>$0.0625 \times 16 = 1.0$<br>Ans. = 0.21 16                                                                                                                                      | К1 | CO1 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

| 17. Convert decimal number 22.64 to hexadecimal number.<br>16/ 22 R-6<br>16/ 1 R-1<br>R-0<br>0.64 x 16 = 10.24<br>0.24 x 16 = 3.84<br>0.84 x 16 = 13.44<br>.44 x 16 = 7.04<br>Ans. = (16 . A 3 D 7)                                                                             | К1 | CO1 |

| 18. What are the two steps in Gray to binary conversion?<br>The MSB of the binary number is the same as the MSB of the gray code<br>number. To obtain the next binary digit, perform an exclusive OR<br>operation between the bit just written down and the next gray code bit. | К1 | CO1 |

| 19. Convert gray code 101011 into its binary equivalent.<br>Gray Code : 1 0 1 0 1 1<br>Binary Code 1 1 0 0 1 0                                                                                                                                                                  | К1 | CO1 |

| 20. Convert (9 B 2 - 1A) H to its decimal equivalent.<br>N = 9 x 16 <sup>2</sup> + B x 16 <sup>1</sup> + 2 x 16 <sup>0</sup> + 1 x 16 <sup>-1</sup> + A (10) x 16 <sup>-2</sup><br>= 2304 + 176 + 2 + 0.0625 + 0.039<br>= 2482.1 10                                             | К1 | CO1 |

## 12. Part B Qs (with K level and CO)

| PART B                                                                                                                                                                                                                                                                                                   | _  |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

| 1. (i) Explain in detail about error detecting and error correcting codes<br>(ii) Given the two binary numbers $X = 10101002$ and $Y = 10000112$ ,<br>perform the subtraction (a) X-Y and (b) Y-X using 2's complement                                                                                   | K1 | CO1 |

| 2. Detect correct errors, if any, in the even parity Hamming code word 1010111 and write the correct code.                                                                                                                                                                                               | K1 | CO1 |

| 3. (i) Perform the following using BCD and Excess-3 addition(205+569) (ii)Encode the binary word11010 into odd parity Hamming code                                                                                                                                                                       | K1 | CO1 |

| 4. Perform the following operation and express the answer in octal form (756) 8-(437) 8+ (725) 16.                                                                                                                                                                                                       | K1 | CO1 |

| 5. A 12 bit hamming code word containing 8 bits of data and 4 parity bits is read from memory. What was the original 8 bit data word that was written into the memory if the 12 bit word read out as 101110010100 (2) 11111110100                                                                        | K1 | CO1 |

| 6. Perform each of the following computations using signed 8-bit words<br>in 1's complement and 2's complement binary arithmetic:<br>(i) $(+95)_{10} + (63)_{10}$ (ii) $(+42)_{10} + (-87)_{10}$<br>(iii) $(-13)_{10} + (-59)_{10}$<br>(iv) $(+38)_{10} + (-38)_{10}$<br>(v) $(-105)_{10} + (-120)_{10}$ | K1 | CO1 |

| <ul> <li>7. The state of a 12-cell register is 010110010111. What is its content if it represents:</li> <li>(a) 3 decimal digits in BCD.</li> <li>(b) 3 decimal digits in Excess-3 code</li> <li>(c) 3 decimal digits in 2421 BCD code</li> <li>(d) 3 decimal digits in 84-2-1 BCD code.</li> </ul>      | K1 | CO1 |

| 8. Draw and explain the circuit diagram of a CMOS NAND and NOR gate                                                                                                                                                                                                                                      | K1 | CO1 |

| 9. Explain the concept and implementation of ECL NOR/ OR gate.                                                                                                                                                                                                                                           | K1 | CO1 |

| 10. Compare DTL,RTL,TTL Logic families                                                                                                                                                                                                                                                                   | K1 | CO1 |

## 13.Supportive online Certification courses (NPTEL, Swayam, Coursera, Udemy, etc.,)

#### Swayam

Digital Circuits: <u>https://swayam.gov.in/nd1\_noc20\_ee70/preview</u> Duration: 12 weeks, Start Date: 14 Sep 2020, End Date: 04 Dec 2020

Udemy Digital Electric Circuits & Intelligent Electrical Devices <u>https://www.udemy.com/course/digital-electric-circuits-intelligent-electrical-devices/</u>

#### Coursera

Build a Modern Computer from First Principles: From Nand to Tetris (Project-Centered Course)

https://www.coursera.org/learn/build-a-computer

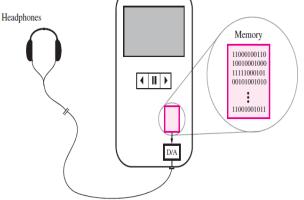

#### 14. Real time Applications in day to day life and to Industry

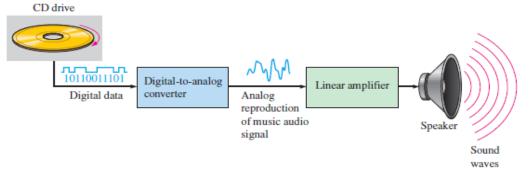

A few real time applications of digital systems is shown and explained.Basic block diagram of a iPod player

The iPod player stores music in the digital form in its memory and the Digital to analog converter converts it into the music that we hear through the head phones.

Basic block diagram of a CD player

The compact disk (CD) player has both digital and analog circuits. Music is stored on the compact disk in digital form. A laser diode optical system picks up the digital data from the rotating disk and transfers it to the digital-to-analog converter (DAC). The DAC changes the digital data into an analog signal which is an electrical reproduction of the original music. This signal is amplified and sent to the speaker. An analog-to-digital converter (ADC) is used to record the music on to the disk in digital form.

Source: Thomas Floyd- Digital Fundamentals

## 15. Contents beyond the Syllabus ( COE related Value added courses)

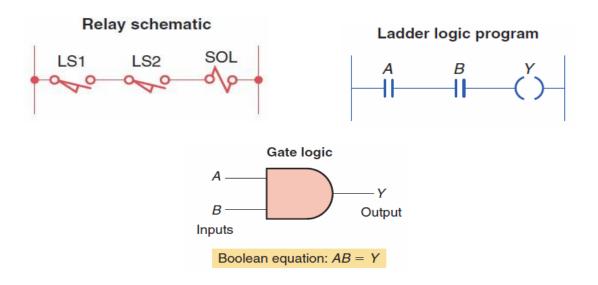

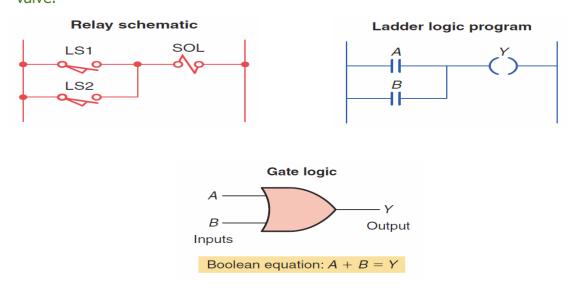

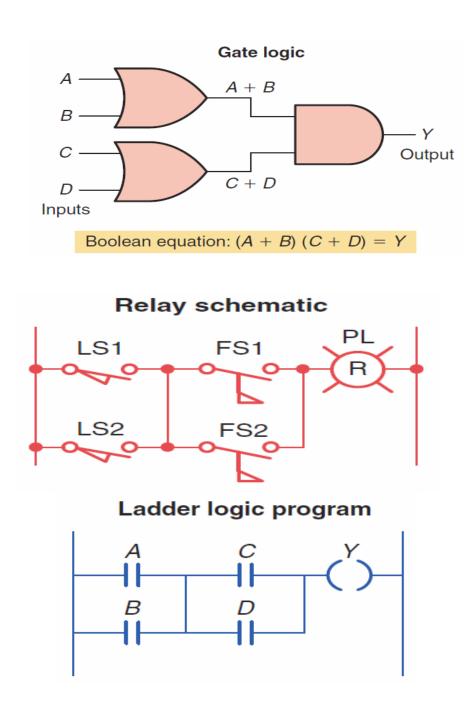

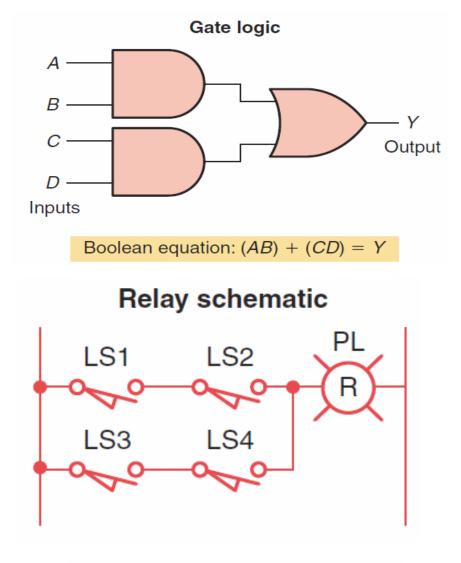

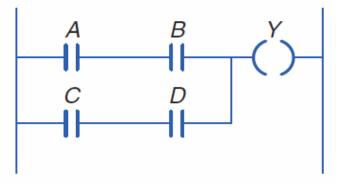

- Simulation of logic gates using PLC simulation software available at Factory Automation CoE.

- Example: Two limit switches connected in series and used to control a solenoid valve.

Example: Two limit switches connected in **parallel** and used to control a solenoid valve.

#### 17. Prescribed Text Books & Reference Books

#### TEXT BOOKS:

1.James W. Bignel, Digital Electronics, Cengage learning, 5th Edition, 2007.

2.M. Morris Mano, 'Digital Design with an introduction to the VHDL', Pearson Education, 2013.

3.Comer "Digital Logic & State Machine Design, Oxford, 2012.

#### REFERENCES

1.Mandal, "Digital Electronics Principles & Application, McGraw Hill Edu, 2013.

2. William Keitz, Digital Electronics-A Practical Approach with VHDL, Pearson, 2013.

3. Thomas L. Floyd, 'Digital Fundamentals', 11th edition, Pearson Education, 2015.

4.Charles H.Roth, Jr, Lizy Lizy Kurian John, 'Digital System Design using VHDL, Cengage, 2013.

# Digital Logic Circuits Unit 2

#### 8. Activity based learning

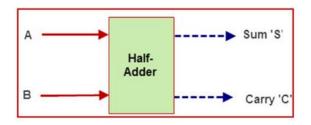

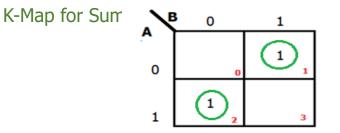

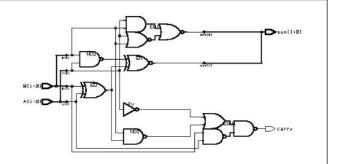

- Understanding the working of the combinational logic circuits through simulation using Logisim

- Simulation of

- Half adder

- Full adder

- Multiplexer

- De-multiplexer

- Practice using open source DEEDS: <u>https://www.digitalelectronicsdeeds.com/</u>

#### 9. Lecture Notes

#### **Table of Contents**

#### **© UNIT II COMBINATIONAL CIRCUITS**

- 1. Combinational logic Representation of logic functions-SOP and POS forms,

- 2. K-map representations minimization using K maps

- 3. Simplification and implementation of combinational logic

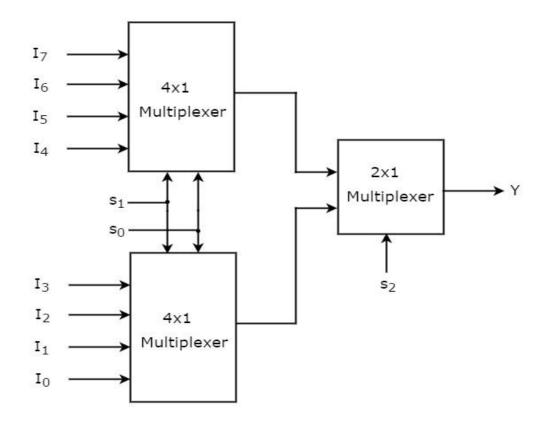

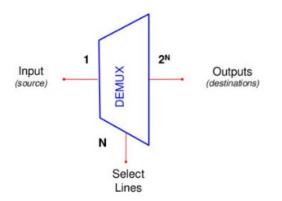

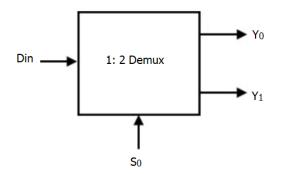

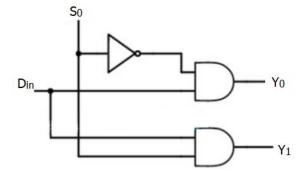

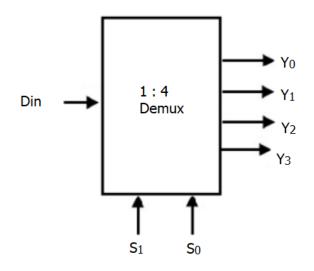

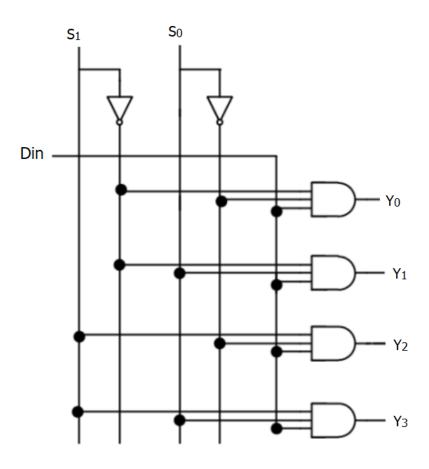

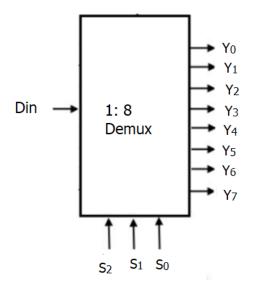

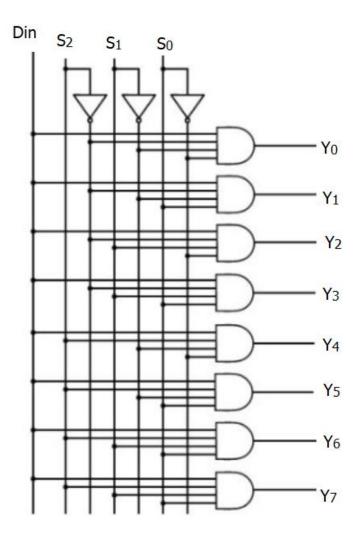

- Multiplexers and De multiplexers

- Code converters,

- Adders, Subtractors,

- Encoders and Decoders.

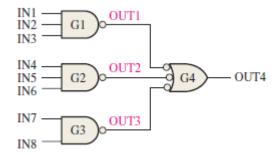

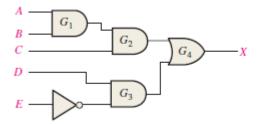

#### **COMBINATIONAL CIRCUITS**

#### Introduction:

- In digital logic, the inputs and output of a function are in the form of binary numbers (boolean values) i.e., the values are either zero (0) or one (1). Therefore, digital logic is also known as 'Boolean logic'.

- 2. These inputs and output can be termed as 'Boolean Variables'.

- 3. The output boolean variable of a digital signal can be expressed in terms of input boolean variables which forms the 'Boolean Expression'.

- 4. A boolean expression is an expression which consists of variables, constants (0false and 1-true) and logical operators which results in true or false.

- 5. They are used to describe Switching Function / Boolean Function.

- 6. In Boolean function, the variables are appeared either in complemented or in uncomplemented form. Each occurrence of a variable in either a complemented or a uncomplemented form is called a literal.

- 7. A Boolean function can be represented as:

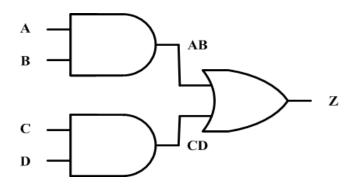

- Algebraic expression Eg: Z(A,B,C,D) = AB + CD

- Truth table

- Logic diagram using gates

Logic diagram for Z(A,B,C,D) = AB + CD

#### Truth table

| A | В | С | D | z      | AB | CD |

|---|---|---|---|--------|----|----|

| 0 | 0 | 0 | 0 | 0      | 0  | 0  |

| 0 | 0 | 0 | 1 | 0      | 0  | 0  |

| 0 | 0 | 1 | 0 | 0      | 0  | 0  |

| 0 | 0 | 1 | 1 | 1      | 0  | 1  |

| 0 | 1 | 0 | 0 | 0      | 0  | 0  |

| Õ | 1 | Õ | 1 | Õ      | 0  | 0  |

| 0 | 1 | 1 | 0 | 0<br>0 | 0  | 0  |

| 0 | 1 | 1 | 1 | 1      | 0  | 1  |

| 1 | 0 | 0 | 0 | 0      | 0  | 0  |

| 1 | 0 | 0 | 1 | 0      | 0  | 0  |

| 1 | 0 | 1 | 0 | 0      | 0  | 0  |

| 1 | 0 | 1 | 1 |        | 0  | 1  |

| 1 | 1 | 0 | 0 | 1<br>1 | 1  | 0  |

| 1 | 1 | 0 | 1 | 1<br>1 | 1  | 0  |

| 1 | 1 | 1 | 0 | 1      | 1  | 0  |

| 1 | 1 | 1 | 1 | 1      | 1  | 1  |

### **Boolean Algebra**

Boolean algebra is a convenient and systematic way of expressing and analysing the operation of logic circuits.

It was developed by George Boole in 1847 and was proposed for design by Claude E. Shannon in 1938.

Boolean algebra provides economical and straightforward approach and is used extensively in designing electronic circuits used in computers

### Laws of Boolean Algebra

Basic Identities

1. X + 0 = X2. X • 1 = X 3. X + 1 = 14. X  $\cdot$  0 = 0 5. X + X = X6. X • X = X 7. X + X' = 1 8. X • X' = 0 9. (X')' = XBasic Laws Commutative 10. X + Y = Y + X11.  $X \cdot Y = Y \cdot X$ Associative 12. X+(Y+Z)=(X+Y)+Z13. X(YZ) = (XY)ZDistributive 14. X(Y+Z) = XY+XZ15. X+YZ=(X+Y)(X+Z)

De Morgan's Theorem

- 16.  $(X + Y)' = X' \cdot Y'$

- 17. (XY)' = X' + Y'

- Consensus Theorem

- 18. XY + X'Z + YZ = XY + X'Z

- The *dual* of a function is obtained by interchanging OR and AND operations and replacing 1s and 0s with 0s and 1s.

| Theorem                  | Dual Theorem             |                     |

|--------------------------|--------------------------|---------------------|

| X + X = X                | X . X = X                | Idempotent Law      |

| X + 1 = 1                | X . 0 = 0                | Annulment Law       |

| $X + X \cdot Y = X$      | X. (X + Y) = X           | Absorption Law      |

| (X')' = X                |                          | Involution Law      |

| X + (Y + Z) = (X+Y) + Z  | X . (Y . Z) = (X . Y). Z | Associative Law     |

| $(X + Y)' = X' \cdot Y'$ | (XY)' = X' + Y'          | De Morgan's Theorem |

### Simplification using Boolean rules

Reduce

$$AB + (AC)' + AB'C(AB + C)$$

AB +  $(AC)' + AB'C(AB + C) = AB + (AC)' + AAB'BC + AB'CC$

=  $AB + (AC)' + AB'C$  [A.A = 1]

=  $AB + (AC)' + AB'C$  [A.A = 1]

=  $AB + (AC)' + AB'C$  [A.A = 1]

=  $AB + A' + C' = AB'C$  [(AB)' = A' + B']

=  $A' + B + C' + AB'C$  [A + AB' = A + B]

=  $A' + B + C' + B'C$

=  $A' + B + C' + B'$

=  $A' + C' + 1$