## DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERINGEC8791EMBEDDED AND REAL TIME SYSTEMSL T P C 3 0 0 3

#### **Objectives:**

- To Understand the concept of embedded system design and analysis.

- To learn the architecture of ARM processor.

- To learn the Programming of ARM processor

- To Expose the basic concepts of embedded programming.

- To Learn real time operating systems

#### UNIT I INTRODUCTION TO EMBEDDED SYSTEM DESIGN

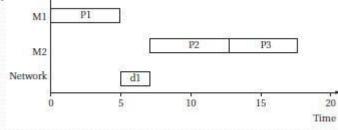

Complex systems and microprocessors– Embedded system design process –Design example: Model train controller- Design methodologies- Design flows - Requirement Analysis – Specifications-System analysis and architecture design – Quality Assurance techniques -Designing with computing platforms – consumer electronics architecture – platform-level performance analysis.

#### UNIT II ARM PROCESSOR AND PERIPHERALS

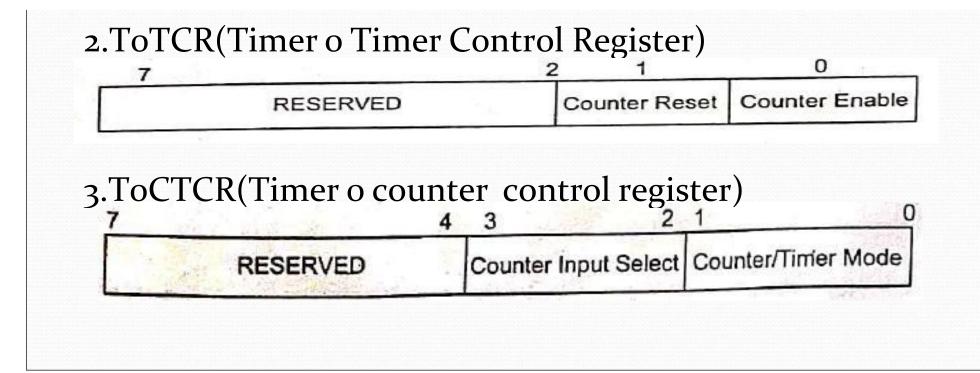

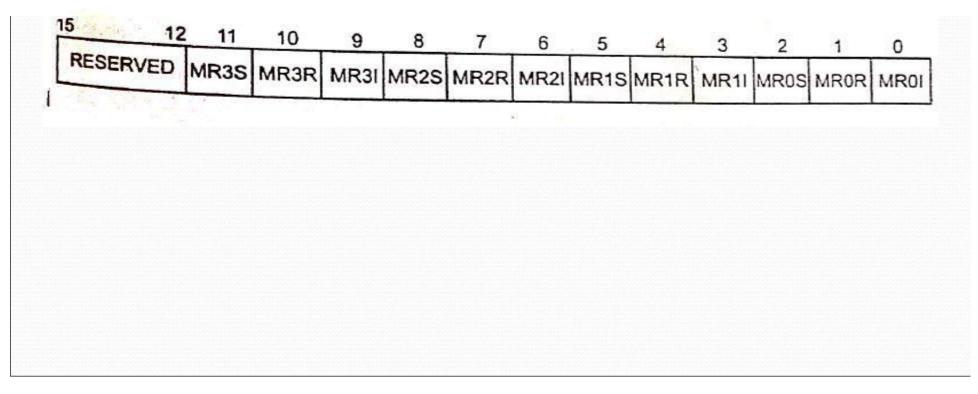

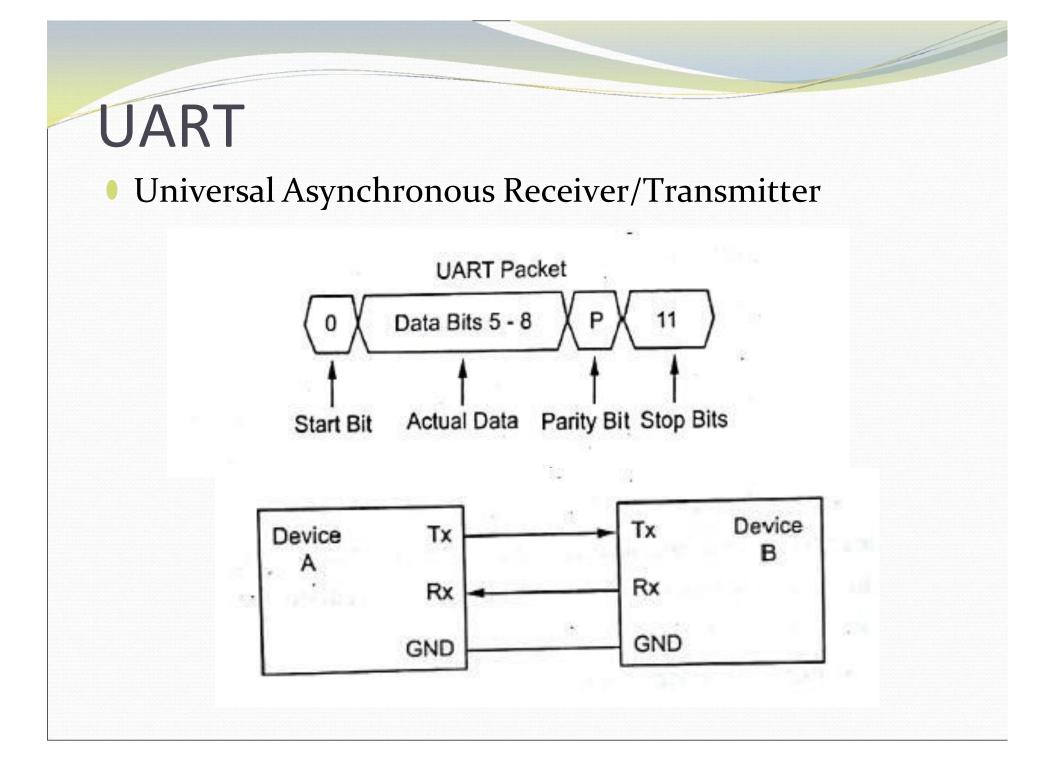

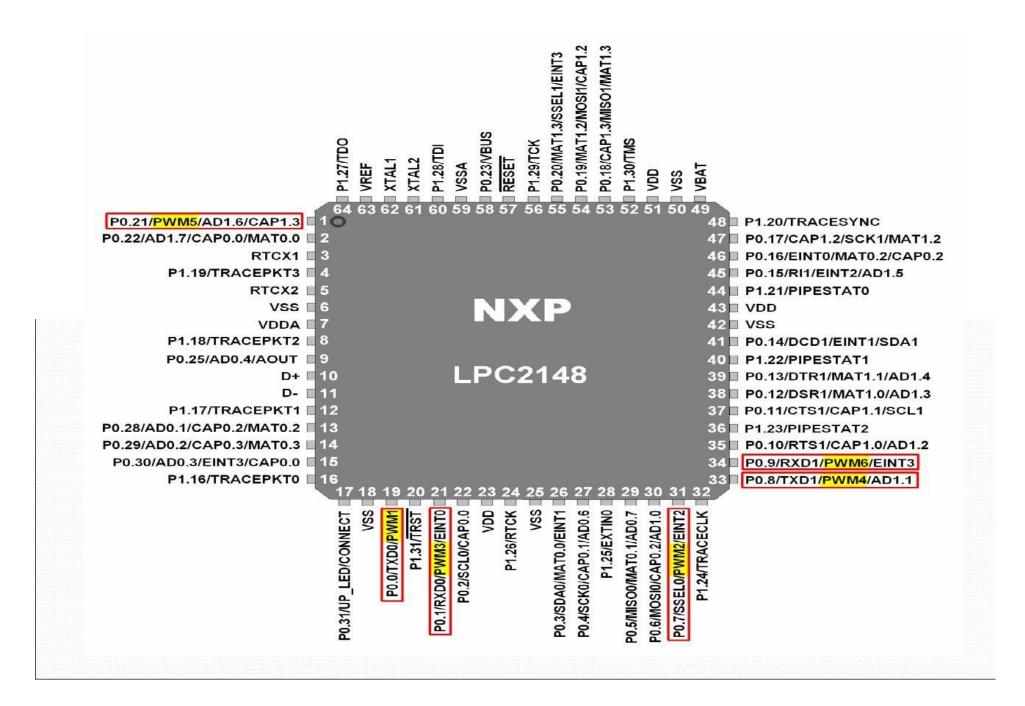

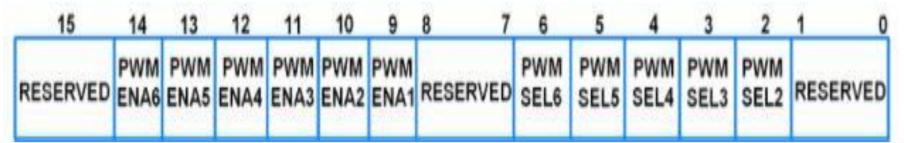

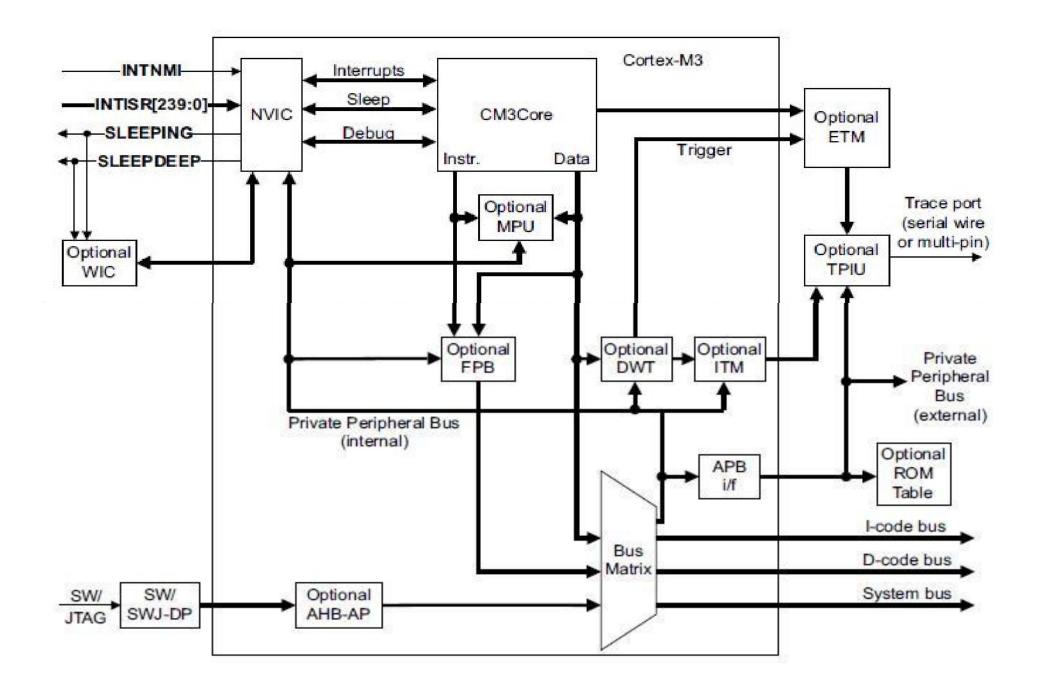

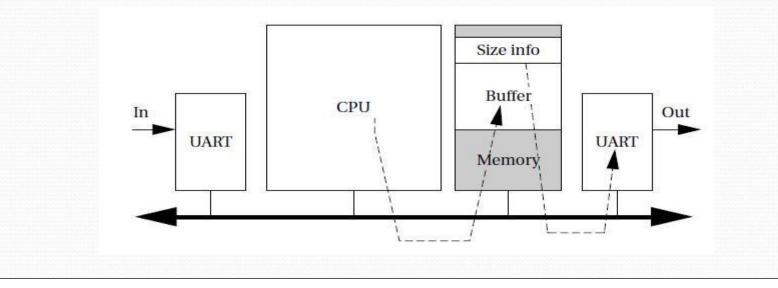

ARM Architecture Versions – ARM Architecture – Instruction Set – Stacks and Subroutines – Features of the LPC 214X Family – Peripherals – The Timer Unit – Pulse Width Modulation Unit – UART – Block Diagram of ARM9 and ARM Cortex M3 MCU.

#### UNIT III EMBEDDED PROGRAMMING

Components for embedded programs- Models of programs- Assembly, linking and loading – compilation techniques- Program level performance analysis – Software performance optimization – Program level energy and power analysis and optimization – Analysis and optimization of program size- Program validation and testing.

#### UNIT IV REAL TIME SYSTEMS

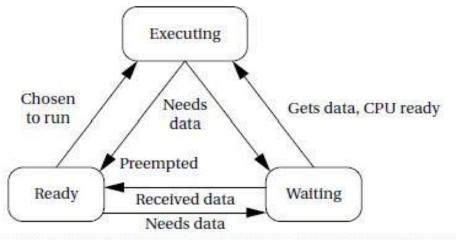

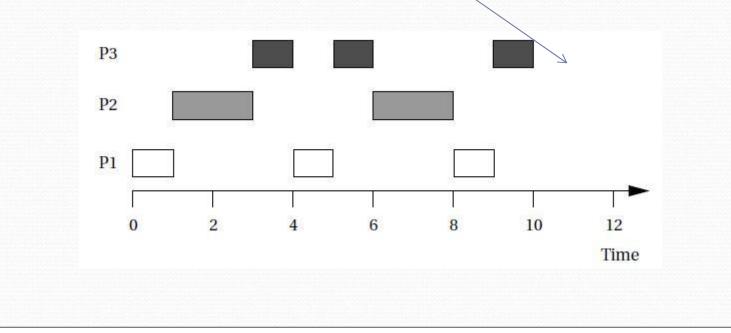

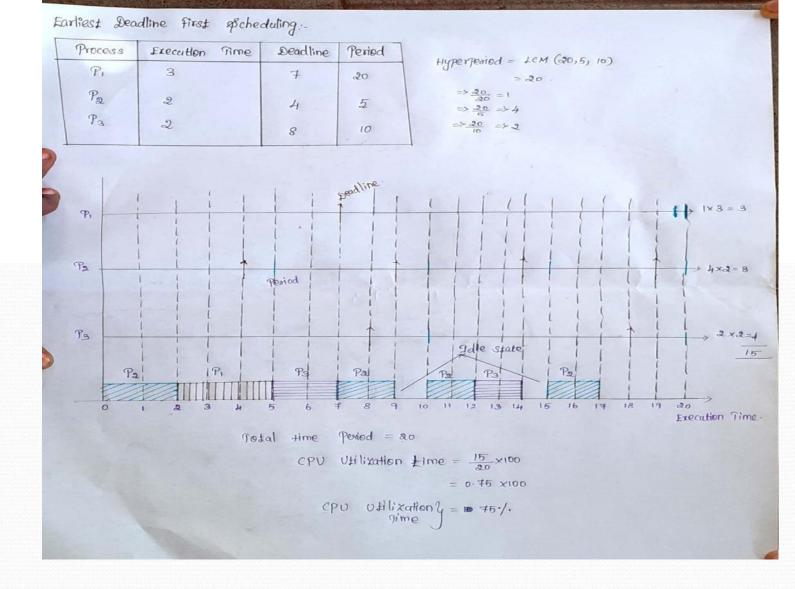

Structure of a Real Time System — Estimating program run times – Task Assignment and Scheduling – Fault Tolerance Techniques – Reliability, Evaluation – Clock Synchronisation..

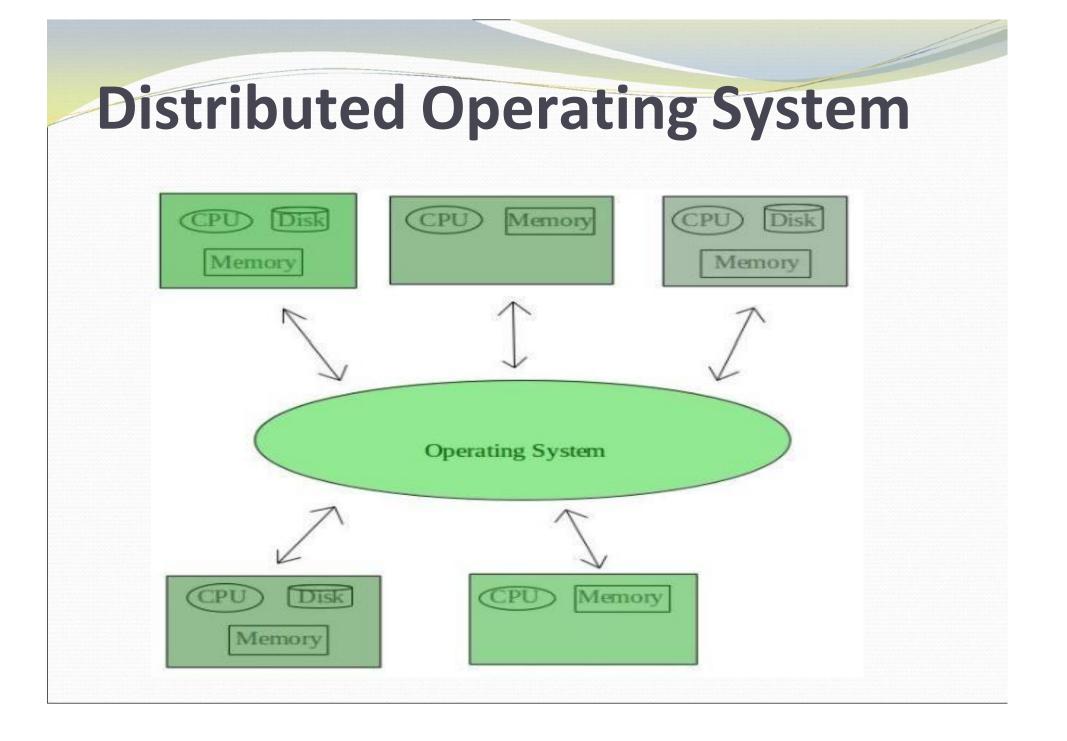

#### UNIT V PROCESSES AND OPERATING SYSTEMS

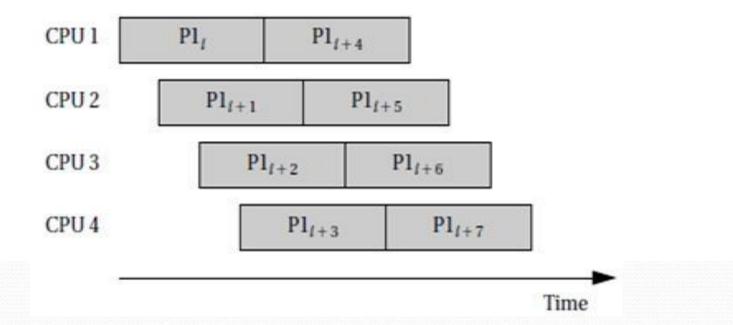

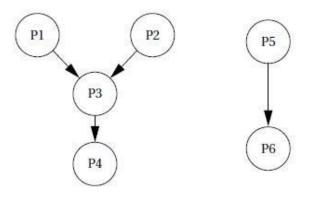

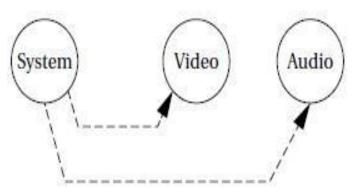

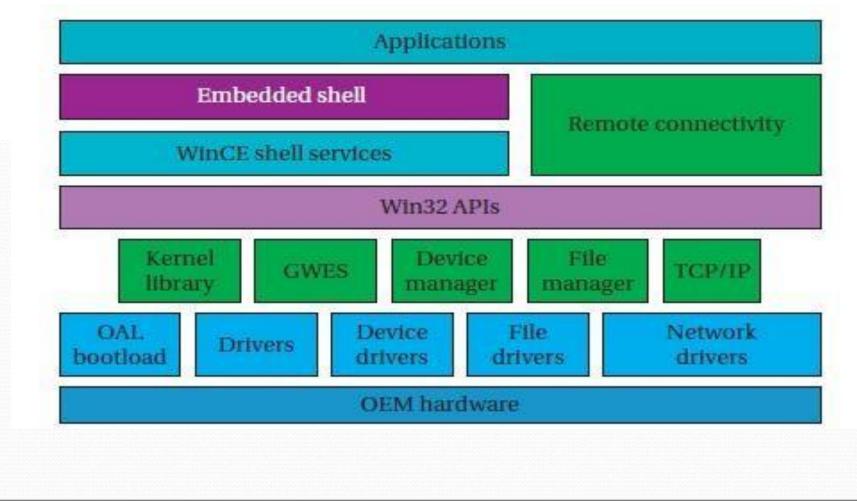

Introduction – Multiple tasks and multiple processes – Multirate systems- Preemptive realtime operating systems- Priority based scheduling- Interprocess communication mechanisms – Evaluating operating system performance- power optimization strategies for processes – Example Real time operating systems-POSIX-Windows CE. - Distributed embedded systems – MPSoCs and shared memory multiprocessors. – Design Example - Audio player, Engine control unit – Video accelerator.

#### **TOTAL : 45 PERIODS**

#### **Course Outcomes:**

At the end of the course, the student will be able to:

- Summarize Architecture and programming of ARM processor.

- Applying the concepts of embedded systems and its features.

- Analyze various Real Time Operating system is used in Embedded System.

- **Design** the flow &Techniques to develop Software for embedded system networks.

- Analyze Real-time applications using embedded System Products.

#### **TEXT BOOK:**

- Marilyn Wolf, "Computers as Components Principles of Embedded Computing System Design", Third Edition "Morgan Kaufmann Publisher (An imprint from Elsevier), 2012. (UNIT I, II, III, V)

- 2. Jane W.S.Liu, Real Time Systems, Pearson Education, Third Indian Reprint, 2003.(UNIT IV)

#### **REFERENCES:**

- 1. Lyla B.Das, —Embedded Systems : An Integrated Approach Pearson Education, 2013.

- 2. Jonathan W.Valvano, "Embedded Microcomputer Systems Real Time Interfacing", Third Edition Cengage Learning, 2012.

- 3. David. E. Simon, "An Embedded Software Primer", 1st Edition, Fifth Impression, Addison-Wesley Professional, 2007.

- 4. Raymond J.A. Buhr, Donald L.Bailey, "An Introduction to Real-Time Systems- From Design to Networking with C/C++", Prentice Hall, 1999.

- 5. C.M. Krishna, Kang G. Shin, "Real-Time Systems", International Editions, Mc Graw Hill 1997

- 6. K.V.K.K.Prasad, "Embedded Real-Time Systems: Concepts, Design & Programming", Dream Tech Press, 2005.

- 7. Sriram V Iyer, Pankaj Gupta, "Embedded Real Time Systems Programming", Tata Mc Graw Hill, 2004.

## EC8791 -EMBEDDED AND REAL TIME SYSTEMS

1. Wayne Wolf, "Computers as Components – Principles of Embedded Computing System Design", Third Edition "Morgan Kaufmann Publisher (An imprint from Elsevier), 2012.

#### **UNIT I**

#### **INTRODUCTION TO EMBEDDEDSYSTEM DESIGN**

Complex systems and microprocessors– Embedded system design process –Design example: Model train controller- Design methodologies- Design flows - Requirement Analysis – Specifications-System analysis and architecture design – Quality Assurance techniques - Designing with computing platforms – consumer electronics architecture – platformlevel performance analysis.

# Introduction-Embedded Systems

- An Embedded system is an electronic system that has a software and is embedded in computer hardware.

- It is a system which has collection of components used to execute a task according to a program or commands given to it.

- Examples → Microwave ovens, Washing machine, Telephone answering machine system, Elevator controller system, Printers, Automobiles, Cameras, etc.

## **EMBEDDED SYSTEM HARDWARE**

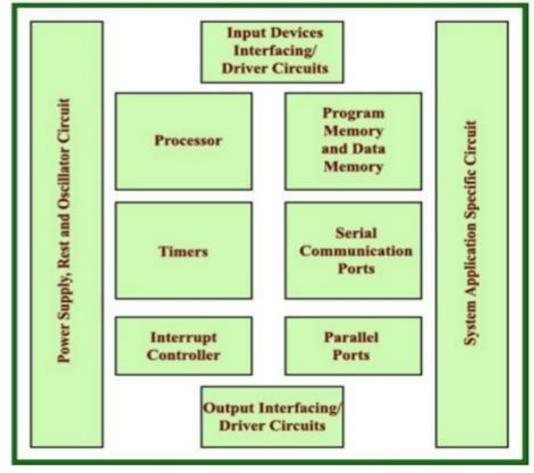

# Components of Embedded system

- Microprocessor

- Memory Unit(RAM,ROM)

- Input unit(Keyboard,mouse,scanner)

- Output unit(pinters,video monitor)

- Networking unit(Ethernet card)

- I/O units(modem)

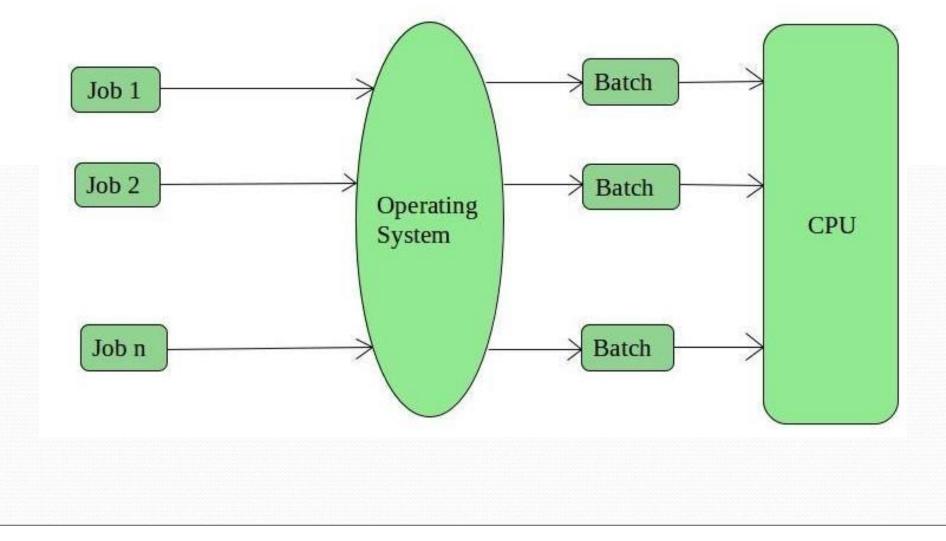

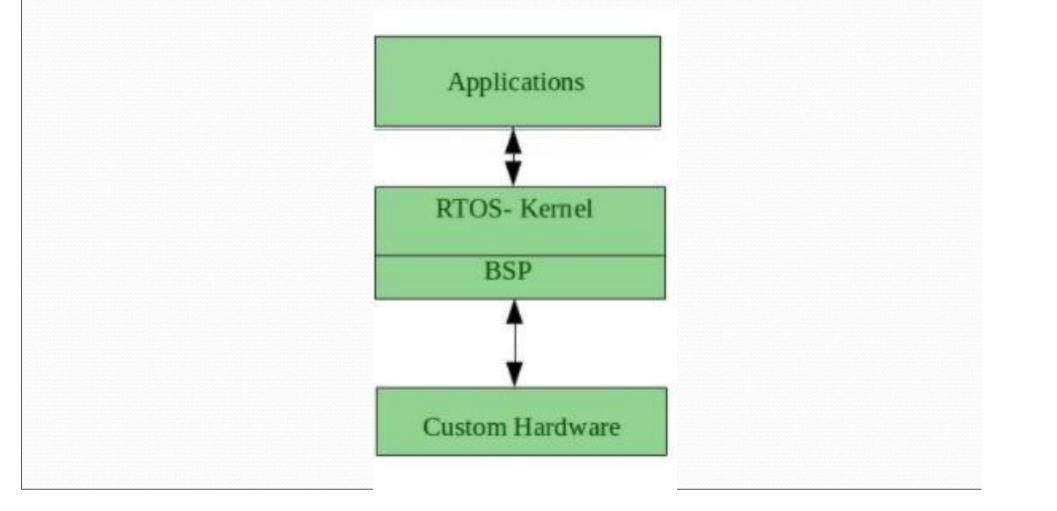

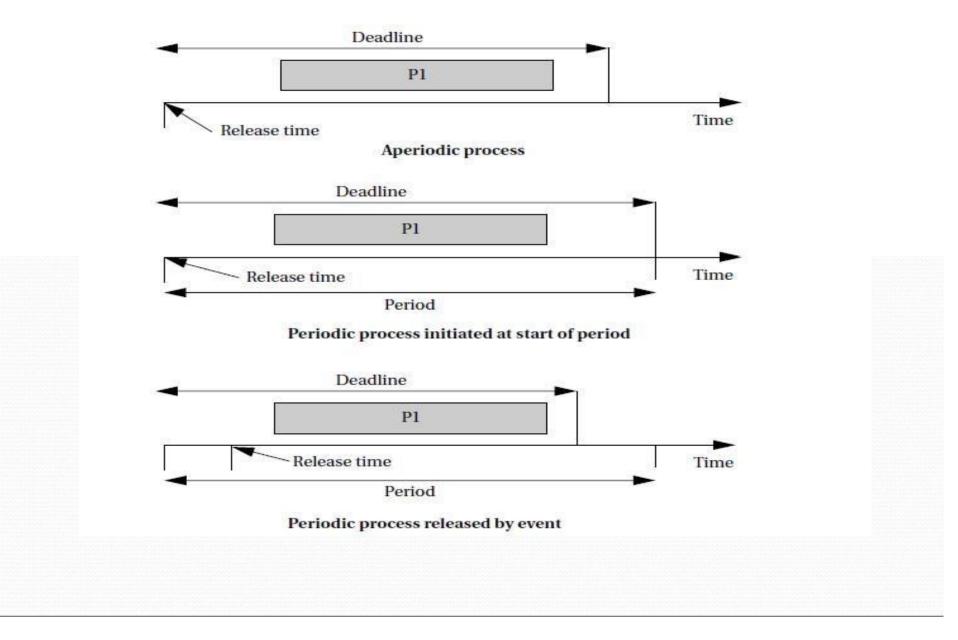

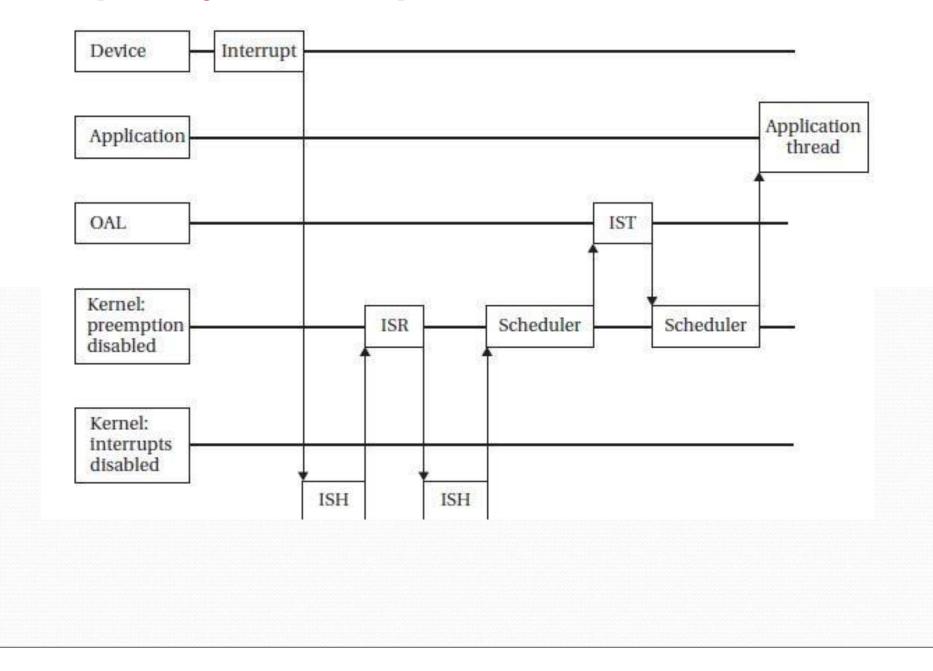

# Real Time Operating System-RTOS

- Real-Time Operating System (RTOS) is an operating system (OS) intended to serve real-time applications that process data as it comes in, typically without buffer delays.

- It schedules their working and execution by following a plan to control the latencies and to meet the dead lines.

- Modeling and evaluation of a real-time scheduling system concern is on the analysis of the algorithm capability to meet a process deadline.

- A deadline is defined as the time required for a task to be processed.

# Classification of Embedded system

- 1. Small scale Embedded system  $\rightarrow$  (8/16bit microcontroller)

- 2. Medium Scale Embedded system  $\rightarrow \rightarrow (16/32)$  bit microcontroller, more tools like simulator, debugger)

- 3. Sophisticated Embedded system  $\rightarrow$  (configurable processor and PAL)

# Embedded designer-skills

- Designer has a knowledge in the followings field,

- Microcontrollers, Data comm., motors, sensors, measurements ,C programming, RTOS programming.

## 1) COMPLEX SYSTEMS AND MICROPROCESSORS

## Embedded(+)computer system

- Embedded system is a complex system

- It is any device that includes a programmable computer but is not itself intended to be a general-purpose computer.

## History of Embedded computer system

- Computers have been embedded into applications since the earliest days of computing.

- In 1940s and 1950s→Whirlwind, designed a first computer to support real-time operation for controlling an aircraft simulator.

- In 1970s→ The first microprocessor(Intel 4004) was designed for an embedded application (Calculator), provided basic arithmetic functions.

- In 1972s→ The first handheld calculator (HP-35) was to perform transcendental functions, so it used several chips to implement the CPU, rather than a single-chip microprocessor.

- Designer faced critical problems to design a digital circuits to perform operations like trigonometric functions using calculator.

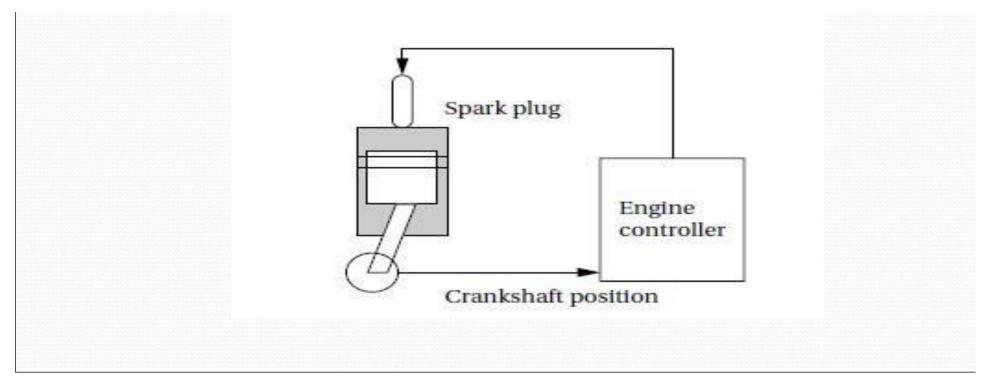

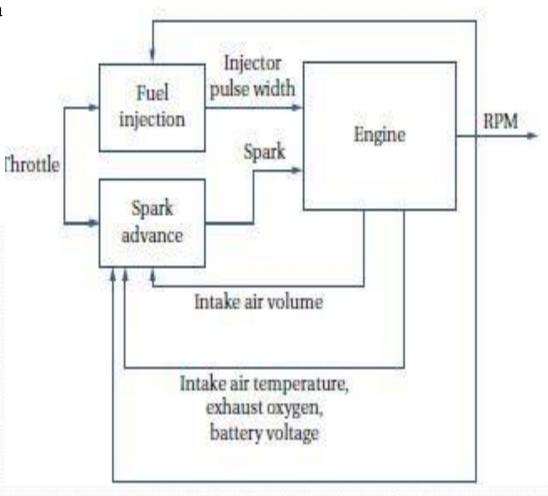

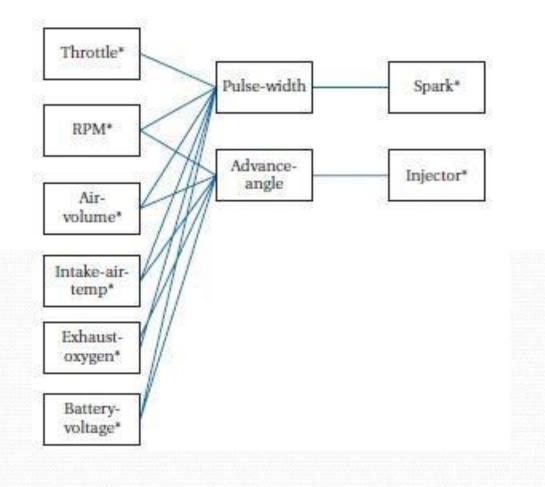

- But ,Automobile designers started making use of the microprocessor for to control the engine by determining when spark plugs fire, controlling the fuel/air mixture

## Levels of Microprocessor

- 8-bit microcontroller→ for low-cost applications and includes on-board memory and I/O devices.

- 2. 16-bit microcontroller → used for more sophisticated applications that may require either longer word lengths or off-chip I/O and memory.

- 3. 32-bit *RISC* microprocessor → offers very high performance for computation-intensive applications.

#### Microprocessor Uses/Applications

- Microwave oven has at least one microprocessor to control oven operation

- Thermostat systems, which change the temperature level at various times during the day

- The modern camera is a prime example of the powerful features that can be added under microprocessor control.

- Digital television makes extensive use of embedded processors.

## **Embedded Computing Applications**

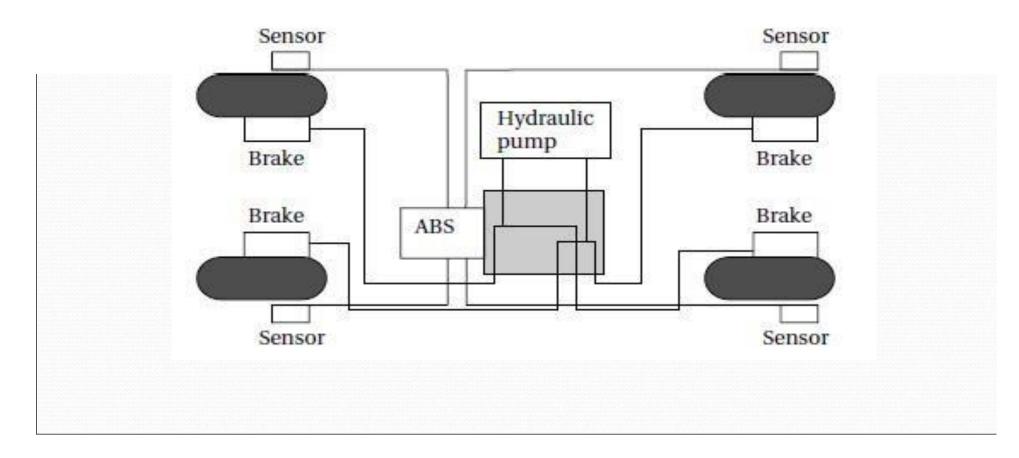

- Ex→BMW 850i Brake and Stability Control System

- The BMW 850i was introduced with a sophisticated system for controlling the wheels of the car.

- Which uses An antilock brake system (ABS) and An automatic stability control (ASC +T) system.

- 1. <u>An antilock brake system (ABS)</u>

- Reduces skidding by pumping the brakes.

- It is used to temporarily release the brake on a wheel when it rotates too slowly—when a wheel stops turning, the car starts skidding and becomes hard to control.

- It sits between the hydraulic pump, which provides power to the brakes.

- It uses sensors on each wheel to measure the speed of the wheel.

- The wheel speeds are used by the ABS system to determine how to vary the hydraulic fluid pressure to prevent the wheels from skidding.

- 2. <u>An automatic stability control (ASC +T) system</u>

- It is used to control the engine power and the brake to improve the car's stability during maneuvers.

- It controls four different systems: throttle, ignition timing, differential brake, and (on automatic transmission cars) gear shifting.

- It can be turned off by the driver, which can be important when operating with tire snow chains.

- It has control unit has two microprocessors, one of which concentrates on logic-relevant components and the other on performance-specific components.

- The ABS and ASC+ T must clearly communicate because the ASC+ T interacts with the brake system.

# Characteristics of Embedded Computing Applications

- 1. Complex algorithms-The microprocessor that controls an automobile engine must perform complicated filtering functions to optimize the performance of the car while minimizing pollution and fuel utilization.

- 2. User interface-The moving maps in Global Positioning System (GPS) navigation are good examples of user interfaces.

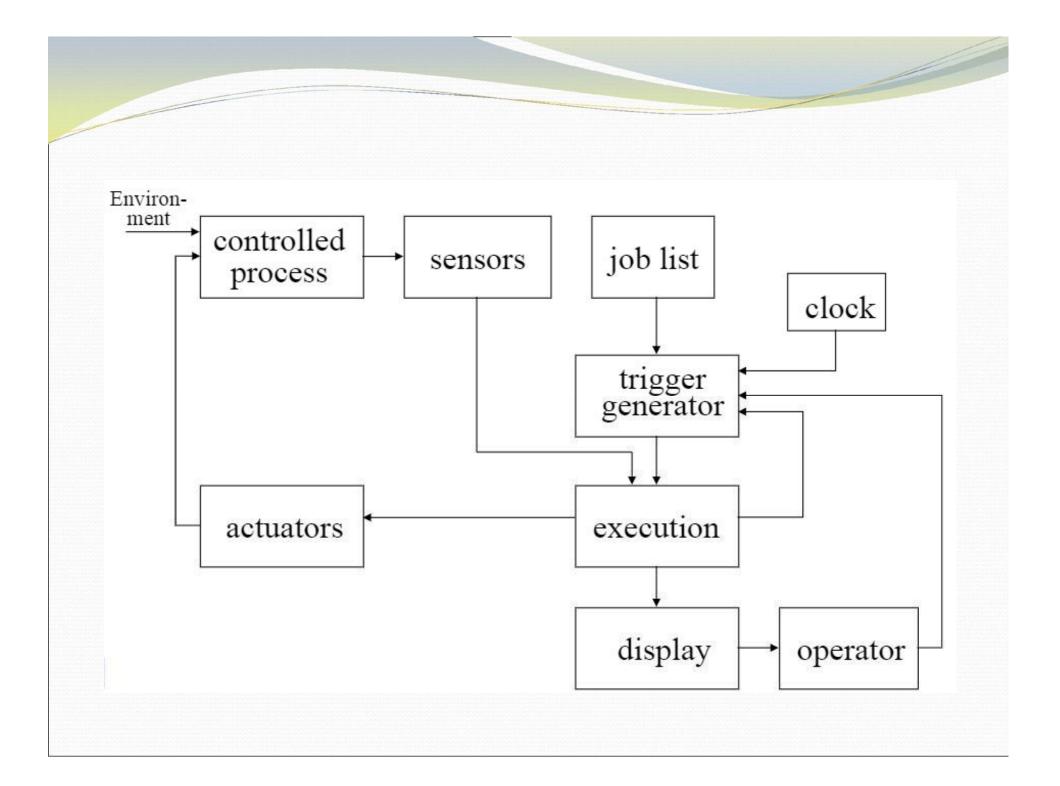

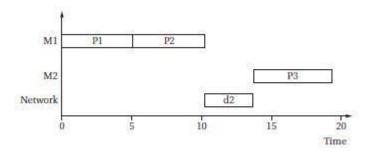

- 3. Real time-Embedded computing systems have to perform in real time—if the data is not ready by a certain deadline, the system breaks. In some cases, failure to meet a deadline or missing a deadline does not create safety problems but does create unhappy customers

- 4. Multirate-Multimedia applications are examples of *multirate* behavior. The audio and video portions of a multimedia stream run at very different rates, but they must remain closely synchronized. Failure to meet a deadline on either the audio or video portions spoils the perception of the entire presentation.

- 5. Manufacturing cost- It is depends on the type of microprocessor used, the amount of memory required, and the types of I/O devices.

- 6. Power and energy-Power consumption directly affects the cost of the hardware, since a larger power supply may be necessary.

- 7. Energy consumption →affects battery life, which is important in many applications, as well as heat consumption, which can be important even in desktop applications.

# Why Use Microprocessors?

- Microprocessors are a very efficient way to implement digital systems.

- It make it easier to design families of products with various feature at different price points

- It can be extended to provide new features to keep up with rapidly changing markets.

- It executes program very efficiently

- It make their CPU run very fast

- Implementing several function on a single processor

# Why not use PCs for all embedded computing?

- Real time performance is very less in PC because of different architecture.

- It increases the complexity and price of components due to broad mix of computing requirements.

## Challenges in Embedded Computing System Design

- 1. How much hardware do we need?

- To meet performance deadlines and manufacturing cost constraints, the choice of Hardware is important.

- Too much hardware and it becomes too expensive.

- 2. How do we meet deadlines?

- To speed up the hardware so that the program runs faster. But the system more expensive.

- It is also entirely possible that increasing the CPU clock rate may not make enough difference to execution time, since the program's speed may be limited by the memory system.

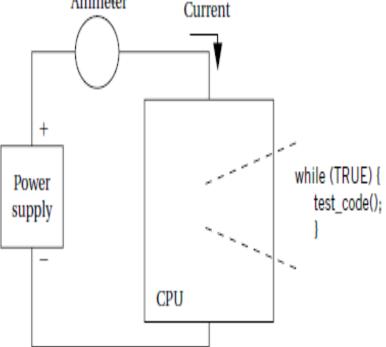

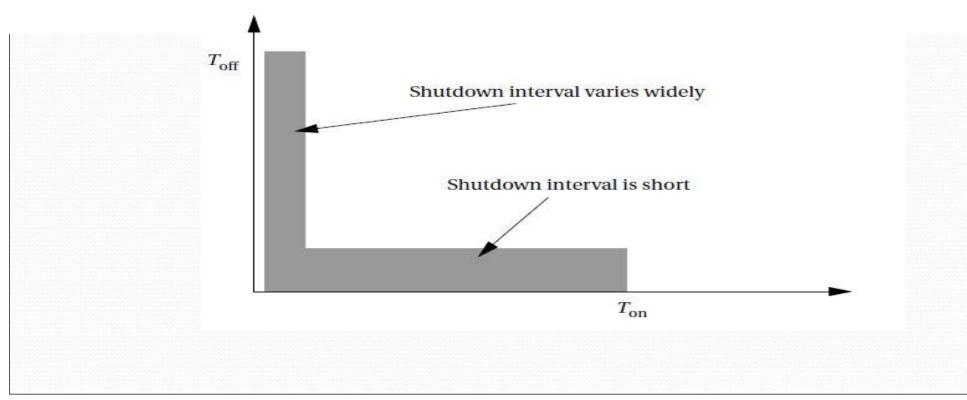

- 3. How do we minimize power consumption?

- In battery-powered applications, power consumption is extremely important.

- In non-battery applications, excessive power consumption can increase heat dissipation.

- Careful design is required to slow down the noncritical parts of the machine for power consumption while still meeting necessary performance goals.

### 4) How do we design for upgradability?

• The hardware platform may be used over several product generations, or for several different versions , able to add features by changing software.

*Complex testing: R*un a real machine in order to generate the proper data.

Testing of an embedded computer from the machine in which it is embedded.

*Limited observability and controllability* → *No keyboard and screens,* in real-time applications we may not be able to easily stop the system to see what is going on inside and to affect the system's operation.

#### *4.3) Restricted development environments:*

- We generally compile code on one type of machine, such as a PC, and download it onto the embedded system.

- To debug the code, we must usually rely on programs that run on the PC or workstation and then look inside the embedded system.

## **Performance in Embedded Computing**

• Embedded system designers have to set their goal —their program must meet its *deadline*.

#### Performance Analysis

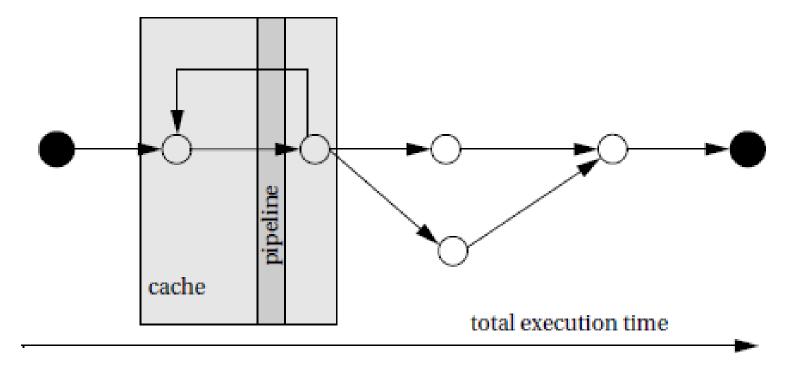

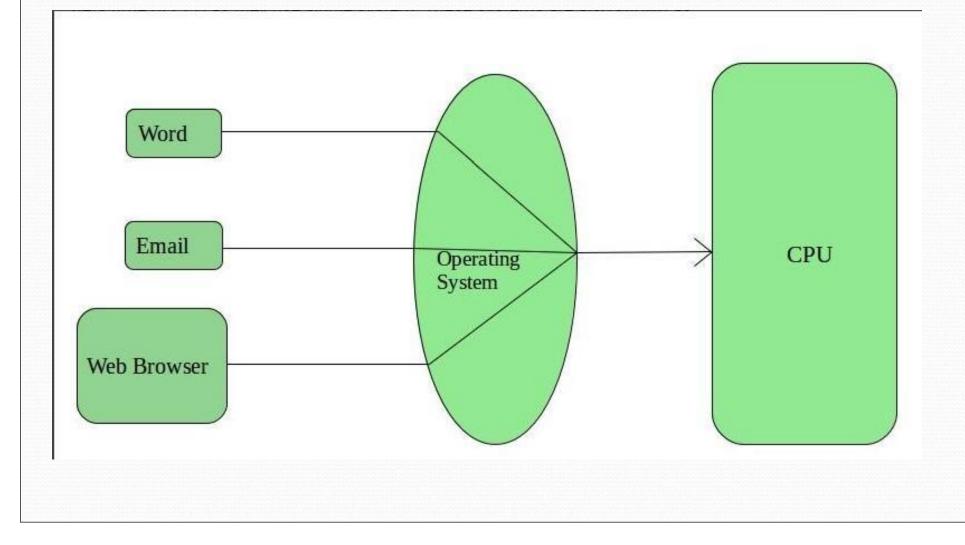

- 1. **CPU:** The **CPU clearly influences the behavior of the program**, particularly when the CPU is a pipelined processor with a cache.

- 2. Platform: The platform includes the bus and I/O devices. The platform components that surround the CPU are responsible for feeding the CPU and can dramatically affect its performance.

- 3. Program: Programs are very large and the CPU sees only a small window of the program at a time. We must consider the structure of the entire program to determine its overall behavior.

- 4. Task: We generally run several programs simultaneously on a CPU, creating a multitasking system. The tasks interact with each other in ways that have profound implications for performance.

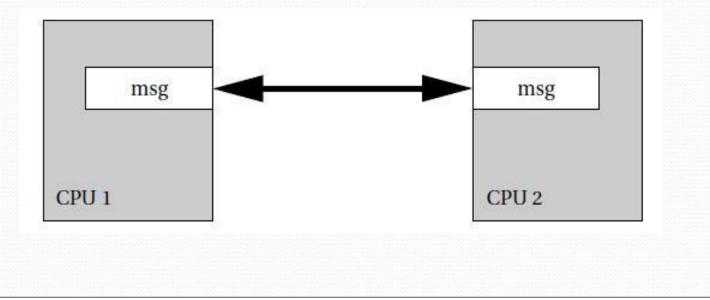

- 5. Multiprocessor: Many embedded systems have more than one processor—they may include multiple programmable CPUs as well as accelerators. Once again, the interaction between these processors adds yet more complexity to the analysis of overall system performance.

# 2) EMBEDDED SYSTEM DESIGN PROCESS

#### Design process has two objectives as follows.

- 1. It will give us an introduction to the various steps in embedded system design.

- 2. <u>Design methodology</u>

- I. Design to ensure that we have done everything we need to do, such as optimizing performance or performing functional tests.

- II. It allows us to develop computer-aided design tools.

- III. A design methodology makes it much easier for members of a design team to communicate.

## Levels of abstraction in the design process.

<u>1)Requirements</u> •It can be classified in to functional or nonfunctional Requirements 1.1)Functional Requirements Top-down Bottom-up design •<u>Gather</u> an informal description from the customers. design •Refine the requirements into a specification that contains Specification enough information to design the system architecture. •Ex:Sample Requirements form •Name $\rightarrow$ Giving a name to the project Architecture Purpose → Brief one- or two-line description of what the system is supposed to do. •Inputs& Outputs  $\rightarrow$  Analog electronic signals? Digital data? Components Mechanical inputs? **Performance**  $\rightarrow$  computations must be performed within a System integration certain time frame •Manufacturing  $cost \rightarrow cost$  of the hardware components. Power  $\rightarrow$  how much power the system can consume Physical size and weight  $\rightarrow$  indication of the physical size of the system

- <u>1.2) Non-Functional Requirements</u>

- Performance→ depends upon approximate time to perform a userlevel function and also operation must be completed within deadline.

- Cost→Manufacturing cost includes the cost of components and assembly.

- Nonrecurring engineering (NRE) costs include the personnel and other costs of designing the

- system

- Physical Size and Weight→The final system can vary depending upon the application.

- Power Consumption → Power can be specified in the requirements stage in terms of battery life.

## 2)SPECIFICATION

- The specification must be carefully written so that it accurately reflects the customer's requirements.

- It can be clearly followed during design.

## 3) Architecture Design

- The architecture is a plan for the overall structure of the system.

- It is in the form block diagram that shows a major operation and data flow.

## <u>4)</u> Designing Hardware and Software Components

• The architectural description tells us what components we need include both hardware—FPGAs, boards & software modules

## <u>5)System Integration</u>

- Only after the components are built, putting them together and seeing a working system.

- Bugs are found during system integration, and good planning can help us find the bugs quickly.

## Embedded system Design Example

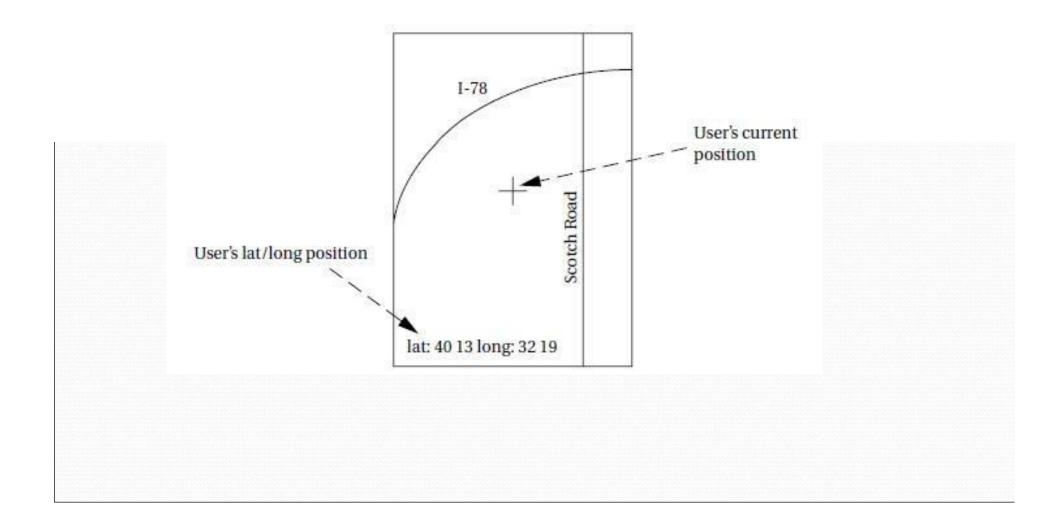

### • <u>GPS moving map</u>

## **Design Process Steps**

- 1. Requirements analysis of a GPS moving map

- The moving map is a handheld device that displays for the user a map of the terrain around the user's current position.

- The map display changes as the user and the map device change position.

- The moving map obtains its position from the GPS, a satellite-based navigation system.

| Name               | GPS moving map                                                                                                      |

|--------------------|---------------------------------------------------------------------------------------------------------------------|

| Purpose            | Consumer-grade moving map for driving use                                                                           |

| Inputs             | Power button, two control buttons                                                                                   |

| Outputs            | Back-lit LCD display 400 600                                                                                        |

| Functions          | Uses 5-receiver GPS system; three user-selectable<br>resolutions; always displays current latitude and<br>longitude |

| Performance        | Updates screen within 0.25 seconds upon movement                                                                    |

| Manufacturing cost | \$30                                                                                                                |

| Power              | 100mW                                                                                                               |

| Physical size and  | No more than 2"X 6, "12 ounces                                                                                      |

| weight             |                                                                                                                     |

## **Design Process Steps**

2) Functionality→This system is designed for highway driving and similar uses. The system should show major roads and other landmarks available in standard topographic databases.

3) User interface → The screen should have at least 400X600 pixel resolution. The device should be controlled by no more than 3 buttons.

→A menu system should pop up on the screen when buttons are pressed to allow the user to make selections to control the system.

4) Performance  $\rightarrow$  The map should scroll smoothly.

→Upon power-up, a display should take no more than 1sec to appear. →The system should be able to verify its position and display the current map within 15 s.

5)Cost→ The selling cost of the unit should be no more than \$100.

6) Physical size and weight→ The device should fit comfortably in the palm of the hand.

7) Power consumption  $\rightarrow$  The device run for at least 8 hrs on 4 AA batteries.

## 8) specification

- 1. Data received from the GPS satellite constellation.

- 2. Map data.

- 3. User interface.

- 4. Operations that must be performed to satisfy customer requests.

- 5. Background actions required to keep the system running, such as operating the GPS receiver.

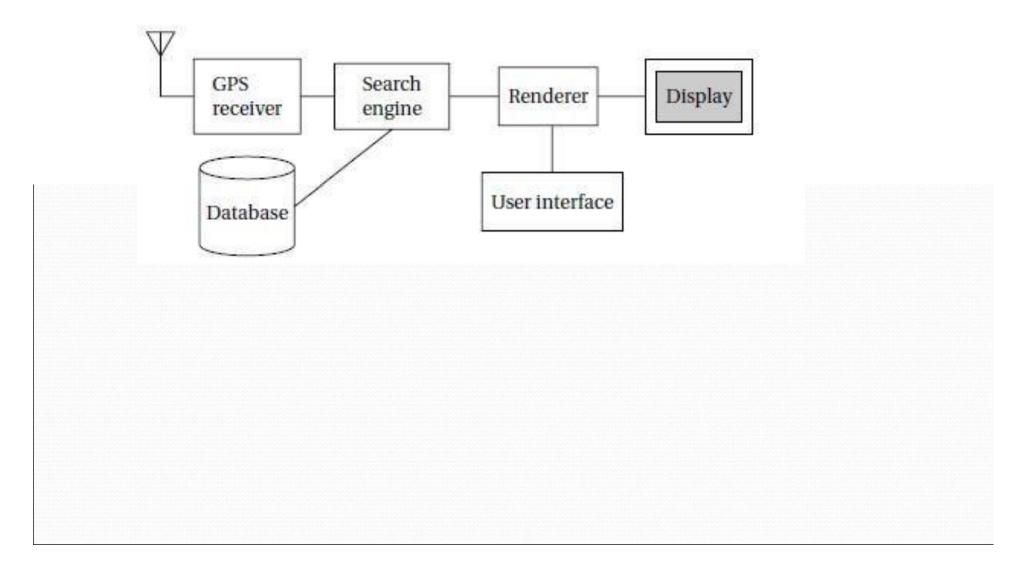

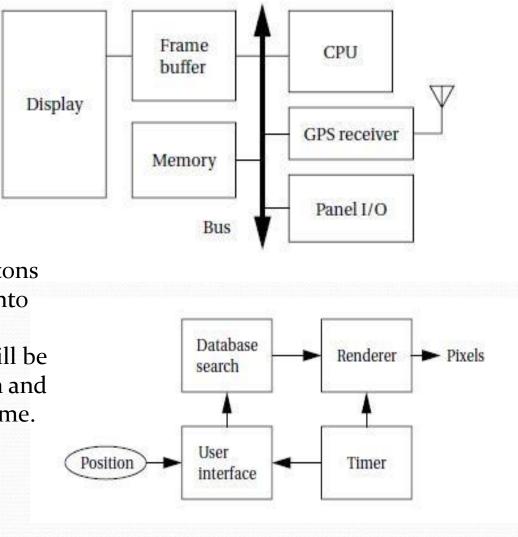

# **Block Diagram**

#### Hardware architecture

one central CPU surrounded by memory and I/O devices.

It used two memories: a frame buffer for the pixels to be displayed and a separate program/data memory for

#### Software architecture

general use by the CPU.

•Timer to control when we read the buttons on the user interface and render data onto the screen.

•Units in the software block diagram will be executed in the hardware block diagram and when operations will be performed in time.

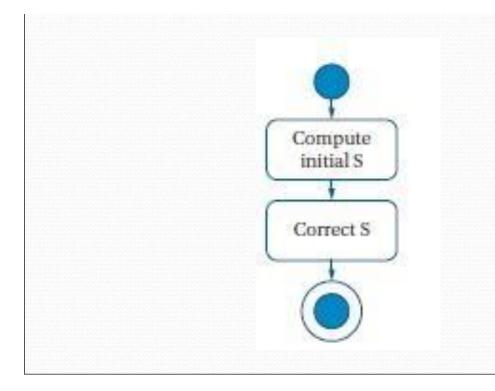

# 3)FORMALISM FOR SYSTEM DESIGN

- UML(Unified Modeling Language) is an object-oriented modeling language→ used to capture all these design tasks.

- It encourages the design to be described as a number of interacting objects, rather than blocks of code.

- objects will correspond to real pieces of software or hardware in the system.

- It allows a system to be described in a way that closely models real-world objects and their interactions.

**Classification of descriptor**

3.1) Structural Description

3.2)Behavioral Description

## **Structural Description**

- It gives basic components of the system and designers can learn how to describe these components in terms of object.

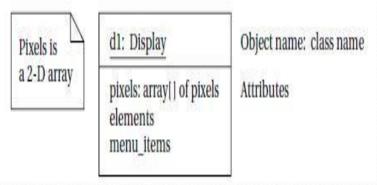

- **OBJECT in UML NOTATION**

- An object includes a set of attributes that define its internal state.

- An object describing a display (CRT screen) is shown in UML notation in Figure.

- The object has a **unique name**, and a member of a **class**.

- The name is underlined to show that this is a description of an object and not of a class.

- The text in the folded-corner page icon is a **note**.

#### An object in UML notation

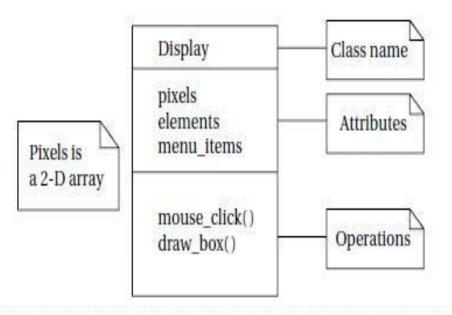

## **CLASS IN UML NOTATION**

- All objects derived from the same class have the same characteristics, but attributes may have different values.

- It also defines the **operations** that determine how the object interacts with the rest of the world.

- It defines both the interface for a particular type of object and that object's implementation.

## Relationships between objects and classes

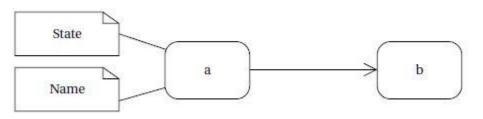

- 1. Association  $\rightarrow$  occurs between objects that communicate with each other but have no ownership relationship between them.

- 2. Aggregation  $\rightarrow$  describes a complex object made of smaller objects.

- 3. Composition  $\rightarrow$  It is a type of aggregation in which the owner does not allow access to the component objects.

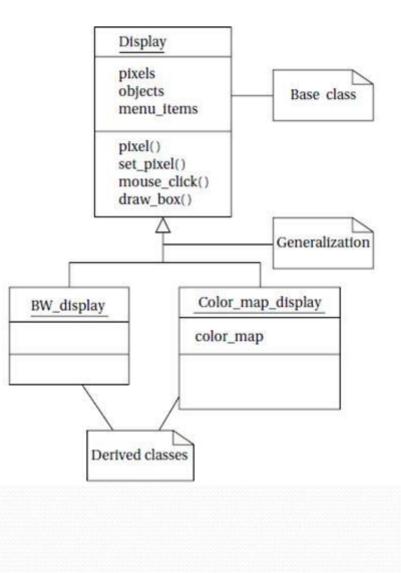

- 4. Generalization  $\rightarrow$  allows us to define one class in terms of another.

#### Derived classes as a form of generalization in UML

•A derived class is defined to include all the attributes of its base class.

Display is the base class and BW display and color map display are the two derived classes.

BW display represents black and white display.

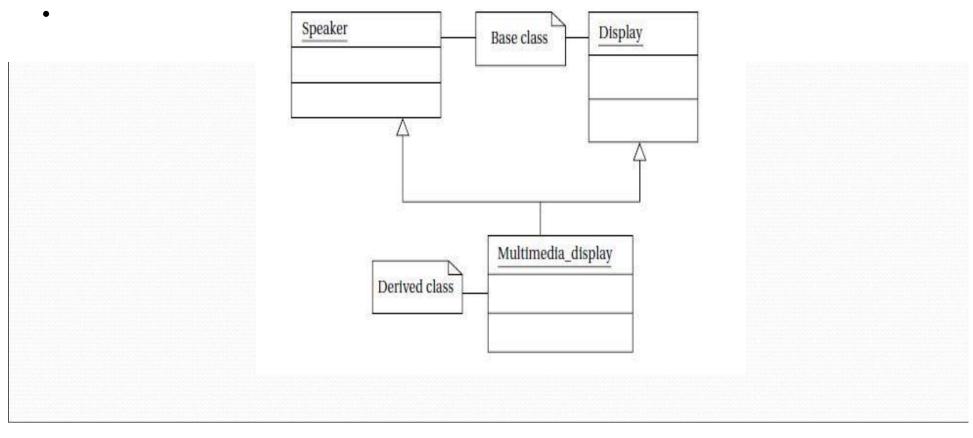

# ultiple inheritance in UML

•UML allows to define multiple inheritance, in which a class is derived from more than one base class.

•Multimedia display class by combining the Display class with a Speaker class for sound.

•The derived class inherits all the attributes and operations of both its base classes, Display and Speaker.

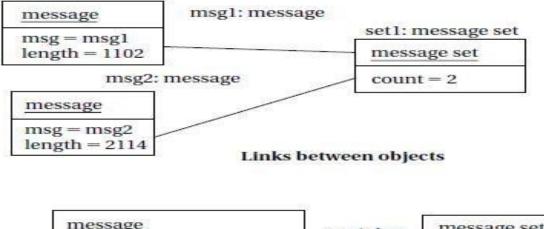

## Links and Association

| message           | contains | message set    |

|-------------------|----------|----------------|

| msg: ADPCM_stream | 0* 1     | count: integer |

| length: integer   |          |                |

- A link describes a relationship between objects and association is to link as class is to object.

- Links used to make to stand associations capture type information about these links.

- The association is drawn as a line between the two labeled with the name of the association, namely, *contains*.

# **Behavioral Description**

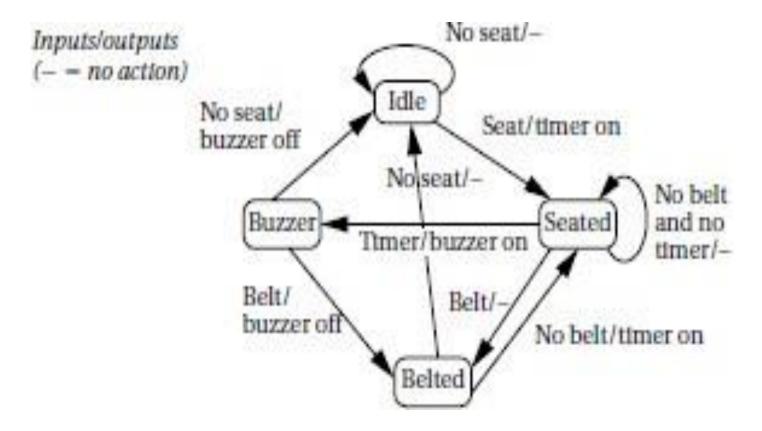

• Behavior of an operation is specified by a state machine.

- These state machines will not rely on the operation of a clock.

- Changes from one state to another are triggered by the occurrence of events.

- The event may generated from the outside or inside of the system.

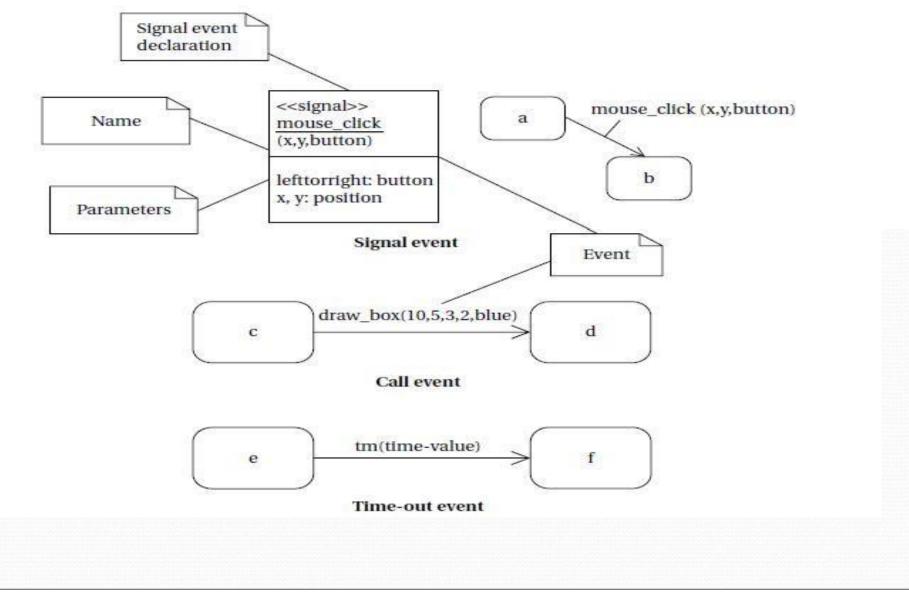

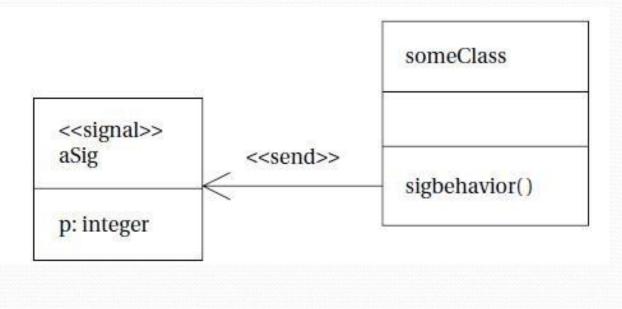

#### Signal, call, and time-out events in UML.

- Signal  $\rightarrow$  is an asynchronous occurrence.

- It is defined in UML by an object that is labeled as a <<signal>>.

- Signal may have parameters that are passed to the signal's receiver.

- Call event→ follows the model of a procedure call in a programming language.

- Time-out event→ causes the machine to leave a state after a certain amount of time.

- The label tm(time-value) on the edge gives the amount of time after which the transition occurs.

- It is implemented with an external timer.

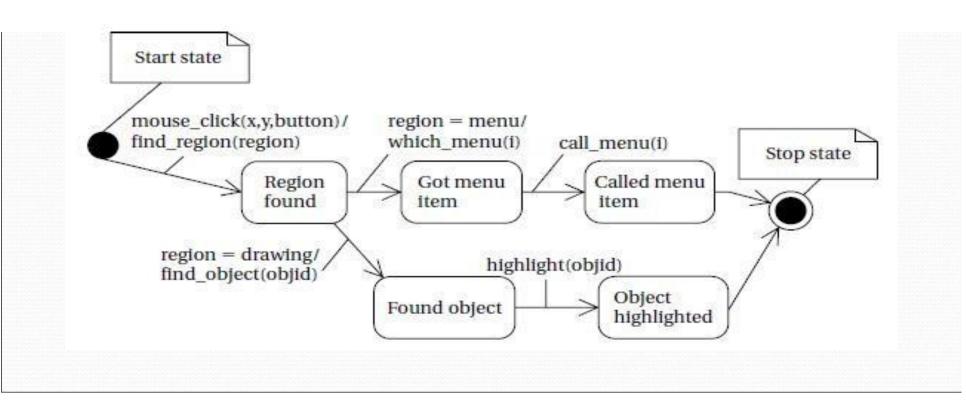

## State Machine specification in UML

- The start and stop states are special states which organize the flow of the state machine.

- The states in the state machine represent different operations.

- Conditional transitions out of states based on inputs or results of some computation.

- An unconditional transition to the next state.

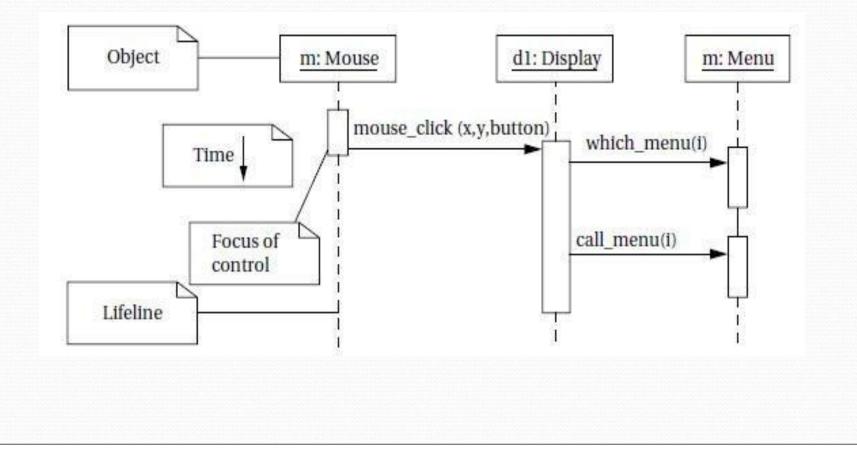

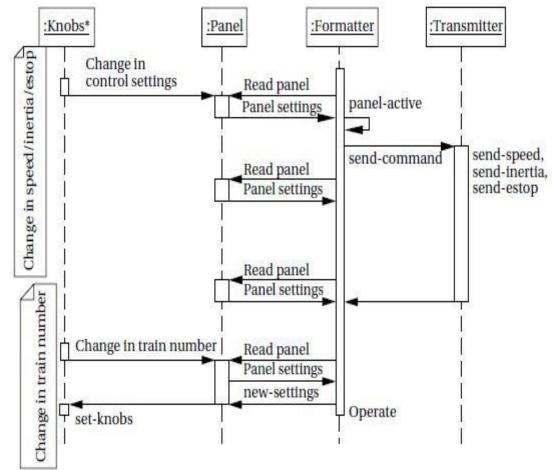

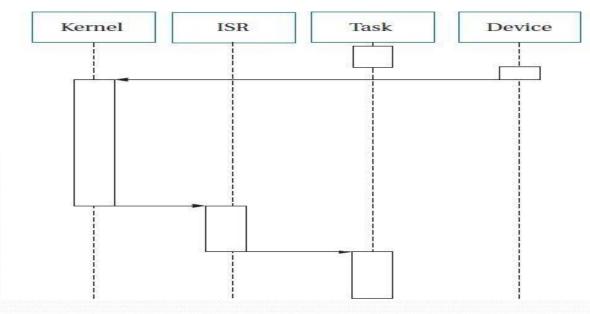

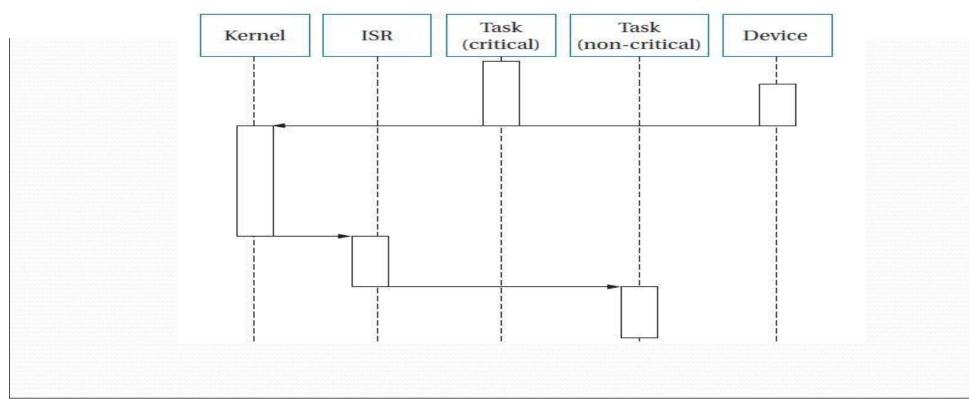

## Sequence diagram in UML

- Sequence diagram is similar to a hardware timing diagram, although the time flows vertically in a sequence diagram, whereas time typically flows horizontally in a timing diagram.

- It is designed to show particular choice of events—it is not convenient for showing a number of mutually exclusive possibilities.

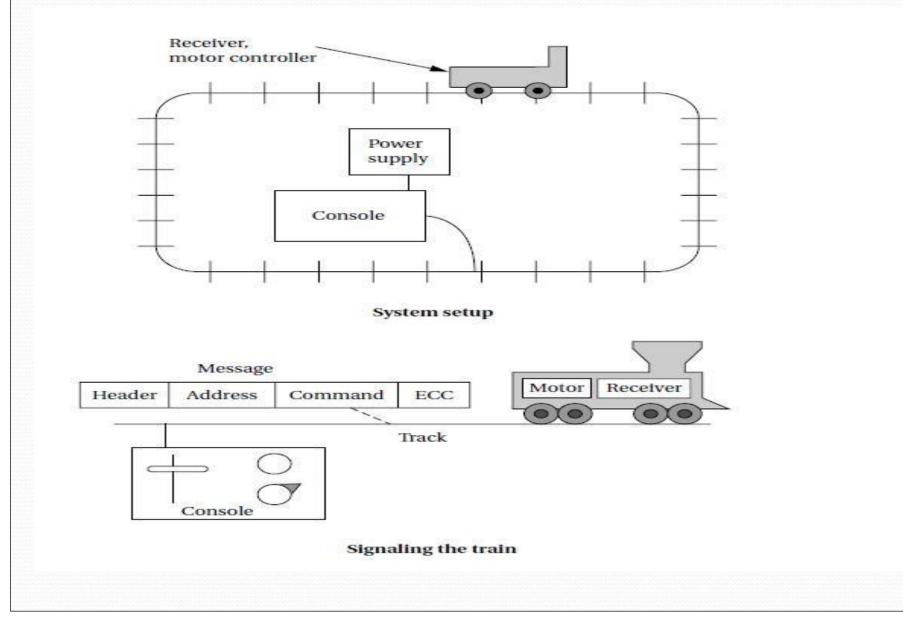

## 4) Design: Model Train Controller

- In order to learn how to use UML to model systems→ specify a simple system (Ex: model train controller)

- The user sends messages to the train with a control box attached to the tracks.

- The control box may have controls such as a throttle, emergency stop button, and so on.

- The train Rx its electrical power from the two rails of the track.

- <u>CONSOLE</u>

- Each packet includes an address so that the console can control several trains on the same track.

- The packet also includes an error correction code (ECC) to guard against transmission errors.

- This is a one-way communication system—the model train cannot send commands back to the user.

## **Model Train Control system**

## REQUIREMENTS

- The console shall be able to control up to eight trains on a single track.

- The speed of each train controllable by a throttle to at least 63 different levels in each direction (forward and reverse).

- There shall be an inertia control  $\rightarrow$  to adjust the speed of train.

- There shall be an emergency stop button.

- An error detection scheme will be used to transmit messages.

# **Requirements:Chart Format**

|   | Name                     | Model train controller                                                                  |

|---|--------------------------|-----------------------------------------------------------------------------------------|

|   | Purpose                  | Control speed of up to eight model trains                                               |

| • | Inputs                   | Throttle, inertia setting, emergency stop, train number                                 |

|   | Outputs                  | Train control signals                                                                   |

| • | Functions<br>respond     | Set engine speed based upon inertia settings;                                           |

|   | Performance              | Can update train speed at least 10 times per second                                     |

|   | Manufacturing cost       |                                                                                         |

|   | Power                    | \$50<br>10W                                                                             |

| • | Physical size and weight | Console should be comfortable for two<br>hands,approximatesize of standard<br>keyboard; |

|   | weight                   | 2 pounds                                                                                |

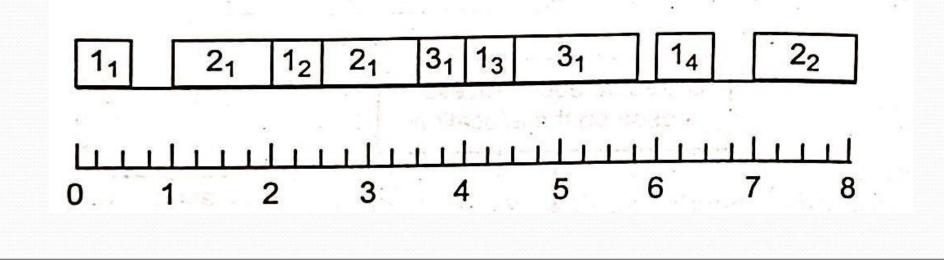

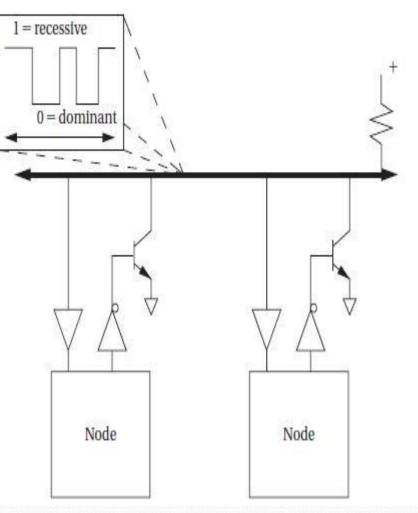

# **Digital Command Control (DCC)**

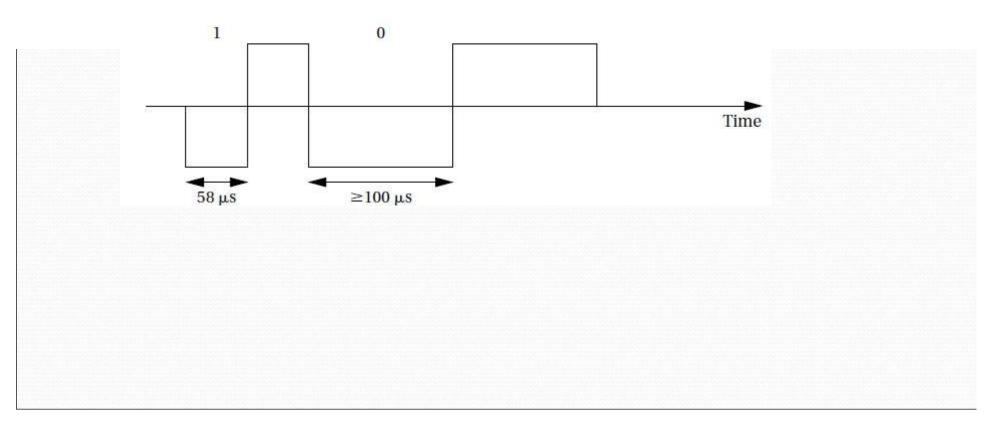

- Standard S-9.1 $\rightarrow$  how bits are encoded on the rails for transmission.

- Standard S-9.2 $\rightarrow$  defines the packets that carry information.

- The signal encoding system should not interfere with power transmission

- Data signal should not change the DC value of the rails.

- Bits are encoded in the time between transitions.

- Bit o is at least 100 s while bit 1 is nominally 58 s.

## Packet Formation in DCC

• The basic packet format is given by

PSA(sD) + E

- $P \rightarrow$  preamble, which is a sequence of at least 10 1 bits.

- $S \rightarrow$  packet start bit. It is a o bit.

- A →address is 8 bits long. The addresses oooooooo, 1111110, and 1111111 are reserved.

- $s \rightarrow$  data byte start bit, which, like the packet start bit, is a o.

- D →data byte includes 8 bits. A data byte may contain an address, instruction, data, or error correction information.

- $E \rightarrow$  packet end bit, which is a 1 bit.

#### **Baseline packet**

- The minimum packet that must be accepted by all DCC implementations.

- It has three data bytes.

- Address data byte → gives the intended receiver of the packet

- Instruction data byte → provides a basic instruction

- Error correction data byte→ is used to detect and correct transmission errors.

#### Date byte

- Bits  $o-3 \rightarrow$  provide a 4-bit speed value.

- Bit 4  $\rightarrow$  has an additional speed bit.

- Bit 5  $\rightarrow$  gives direction, with 1 for forward and 0 for reverse.

- Bits 6-7 are set at on  $\rightarrow$  provides speed and direction.

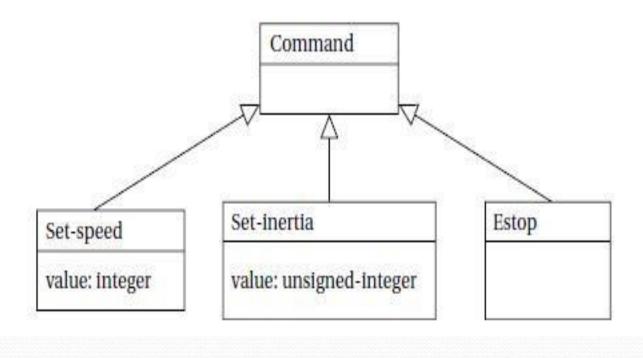

## **Conceptual Specification**

- Conceptual specification allows us to understand the system a little better.

- A train control system turns commands into packets.

- A command comes from the command unit while a packet is transmitted over the rails.

- Commands and packets may not be generated in a 1-to-1 ratio

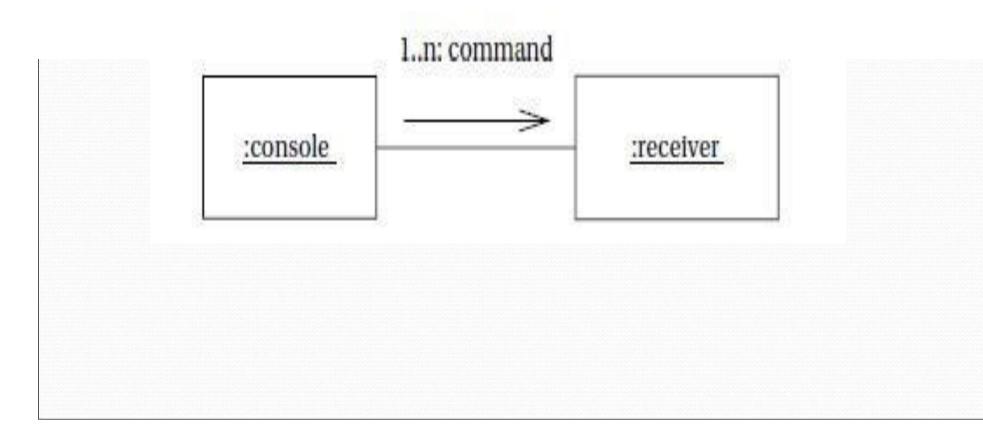

# UML collaboration diagram for train controller system

- The command unit and receiver are each represented by objects.

- The command unit sends a sequence of packets to the train's receiver, as illustrated by the arrow messages as 1..n.

- Those messages are of course carried over the track.

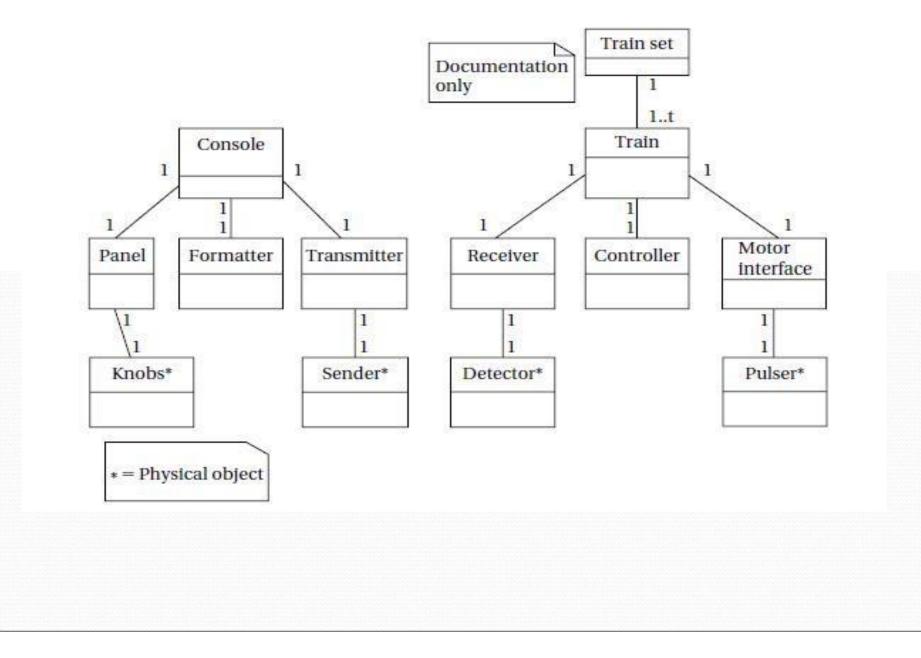

#### UML class diagram for the train controller

#### Basic characteristics of UML classes

- Console class→ describes the command unit's front panel, which contains the analog knobs and hardware to interface to the digital parts of the system.

- *Formatter class* → *includes behaviors that know how to read the panel* knobs and creates a bit stream for the required message.

- *Transmitter class*  $\rightarrow$  *interfaces to analog electronics to send the message* along the track

- Knobs\*→ describes the actual analog knobs, buttons, and levers on the control panel.

- Sender\*→ describes the analog electronics that send bits along the track.

- **Receiver class**  $\rightarrow$  knows how to turn the analog signals on the track into digital form.

- *Controller class*→ *includes behaviors that interpret the commands and* figures out how to control the motor.

- Motor interface class→ defines how to generate the analog signals required to control the motor.

- **Detector**\* → detects analog signals on the track and converts them into digital form.

- Pulser\* → turns digital commands into the analog signals required to control the motor speed.

## **Detailed Specification**

•The Panel has three knobs

• train number (which train is currently being controlled).

•speed (which can be positive or negative), and inertia.

•It also has one button for emergencystop.

•When we change the train number setting, to reset the other controls to the proper values for that train.

• so that the previous train's control settings are not used to change the current train's settings.

Knobs\*

train-knob: integer

speed-knob: integer

inertia-knob: unsigned-integer

emergency-stop: boolean

set-knobs()

| - 1 | -  | -   | -1           | Þ     |

|-----|----|-----|--------------|-------|

| 11  | e  | o   | $\mathbf{r}$ | P     |

| п   | a  | с.  |              |       |

|     | 11 | 118 | lise         | llser |

pulse-width: unsigned-integer direction: boolean

| Sender*    |  |

|------------|--|

| send-bit() |  |

| Detector*                               |

|-----------------------------------------|

|                                         |

| <integer> read-bit(): integer</integer> |

## **Class diagram for panel**

| Panel                   |

|-------------------------|

|                         |

| panel-active(): boolean |

| train-number(): integer |

| speed(): integer        |

| inertia(): integer      |

| estop(): boolean        |

| new-settings()          |

| Motor-interface |  |

|-----------------|--|

| speed: integer  |  |

•The *Panel class* defines a behavior for each of the controls on the panel.

- The new-settings behavior uses the set-knobs behavior of the Knobs\*

- •Change the knobs settings whenever the train number setting is changed.

- •The Motor-interface defines an attribute for speed that can be set by other classes.

#### Class diagram for the Transmitter and Receiver

Transmitter send-speed(adrs: integer, speed: integer) send-inertia(adrs: integer, val: integer) send-estop(adrs: integer) Receiver

current: command new: boolean

read-cmd()

new-cmd(): boolean rcv-type(msg-type: command) rcv-speed(val: integer) rcv-inertia(val: integer)

•They provide the software interface to the physical devices that send and receive bits along the track.

•The Transmitter provides a behavior message that can be sent

• The Receiver class provides a read-cmd behavior to read a message off the tracks.

# **Class diagram for Formatter**

#### Formatter

current-train: integer current-speed[ntrains]: integer current-inertia[ntrains]: unsigned-integer current-estop[ntrains]: boolean

send-command()

panel-active(): boolean

operate()

- The formatter holds the current control settings for all of the trains.

- The *send-command* serves as the interface to the transmitter.

- The operate function performs the basic actions for the object.

- The *panel-active behavior* returns true whenever the panel's values do not correspond to the current values

# **Class diagram for Controller**

Controller

current-train: integer current-speed[ntrains]: unsigned-integer current-direction[ntrains]: boolean current-inertia[ntrains]: unsigned-integer

operate() issue-command()

•The *Controller's operate behavior must execute* several behaviors to determine the nature of the message.

•Once the speed command has been parsed, it must send a sequence of commands to the motor to smoothly change the train's speed.

# Sequences diagram for transmitting a control input

- Sequence diagram specify the interface between more than one classes.

- Its detailed operations and what ways its going to operate

## **DESIGN METHODOLOGIES**

- Design of Embedded system is not an easy task.

- The main goal of a design process is to create a product that does something useful.

- Typical specifications for a product are functionality , manufacturing cost, performance and power consumption.

#### Design process has several important goals as follows

Time-to-market

- Customers always want new features.

- The product that comes out first can win the market, even setting customer preferences for future generations of the product.

#### Design cost

- Consumer products are very cost sensitive, and it is distinct from manufacturing cost.

- Design costs can dominate manufacturing costs.

- Design costs can also be important for high-volume consumer devices when time-to-market pressures cause teams to swell in size.

#### Quality

- Customers want their products fast and cheap.

- Correctness, reliability, and usability must be explicitly addressed from the beginning of the design job to obtain a high-quality product at the end

## Design flows

- A design flow is a sequence of steps to be followed during a design.

- Some of the steps can be performed by tools and other steps can be performed by hand.

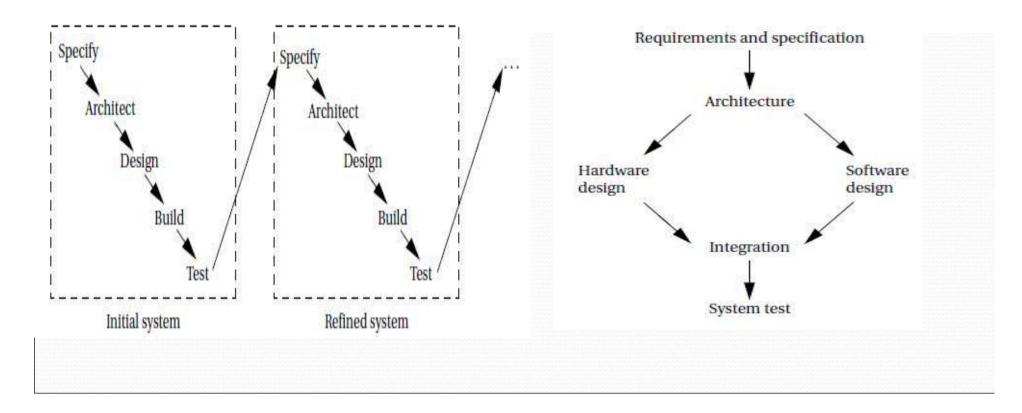

Types of Software development models

- 1. Waterfall model

- 2. Spiral model

- 3. Successive refinement development model

- 4. Hierarchical design model

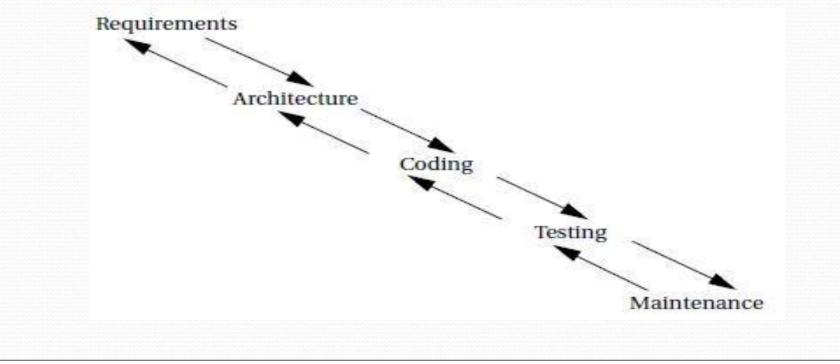

#### Waterfall model

- The waterfall development model consists of five major phases.

- **Requirements analysis** → determines the basic characteristics of the system.

- Architecture design→It decomposes the functionality into major components

- Coding  $\rightarrow$  It implements the pieces and integrates them.

- Testing  $\rightarrow$  It detemines bugs.

- Maintenance → It entails deployment in the field, bug fixes, and upgrades.

- The waterfall model makes work flow information from higher levels of abstraction to more detailed design steps.

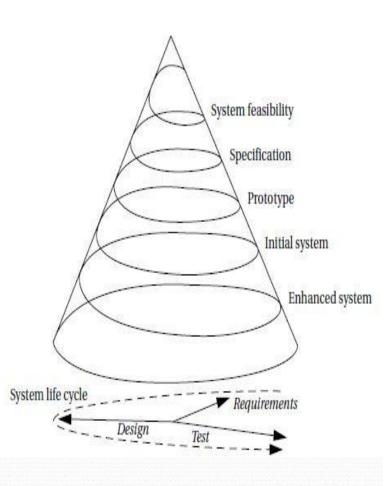

# Spiral model

- The spiral model assumes that several versions of the system will be built.

- Each level of design, the designers go through requirements, construction, and testing phases.

- At later stages when more complete versions of the system are constructed.

- Each phase requires more work, widening the design spiral.

- The first cycles at the top of the spiral are very small and short.

- The final cycles at the spiral's bottom add detail learned from the earlier cycles of the spiral.

- The spiral model is more realistic than the waterfall model because multiple iterations needed to complete a design.

- But too many spirals may take long time required for design.

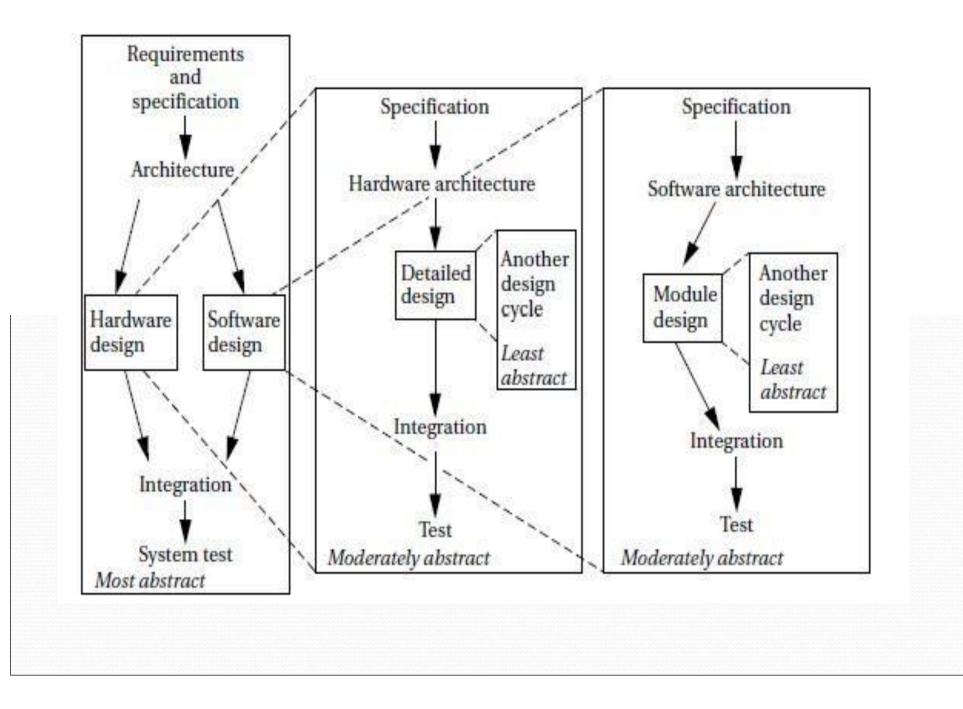

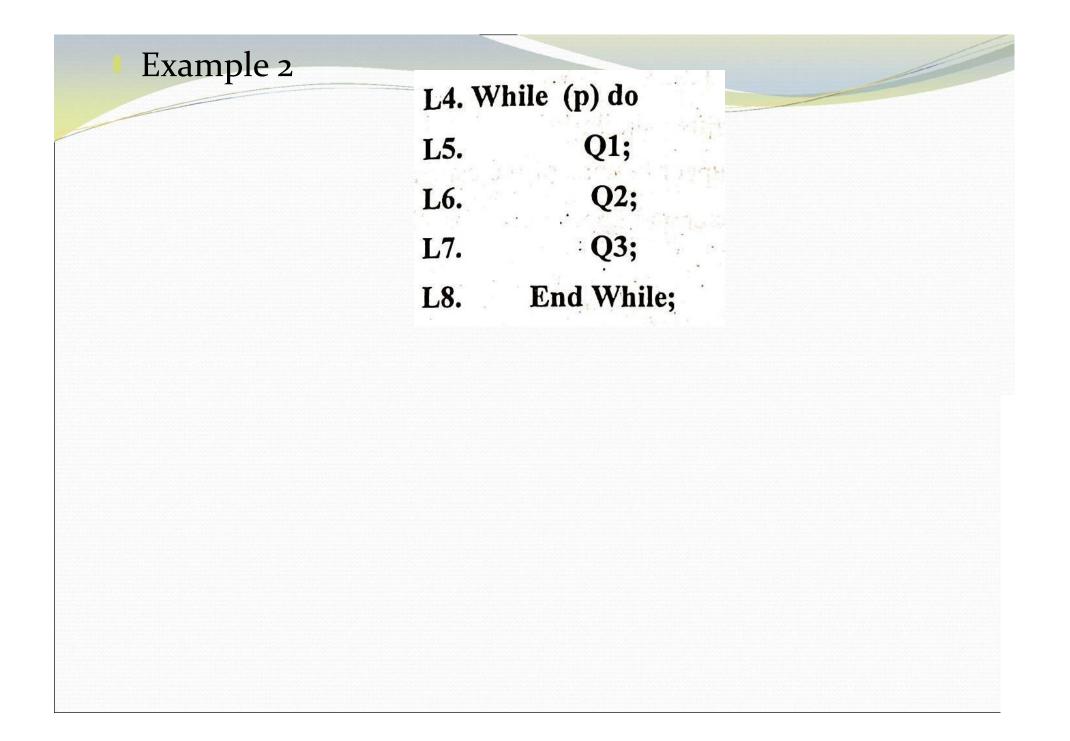

### Successive refinement design model

- In this approach, the system is **built several times**.

- A first system is used as a rough prototype.

- Embedded computing systems are involved the design of hardware/software project.

- Front-end activities→ are specification and architecture and also includes hardware and software aspects.

- Back-end activities → includes integration and testing.

- Middle activities → includes hardware and software development.

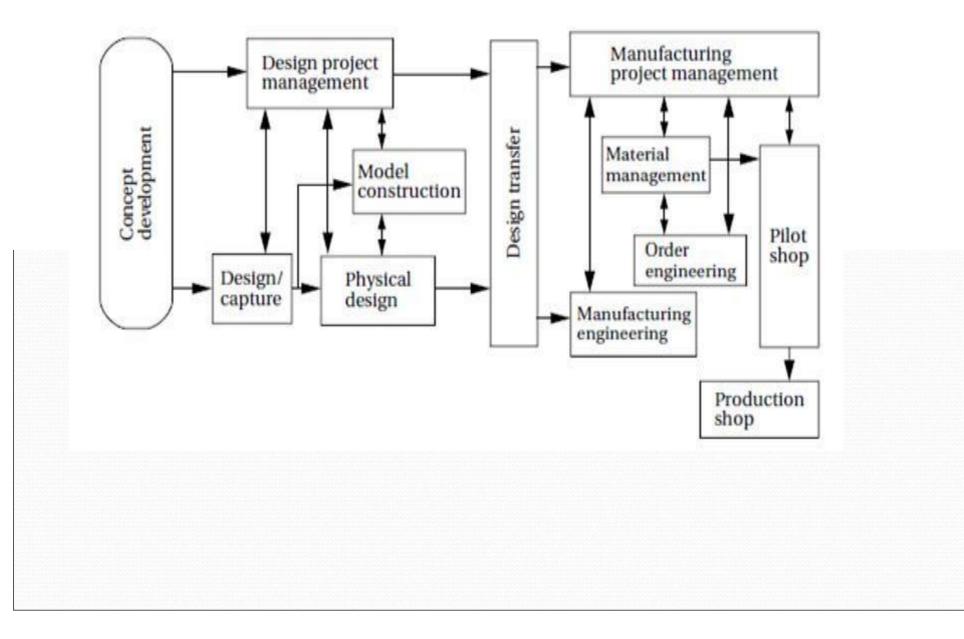

## **Concurrent engineering**

- Reduced design time is an important goal for concurrent engineering.

- It eliminate "over-the-wall" design steps, one designer performs an isolated task and then throws the result to the next designer.

Concurrent engineering efforts are comprised of several elements.

- Cross-functional teams →include members from various disciplines (manufacturing, hardware and software design, marketing)

- **Concurrent product**→ realize the process activities .

- Designing various subsystems simultaneously, is reducing design time.

- Integrated project management → ensures that someone is responsible for the entire project.

- Early and continual supplier → make the best use of suppliers' capabilities.

- Early and continual customer  $\rightarrow$  ensure that the product meets customers' needs.

#### **Concurrent Engineering Applied to Telephone Systems**

- 1. **Benchmarking**→ They compared themselves to competitors and found that it took them 30% longer to introduce a new product than their best competitors.

- 2. Breakthrough improvement.

- Increased partnership between design and manufacturing.

- Continued existence of the basic organization of design labs and manufacturing.

- Support of managers at least two levels above the working level.

- 3. Characterization of the current process.

- Too many design and manufacturing tasks were performed sequentially.

- 4. Create the target process → The core team created a model for the new development process.

- 5. Verify the new process  $\rightarrow$  test the new process.

- 6. **Implement across the product line**→ This activity required training of personnel, documentation of the new standards and procedures, and improvements to information systems.

- 7. **Measure results and improve**  $\rightarrow$  **P**erformance of the new design was measured.

#### **REQUIREMENTS ANALYSIS**

- Requirements→It is a informal descriptions of what the customer wants.

- A functional requirement → states what the system must do.

- A nonfunctional requirement→It can be physical size, cost, power consumption, design time, reliability, and so on.

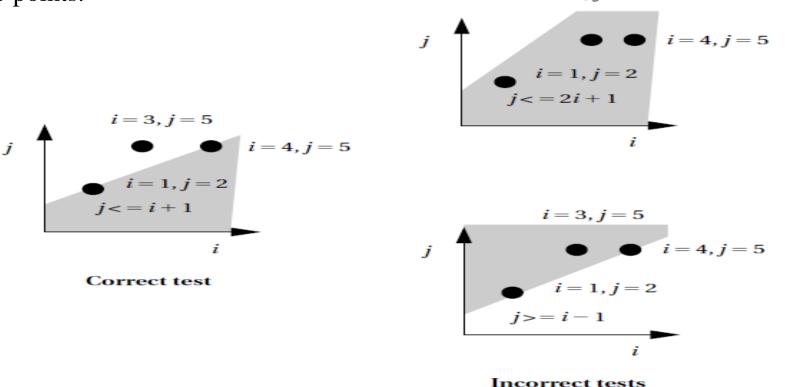

#### Requirements of tests

- Correctness→Requirements should not mistakenly describe what the customer wants.

- Unambiguousness→Requirements document should be clear and have only one plain language interpretation.

- Completeness  $\rightarrow$  Requirements all should be included.

- Verifiability→ cost-effective way to ensure that each requirement is satisfied in the final product.

- Consistency→One requirement should not contradict another requirement.

- Modifiability→The requirements document should be structured so that it can be modified to meet changing requirements without losing consistency.

- Traceability → Able to trace forward /backward from the requirements.

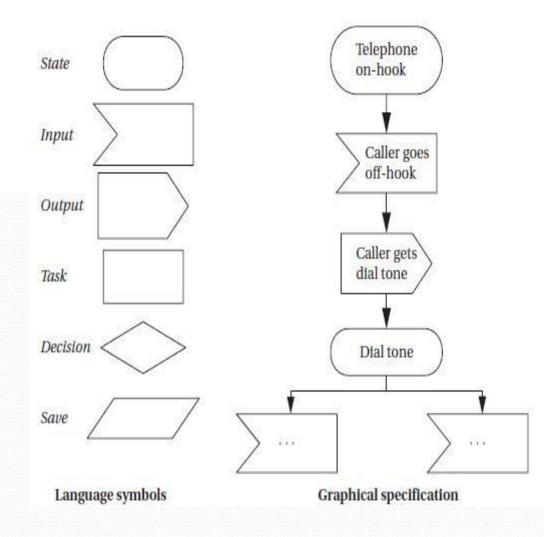

## **SPECIFICATIONS**

Specifications→It is a detailed descriptions of the system that can be used to create the architecture.

#### Control-oriented specification languages

- SDL specifications include states, actions, and both conditional and unconditional transitions between states.

- SDL is an event-oriented state machine model.

- State chart has some important concepts.

- State charts allow states to be grouped together to show common functionality.

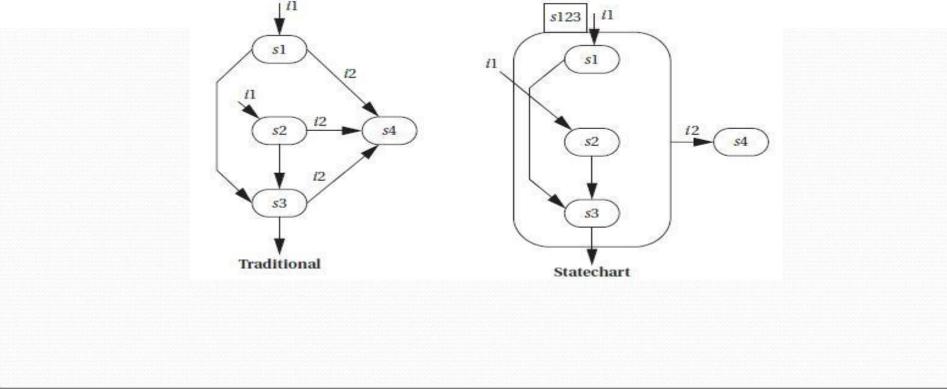

#### Basic groupings(OR)

- State machine specifies that the machine goes to state s4 from any of s1, s2, or s3 when they receive the input i2.

- The State chart denotes this commonality by drawing an OR state around s1, s2, and s3.

- Single transition out of the OR state \$123 specifies that the machine goes to \$4 when it receives the i2 input while in any state included in \$123.

- Multiple ways to get into s123 (via s1 or s2), and transitions between states within the OR state (from s1 to s3 or s2 to s3).

- The OR state is simply a tool for specifying some of the transitions relating to these states.

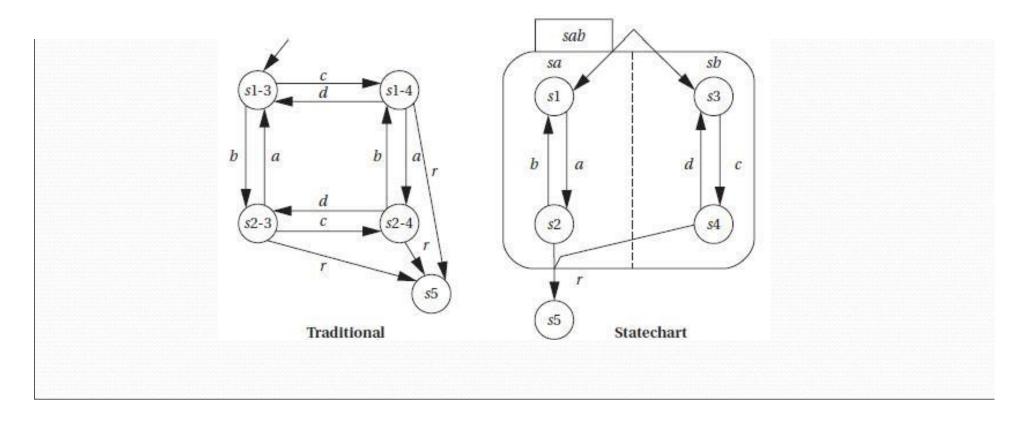

#### Basic groupings(AND)

- In the State chart, the AND state sab is decomposed into two components, sa and sb.

- When the machine enters the AND state, it simultaneously inhabits the state s1 of component sa and the state s3 of component sb.

- When it enters sab, the complete state of the machine requires examining both sa and sb.

- State s1-3 in the State chart machine having its sa component in s1 and its sb component in s3.

- When exit from cluster states go to s5 only when in the traditional specification, we are in state s2-4 and receive input r.

# Advanced specifications

• It ensure the correctness and safety of this system.

Ex→ Traffic Alert and Collision Avoidance System(TCAS)

- It is a collision avoidance system for aircraft.

- TCAS unit in an aircraft keeps track of the position of other nearby aircraft.

- It uses pre-recorded voice ("DESCEND!) commands for mid-air collision.

- TCAS makes sophisticated decisions in real time and is clearly safety critical.

- It must detect as many potential collision events as possible .

- It must generate a few false alarms ,at extreme maneuvers in potentially dangerous.

| TCAS-II s | pecification | RSML | Language) |

|-----------|--------------|------|-----------|

|           | L            | •    |           |

Transition states

| state I  |                   | - |

|----------|-------------------|---|

|          |                   |   |

|          | State description |   |

| Output   |                   |   |

| Outputs: |                   |   |

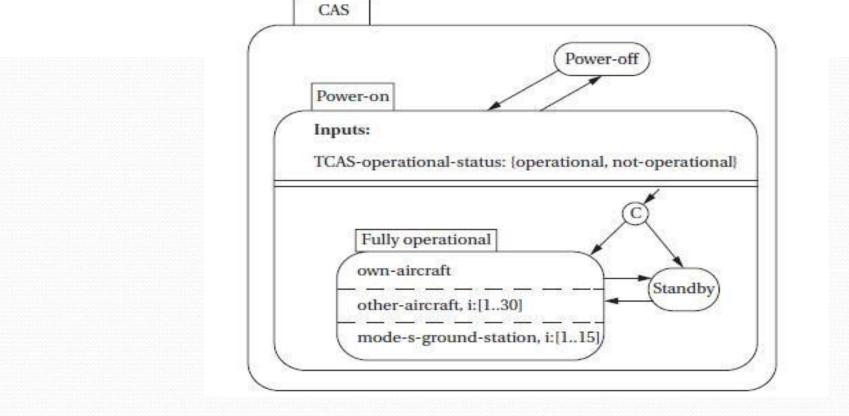

#### Collision Avoidance system

- The system has Power-off and Power-on states .

- In the power on state, the system may be in Standby or Fully operational mode.

- In the Fully operational mode, three components are operating in parallel, as specified by the AND state.

- The own aircraft subsystem to keep track of up to 30 other aircraft.

- Subsystem to keep track of up to 15 Mode S ground stations, which provide radar information.

## SYSTEM ANALYSIS AND ARCHITECTURE DESIGN

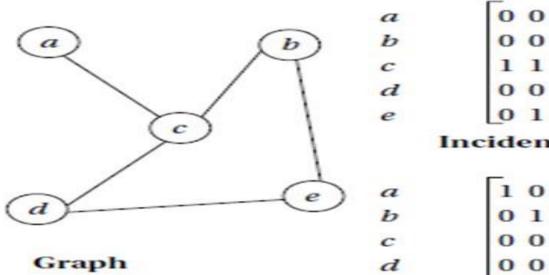

• The CRC card methodology analyze and understanding the overall structure of a complex system.

#### <u>CRC cards</u>

- Classes define the logical groupings of data and functionality.

- **Responsibilities** describe what the classes do.

- Collaborators are the other classes with which a given class works.

- It has space to write down the class name, its responsibilities and collaborators, and other information.

#### Layout of CRC card

| Class name:<br>Superclasses:<br>Subclasses:<br>Responsibilities: Collaborators: | Class name:<br>Class's function:<br>Attributes: |  |

|---------------------------------------------------------------------------------|-------------------------------------------------|--|

| Front                                                                           | Back                                            |  |

- A class may represent a real-world object of the system.

- A class has both an internal state and a functional interface.

- The functional interface describes the class's capabilities.

- The responsibility set is describing that functional interface.

- The collaborators of a class are simply the classes that it talks or calls upon to help it do its work.

- <u>CRC card Analysis Process</u>

- 1. Develop an initial list of classes→Write down the class name and functions of it.

- 2. Write an initial list of responsibilities and collaborators.

- 3. Create some usage scenarios  $\rightarrow$  describe what the system does.

- 4. Walk through the scenarios  $\rightarrow$  Each person on the team represents one or more classes.

- 5. Refine the classes, responsibilities, and collaborators → make changes to the CRC cards.

- 6. Add class relationships→ subclass and super-class can be added to the cards.

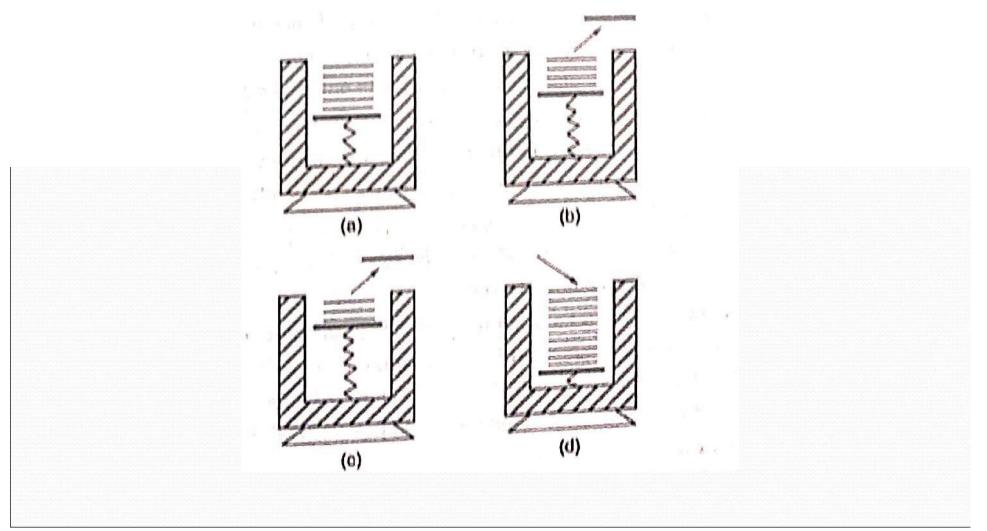

## **Ex:Elevator system**

- 1. One passenger requests a car on a floor, gets in the car when it arrives, requests another floor, and gets out when the car reaches that floor.

- 2. One passenger requests a car on a floor, gets in the car when it arrives, and requests the floor that the car is currently on.

- 3. A second passenger requests a car while another passenger is riding in the elevator.

- 4. Two people push floor buttons on different floors at the same time.

- 5. Two people push car control buttons in different cars at the same time.

| Class                           | Responsibilities                                      | Collaborators                                                                 |

|---------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------|

| Elevator car* Moves up and down |                                                       | Car control, car sensor, car<br>control sender                                |

| Passenger*                      | Pushes floor control and car control buttons          | Floor control, car control                                                    |

| Floor control*                  | Transmits floor requests                              | Passenger, floor control reader                                               |

| Car control*                    | Transmits car requests                                | Passenger, car control reader                                                 |

| Car sensor*                     | Senses car position                                   | Scheduler                                                                     |

| Car state                       | Records current position of car                       | Scheduler, car sensor                                                         |

| Floor control<br>reader         | Interface between floor control and rest of<br>system | Floor control, scheduler                                                      |

| Car control<br>reader           | Interface between car control and rest of<br>system   | Car control, scheduler                                                        |

| Car control sender              | Interface between scheduler and car                   | Scheduler, elevator car                                                       |

| Scheduler                       | Sends commands to cars based upon<br>requests         | Floor control reader, car<br>control reader, car control<br>sender, car state |

## Capability Maturity Model (CMM)

- It is used to measuring the quality of an organization's software development.

- Initial→A poorly organized process, with very few well-defined processes. Success of a project depends on the efforts of individuals, not the organization itself.

- 2. Repeatable→ provides basic tracking mechanisms to understand cost, scheduling .

- 3. Defined→The management and engineering processes are documented and standardized.

- 4. Managed→detailed measurements of the development process and product quality.

- 5. Optimizing→feedback from detailed measurements is used to continually improve the organization's processes.

- Verifying the specification→Discovering bugs early is crucial because it prevents bugs from being released to customers, minimizes design costs, and reduces design time.

- Validation of specifications -> creating the requirements, including correctness, completeness, consistency, and so on

#### **Design reviews**

- The review leader coordinates the pre-meeting activities, the design review itself, and the post-meeting follow-up.

- The reviewer records the minutes of the meeting so that designers and others know which problems need to be fixed.

- The review audience studies the component.

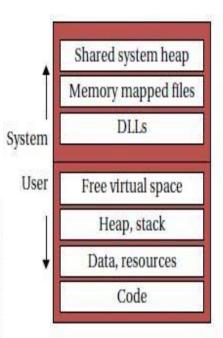

## DESIGNING WITH COMPUTING PLATFORM

### System Architecture

- The architecture of an embedded computing system includes both hardware and software elements

- HARDWARE

- *CPU* → The choice of the CPU is one of the most important, but it can be considered the software that will execute on the machine.

- Bus → The choice of a bus is closely tied to that of a CPU, bus can handle the traffic.

- Memory→Selection depends total size and speed of the memory will play a large part in determining system performance.

- **Input and output devices** → Dependig upon the system requirements

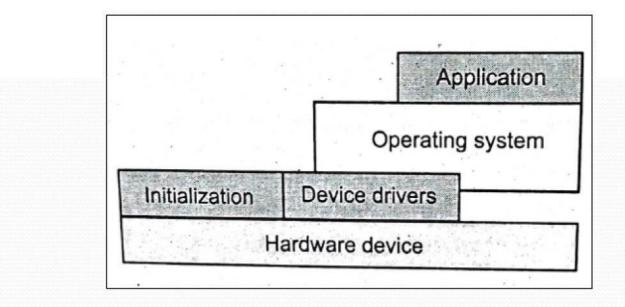

#### **SOFTWARE**

#### Run Time components

- It is a critical part of the platform.

- An operating system is required to control CPU and its multiple processes .

- A file system is used in many embedded systems to organize internal data and interface with other systems

#### Support components

- It is a complex hardware platform.

- Without proper code development and operating system, the hardware itself is useless.

## **ARM** evaluation board

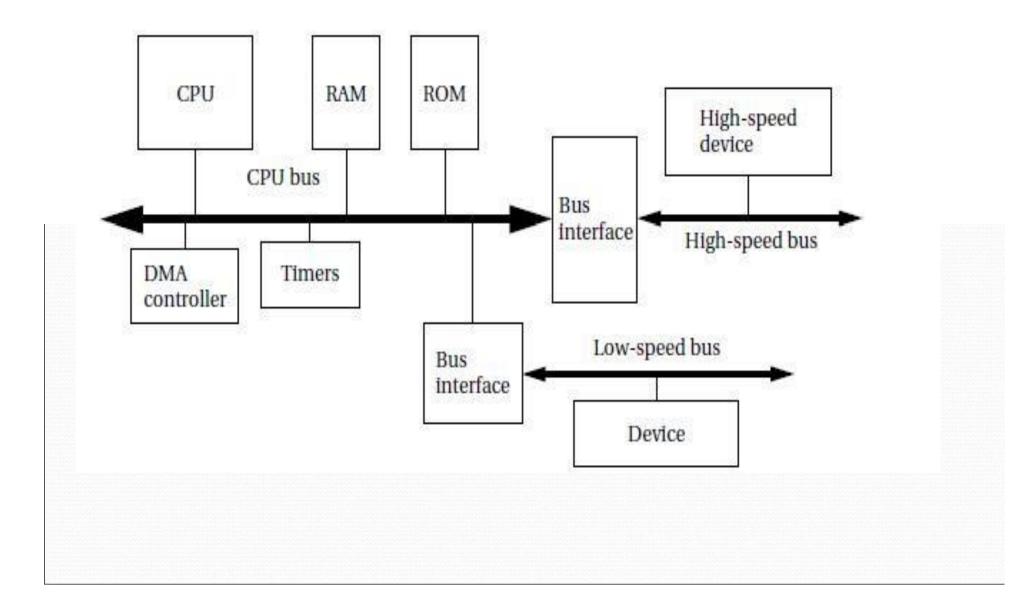

# 1.10.2) The PC as a Platform

- **CPU** → provides basic computational facilities.

- **RAM** $\rightarrow$  is used for program storage.

- ROM $\rightarrow$  holds the boot program.

- DMA→controller provides DMA capabilities.

- Timers→ used by the operating system for a variety of purposes.

- High-speed bus→connected to the CPU bus through a bridge, allows fast devices to communicate with the rest of the system.

- low-speed bus→ provides an inexpensive way to connect simpler devices.

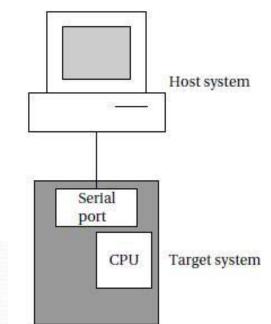

# Development Environments

- Development process → used to make a complete design of the system.

- It guides the developers how to design a system .

- An embedded computing system has CPU ,memory, I/O devices.

- Development of embedded system have both hardware& software.

- The software development on a PC or workstation known as a host.

- The host and target are frequently connected by a USB link.

The target must include a small amount of software to talk to the host system.

#### Functions of Host system

- Load programs into the target

- Start and stop program execution on the target

- Examine memory and CPU registers.

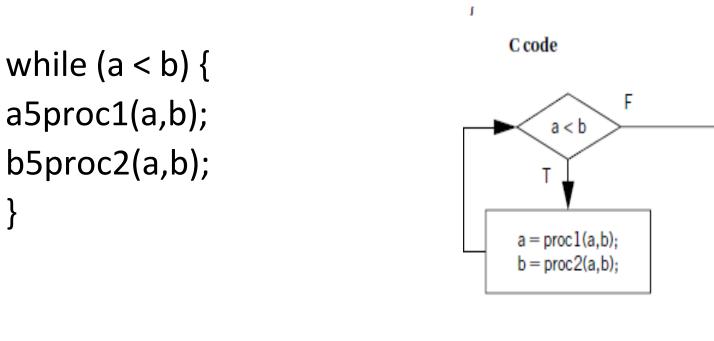

#### Cross-Compiler

- Compiler→ kind of software that translate one form of pgm to another form of pgm.

- Cross Compiler → is a compiler that runs on one type of machine but generates

- code for another

- After compilation, the executable code is downloaded to the embedded system by a serial link.

- A PC or workstation offers a programming environment .

- But one problem with this approach emerges when debugging code talks to I/O devices.

- **Testbench program** → can be built to help debug the embedded code.

- It may also take the output values and compare them against expected values.

# **Debugging Techniques**

- It is the process of checking errors and correcting those errors.

- It can be done by compiling and executing the code on a PC or workstation.

- It can be performed by both H/W and S/W sides.

#### Software debugging tools

- 1. <u>Serial Port tool</u>

- It will perform the debugging process from the initial state of embedded system design.

- It can be used not only for development debugging but also for diagnosing problems in the field.

- 2. <u>Breakpoints tool</u>

- user to specify an address at which the program's execution is to break.

- When the PC reaches that address, control is returned to the monitor program.

- From the monitor program, the user can examine and/or modify CPU registers, after which execution can be continued.

•Breakpoint is a location in memory at which a program stops executing and returns to the debugging tool or monitor program.

To establish a breakpoint at location ox4oc in some ARM code, replaced the branch (B) instruction with a subroutine call (BL) to the breakpoint handling routine

$$0 \times 400 \text{ MUL } r4, r4, r6$$

$0 \times 400 \text{ MUL } r4, r4, r6$  $0 \times 404 \text{ ADD } r2, r2, r4$  $\longrightarrow 0 \times 404 \text{ ADD } r2, r2, r4$  $0 \times 408 \text{ ADD } r0, r0, \#1$  $0 \times 408 \text{ ADD } r0, r0, \#1$  $0 \times 40c \text{ B loop}$  $0 \times 40c \text{ BL bkpoint}$

- <u>Hardware debugging tools</u>

- Hardware can be deployed to give a clearer view on what is happening when the system is running.

- 1. <u>Microprocessor In-Circuit Emulator (ICE)</u>

- It is a specialized hardware tool that can help debug software in a working embedded system.

- In-circuit emulator is a special version of the microprocessor that allows its internal registers to be read out when it is stopped

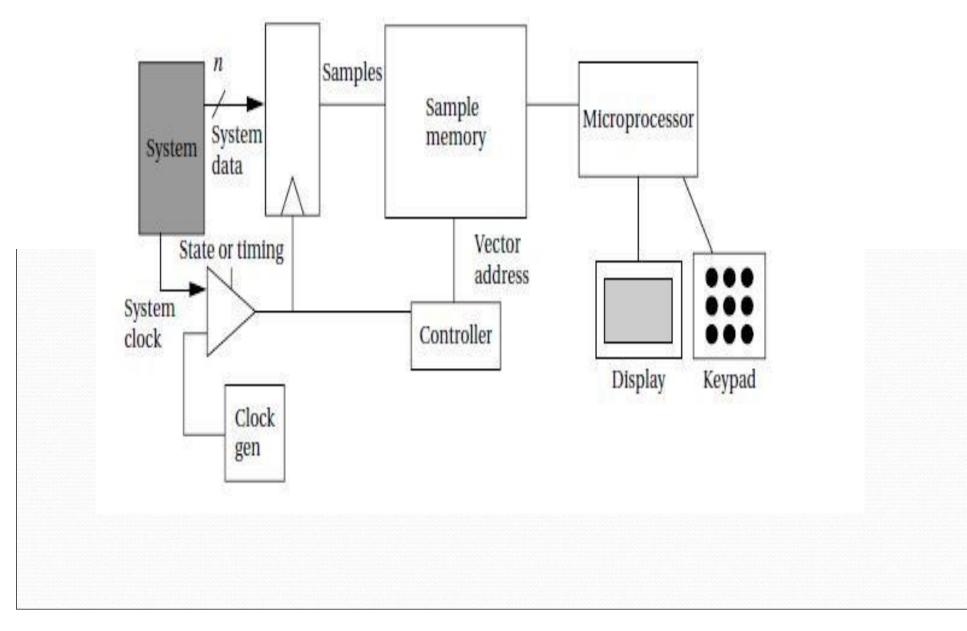

- 2. <u>Logic Analyer</u>

- The analyzer can sample many different signals simultaneously but can display only 0, 1, or changing values for each.

- The logic analyzer records the values on the signals into an internal memory and then displays the results on a display once the memory is full.

# Architecture of a logic analyzer

## Data modes of logic analyzer

#### State modes

- State mode represent different ways of sampling the values.

- It uses the own clock to control sampling

- It samples each signal only one per clock cycle.

- It has less memory to store a given number of system clock.

#### Timing modes

Timing mode uses an internal clock that is fast enough to take several samples per clock period in a typical system.

## 1.10.5) Debugging Challenges

- Logical errors in software can be hard to track down and it will create many problems in real time code.

- Real-time programs are required to finish their work within a certain amount of time.

- Run time pgm run too long, they can create very unexpected behavior.

- Missing of Deadline makes debugging process as difficult.

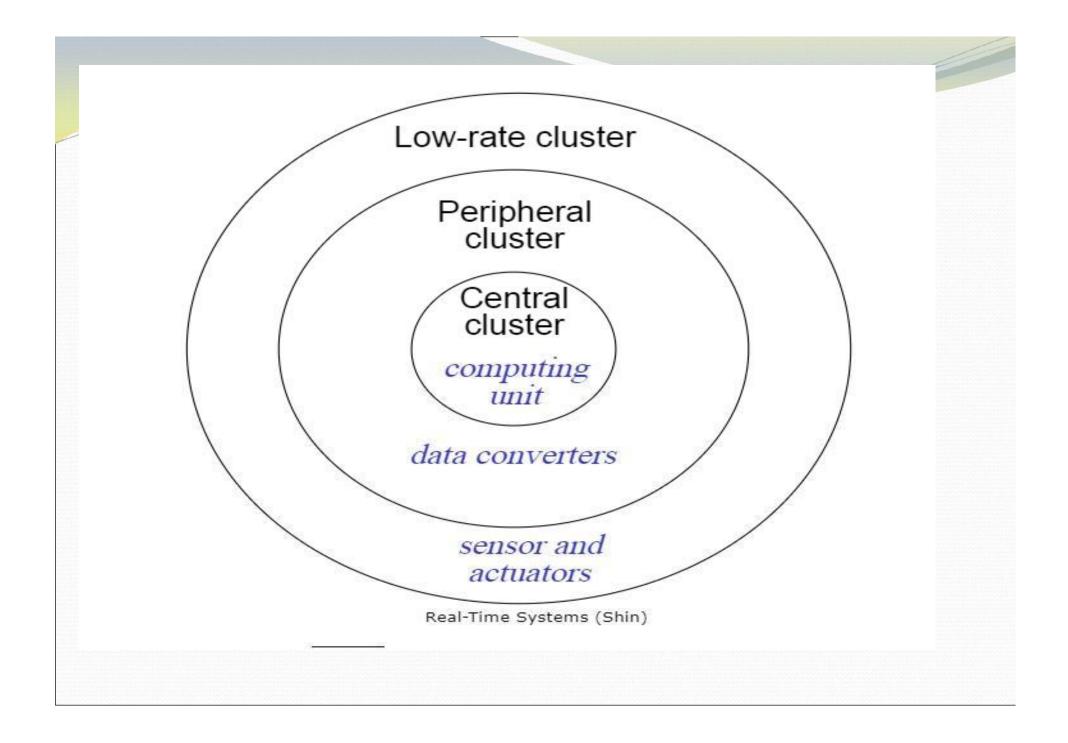

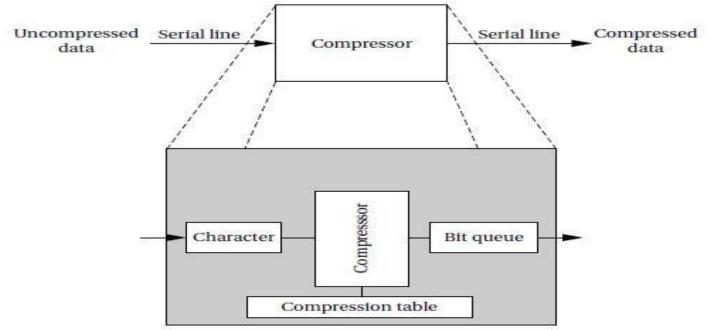

# **Consumer Electronic Architecture**

- Consumer electronic refers to any device containing an electronic circuit board that is intended for energyday use by individuals.

- Eg→TV,cameras,digital cameras,calculators,DVDs,audio devices,smart phones etc..,

#### 1.11.1) Functional Requirements

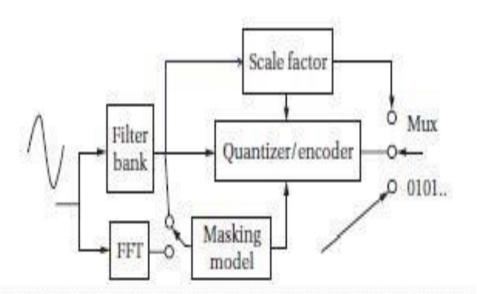

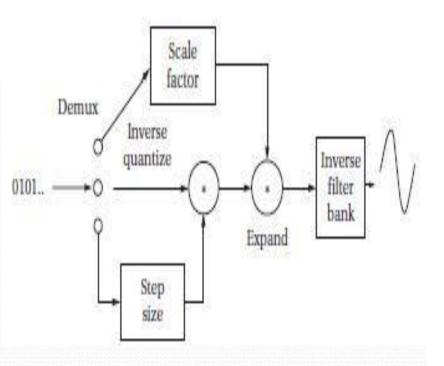

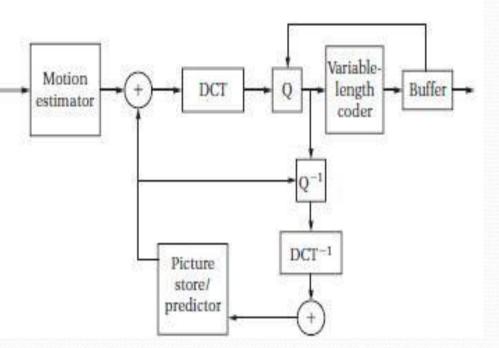

- 1. <u>Multimedia</u>

- The media may be audio, still images, or video.

- These multimedia objects are generally stored in compressed form and must be uncompressed to be played .

- Eg $\rightarrow$  multimedia compression standards (MP3, Dolby Digital(TM))

- audio; JPEG for still images; MPEG-2, MPEG-4, H.264, etc. for video.

- Data storage and management → People want to select what multimedia objects they save or play, data storage goes hand-in-hand with multimedia capture and display. Many devices provide PC-compatible file systems so that data can be shared more easily.

- 3. *Communications* **→ Communications** may be relatively **simple**, such as a USB

- and another is Ethernet port or a cellular telephone link.

#### Non-Functional Requirements

- Many devices are **battery-operated**, which means that they must operate under strict energy budgets.

- Battery(75mW) → support not only the processors but also the display, radio, etc.

- Consumer electronics must also be very inexpensive but provide very high performance.

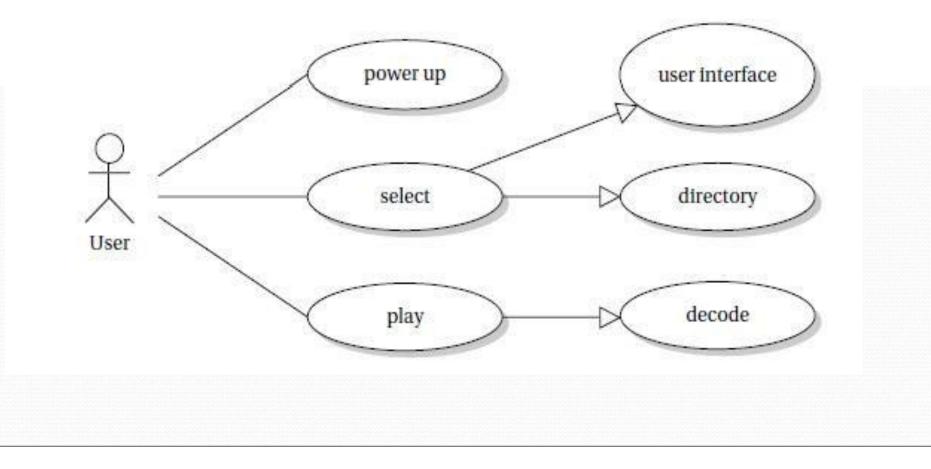

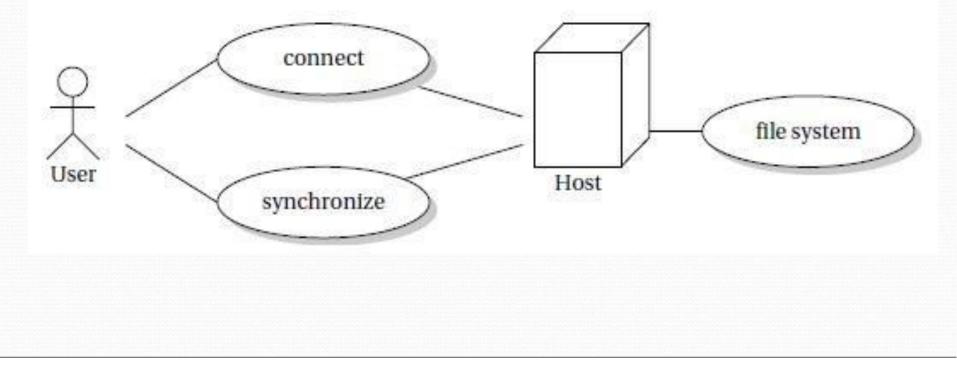

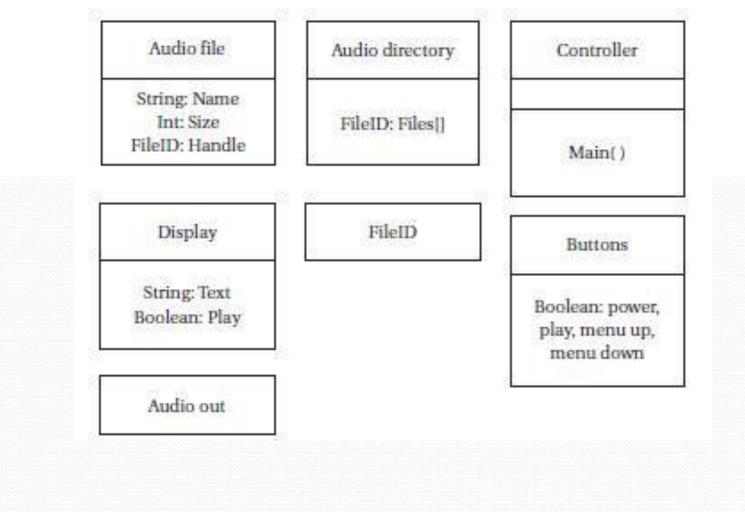

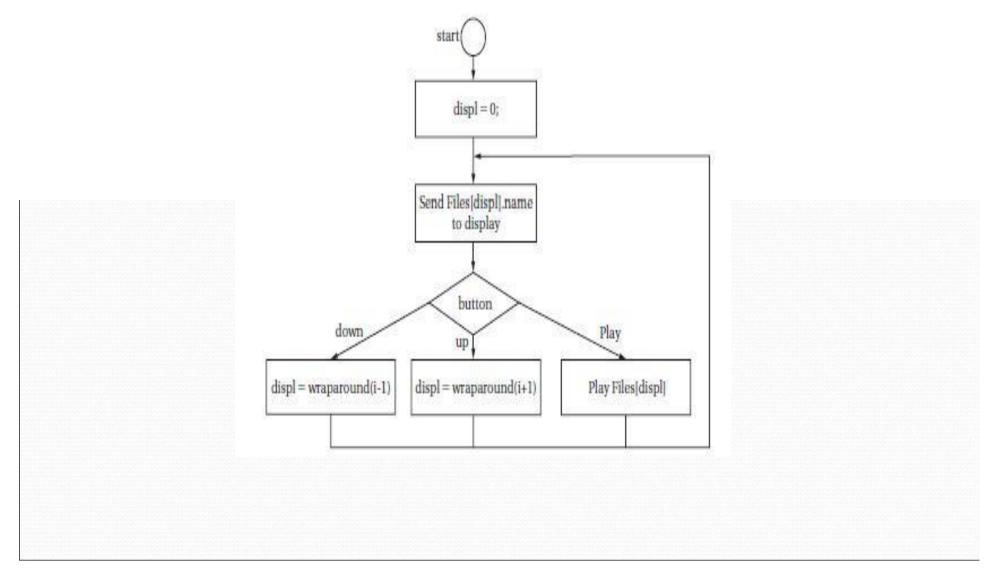

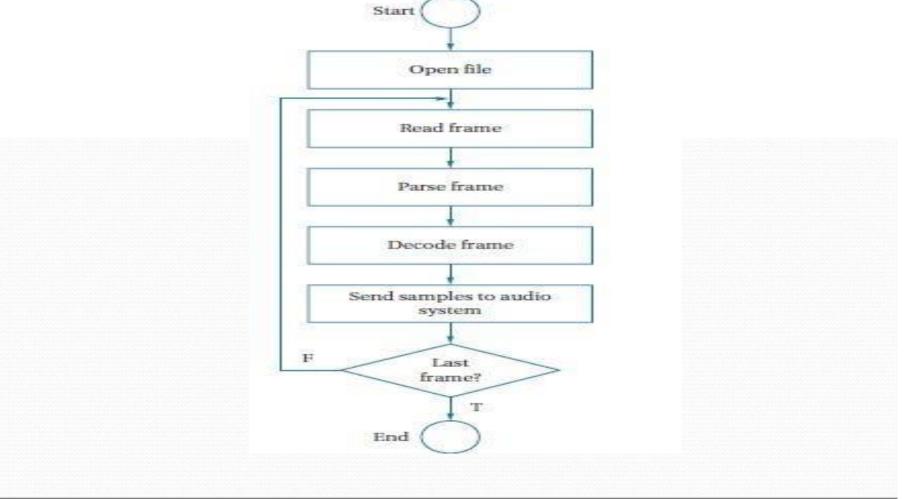

# Use case for playing multimedia

- use case for selecting and playing a multimedia object (audio clip, a picture, etc.).

- Selecting an object makes use of both the user interface and the file system.

- Playing also makes use of the file system as well as the decoding subsystem and I/O subsystem.

# Use case of synchronizing with a host system

- use case for connecting to a client.

- The connection may be either over a local connection like USB or over the Internet.

- Some operations may be performed locally on the client device

- most of the work is done on the host system while the connection is established

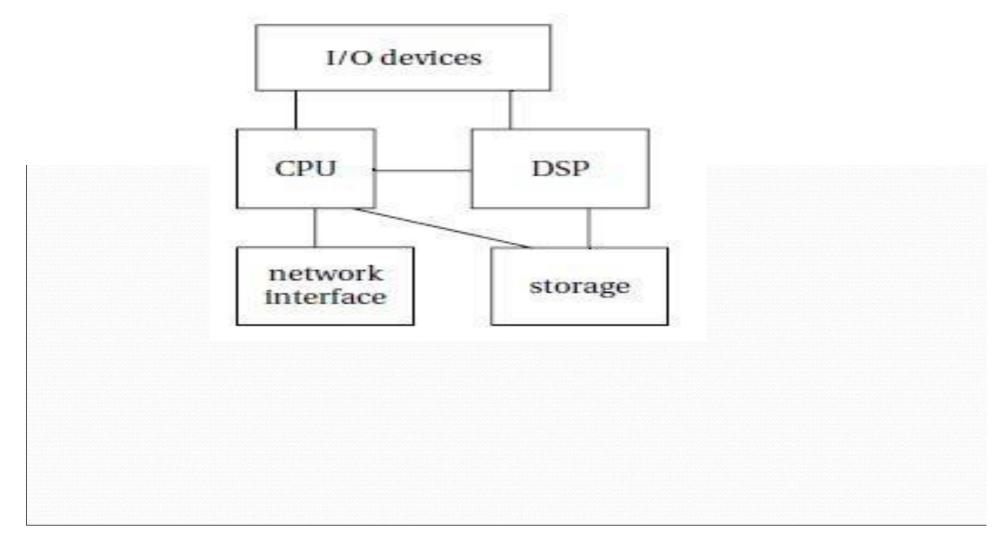

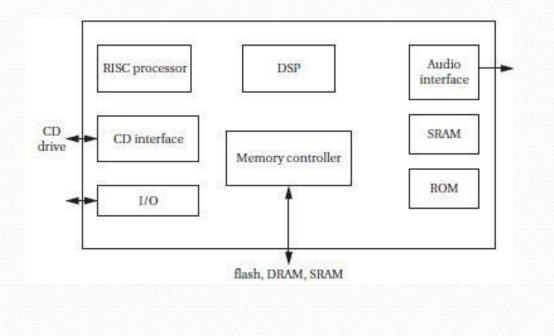

# Functional architecture of Consumer Electronics Device(CED)

- It is a two-processor architecture.

- If more computation is required, more DSPs and CPUs may be added.

- The RISC-CPU runs the operating system, runs the user interface, maintains the file system, etc.

- **DSP** $\rightarrow$  it is a programmable one, which performs signal processing.

- Operating system→ runs on the CPU must maintain processes and the file system.

- Depending on the complexity of the device, the operating system may not need to create tasks dynamically.

- If all tasks can be created using initialization code, the operating system can be made smaller and simpler.

# 1.11.4 Flash File Systems

- Many consumer electronics devices use flash memory for mass storage.

- Flash memory is a type of semiconductor memory ,unlike DRAM or SRAM, provides permanent storage.

- Values are stored in the flash memory cell as electric charge using a specialized capacitor that can store the charge for years.

- The file system of a device is typically shared with a PC.

- Standard file system→has two layers.bottom layer handles physical reads and writes on the storage device and the top layer provides a logical view of the file system.

- Flash file system → imposes an intermediate layer that allows the logicalto-physical mapping of files to be changed.

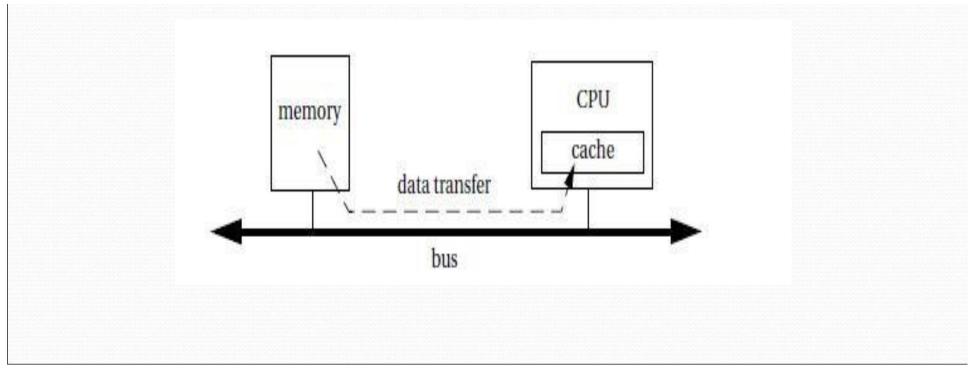

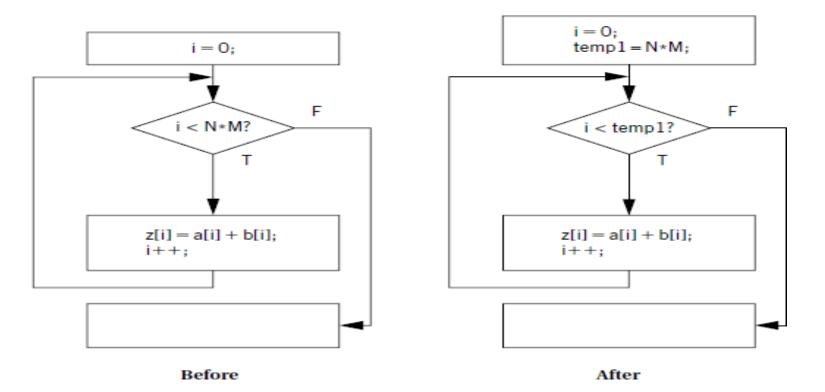

## **Platform-Level Performance Analysis**

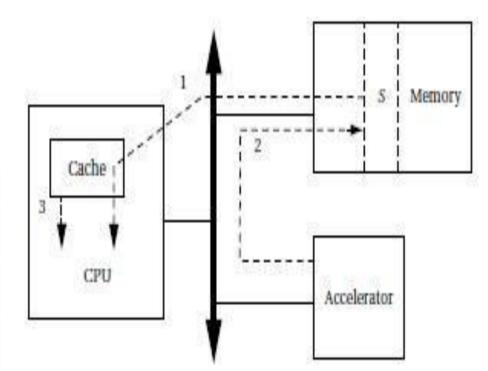

- System-Level Performance involves much more than the CPU.

- To move data from memory to the CPU to process it. To get the data from memory to the CPU we must.

- 1. **Read** from the memory.

- 2. Transfer over the bus to the cache.

- 3. Transfer from the cache to the CPU.

- The performance of the system based on **Bandwidth** of the system.

- We can increase bandwidth in two ways:

- 1) By increasing the clock rate of the bus

- 2) By increasing the amount of data transferred per clock cycle.

For example, bus to carry four bytes or 32 bits per transfer, we would reduce the transfer time to 0.058 s. If we also increase the bus clock rate to 2 MHz, then we would reduce the transfer time to 0.029 s ,which is within our time budget for the transfer.

## t=TP

t→bus cycle counts T→bus cycles. p→bus clock period

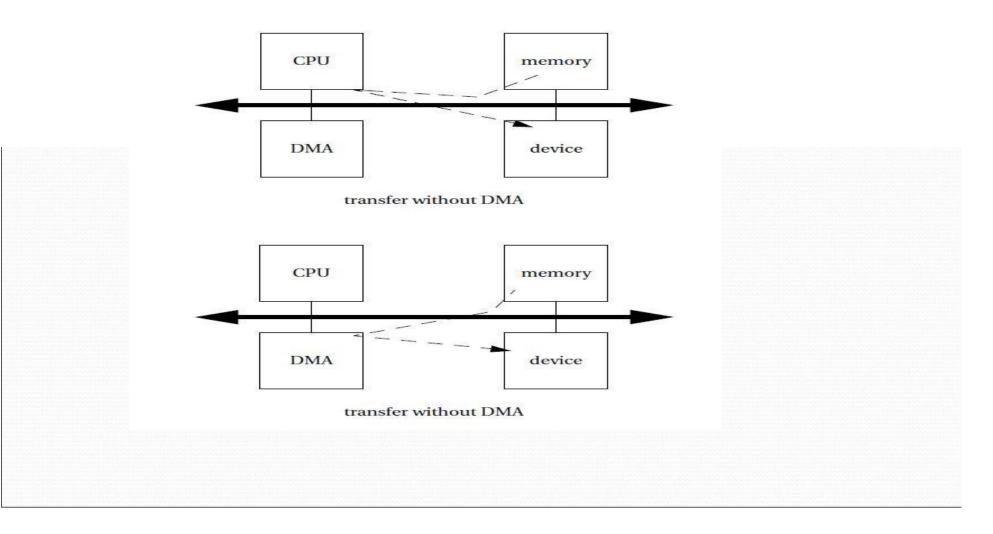

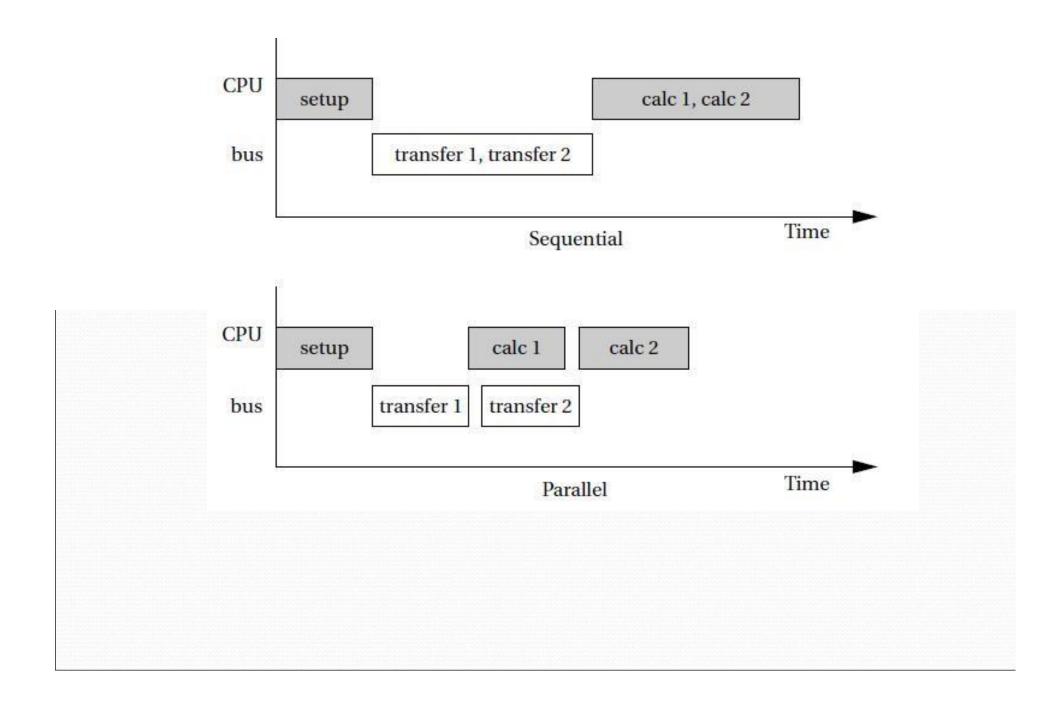

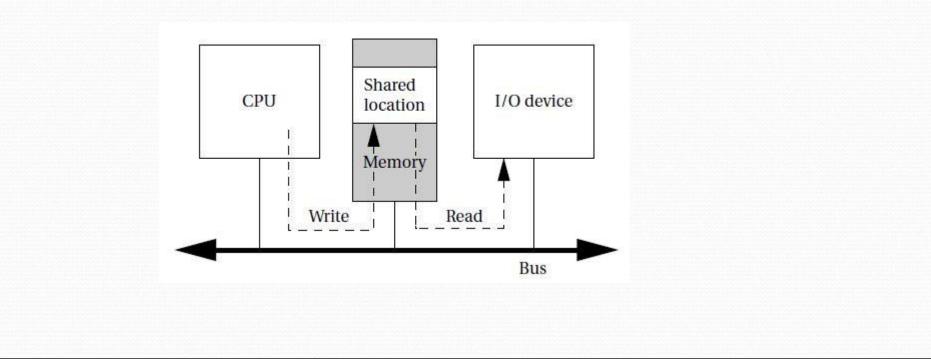

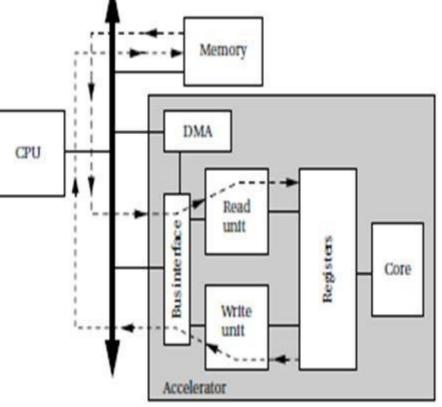

## Parallelism

- Direct memory access is a example of parallelism.

- DMA was designed to off-load memory transfers from the CPU.

- The CPU can do other useful work while the DMA transfer is running.

### UNIT II

#### **ARM PROCESSOR AND PERIPHERALS**

ARM Architecture Versions – ARM Architecture – Instruction Set

– Stacks and Subroutines – Features of the LPC 214X Family –

Peripherals – The Timer Unit – Pulse Width Modulation Unit –

UART – Block Diagram of ARM9 and ARM Cortex M3 MCU.

## **ARM** Architecture Versions

- The ARM processor is a Reduced Instruction Set Computer (RISC).

- The first ARM processor was developed at Acorn Computers Limited, of Cambridge, England, between October 1983 and April 1985. It is very simple architecture.

- At that time, and until the formation of Advanced RISC Machines Limited (which later was renamed simply ARM Limited) in 1990, ARM stood for Acorn RISC Machine

- Second, both ARM ISA and pipeline design are aimed to minimize the energy consumption.

- Third, the ARM architecture is highly modular only mandatory component of ARM processor is the integer pipeline, others are optional. This gives more flexibility in application dependent architecture

| Revision | Example core<br>implementation | ISA Enhancement                                                                                                                                                                                                                                                          |

|----------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARM v1   | ARM1                           | <ul><li>First ARM Processor</li><li>26bit addressing</li></ul>                                                                                                                                                                                                           |

| ARMv2    | ARM2                           | •32bit multiplier<br>•32bit coprocessor<br>support                                                                                                                                                                                                                       |

| ARMv2a   | ARM3                           | <ul> <li>On chip cache</li> <li>Atomic swap instruction</li> <li>Coprocessor 15 for cache<br/>management</li> </ul>                                                                                                                                                      |

| ARMv3    | ARM6 and ARM7DI                | <ul> <li>•32 bit addressing</li> <li>•Separate cpsr (current<br/>Program status<br/>register) and spsr</li> <li>(Saved program status<br/>register)</li> <li>•New modes undefined<br/>instruction and abort</li> <li>•MMU support(Memory<br/>Management Unit)</li> </ul> |

| ARMv3M  | ARM7M              | Signed and un signed<br>long multiply<br>instruction                                                                                                                                                                                      |

|---------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARMv4   | Strong ARM         | <ul> <li>load store instructions<br/>for signed half<br/>words/bytes</li> <li>Reserve SWI(software<br/>interrupt) space fro<br/>architecturally define<br/>operations.</li> <li>26 bit addressing mode<br/>no longer supported</li> </ul> |

| ARMv4T  | ARM7TDMI and ARM9T | •Thumb                                                                                                                                                                                                                                    |

| ARMV5TE | ARM9E AND ARM10E   | <ul> <li>Superset of ARM</li> <li>Enhanced multiply<br/>instructions</li> <li>Extra DSP type<br/>instruction</li> <li>Faster multiply<br/>instruction</li> </ul>                                                                          |

| ARM V5tej | ARM7EJ & ARM926EJ | Java Acceleration                                                                                                  |

|-----------|-------------------|--------------------------------------------------------------------------------------------------------------------|

| ARMv6     | ARM11             | <ul> <li>Improved Multiprocessor<br/>instructions</li> <li>Unaligned and Mixed<br/>endian data handling</li> </ul> |

### ARM processor Features

| Terms | Extention                    |

|-------|------------------------------|

| Х     | Family or series             |

| Y     | Memory Management            |

| Z     | Cache                        |

| Т     | 16bit thumb decoder          |

| D     | Jtag Debugger                |

| Μ     | Fast multiplier              |

| Ι     | Embedded In circuit Emulator |

| Ε     | Enhanced Instruction for DSP |

| J     | Jazelle                      |

| F     | Vector floating point unit   |

| S     | Synthesizable version        |

# **ARM 7family**

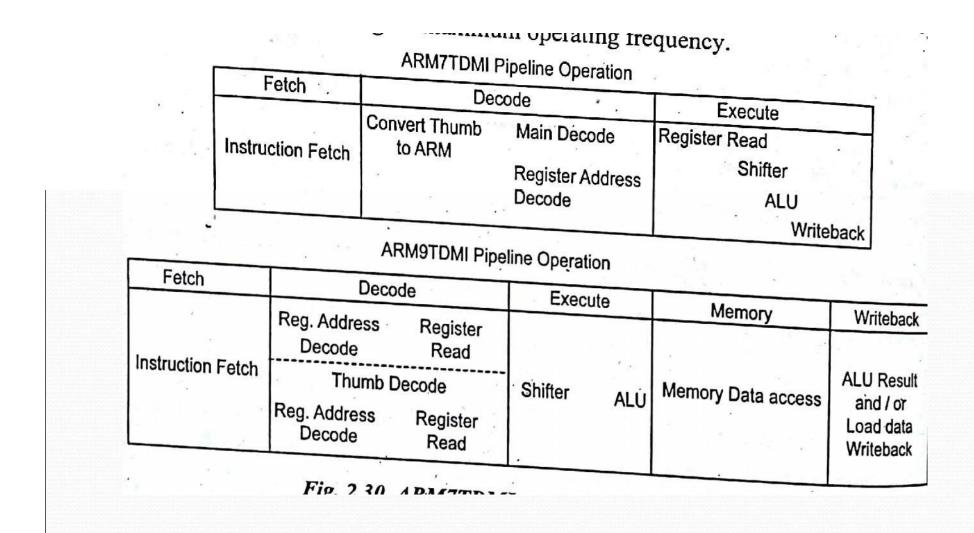

- ARM7 core has a von neumann style architecture

- ARM7 TDMI is first processor introduced in 1995 by ARM

- It provide a very good performance to power ratio

- ARM7TDMI-S has the synthesizable

- ARM720T is the most fexible member of ARM7 family because it include MMU. MMU handle both platforms Linux and windows

- It having unified 8k cache and vector table are relocated depend on the priority

- ARM7EJS processor, also synthesizable. Its having five stage pipeline and execute ARMv5TEJ instruction

- This version only support java acceleration.

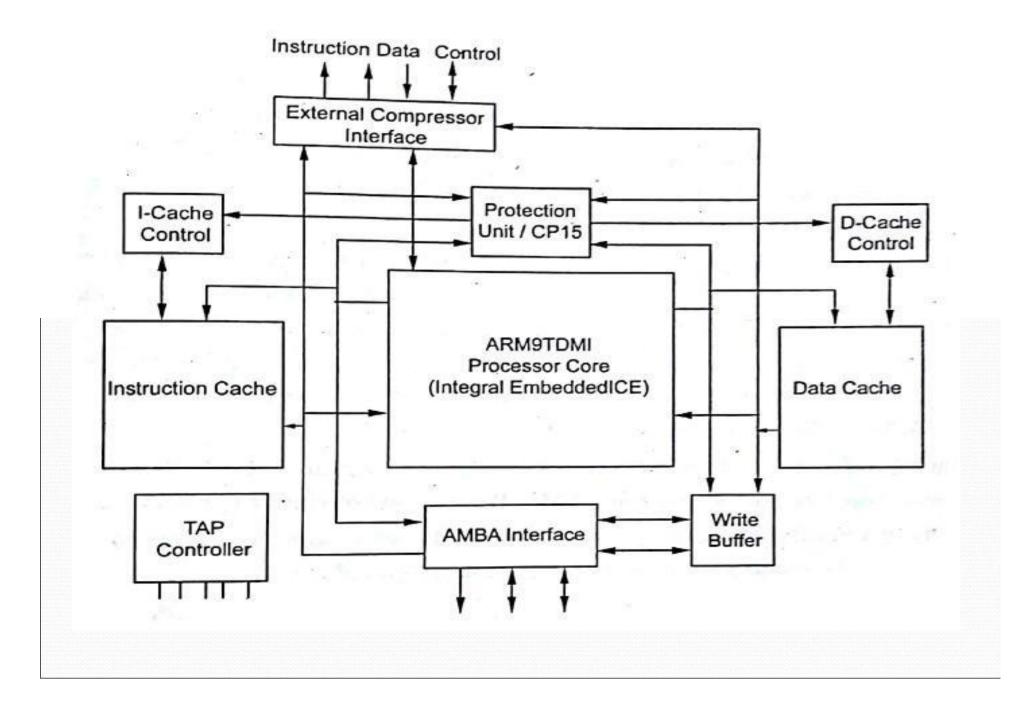

## ARM9 family

- The ARM9 family was announced in 1997

- ARM9 has five stage pipeline and high clock frequencies

- Memory have been redesign Harvard architecture

- ARM9 process includes cache and MMU

- Operating system requiring virtual memory support

- ETM (Embedded Trace Macrocell) which allows a developer to trace instruction and data execution in real time operation. So that debugging is done during the critical time segments.

- ARM946E-S include TCM, cache and MPU. The size of the TCM and cache are configurable

- The processor is designed for the embedded control application that require deterministic real time response

- ARM926EJ-S synthesizable processor core, announced in 2000

- It a java enable device such as 3G phones and personal digital assistant

# RM10 FAMILY

- The ARM10 announced in 1997 was designed for performance

- It extended version of 6 stage pipeline

- Vector floating point unit which adds a seventh stage to the ARM10 pipeline

- VFP combined with IEEE 754.1985 floating point

- ARM1020 E it includes E instruction. it having cache, VFP and MMU

- ARM1026EJ-S is similar to ARM926EJ-S . But ARM10 is flexible when compare to ARM9

# ARM11

- ARM1136J-S, announced in 2003 was designed for high performance and power efficient applications

- ARM1136J-S was the first processor to execute architecture ARMv6 instructions

- It has eight pipeline stages with load and store arithmetic pipeline.

- ARMv6 instruction are single instruction with multiple data extensions for media processing.

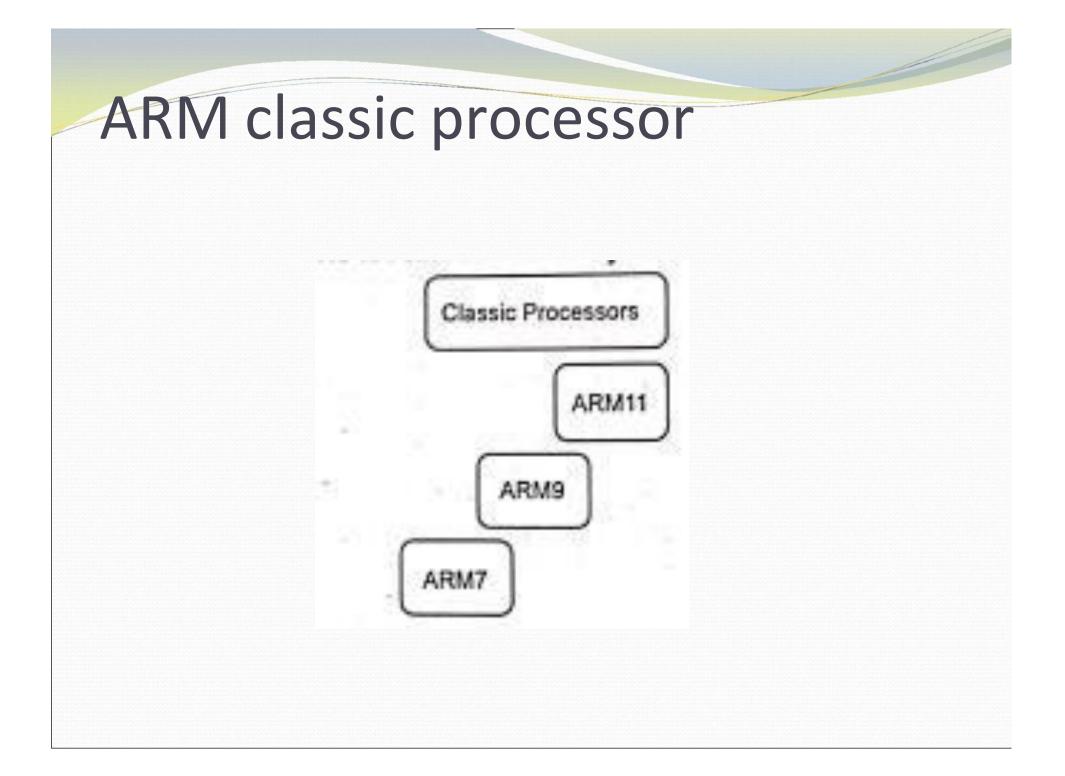

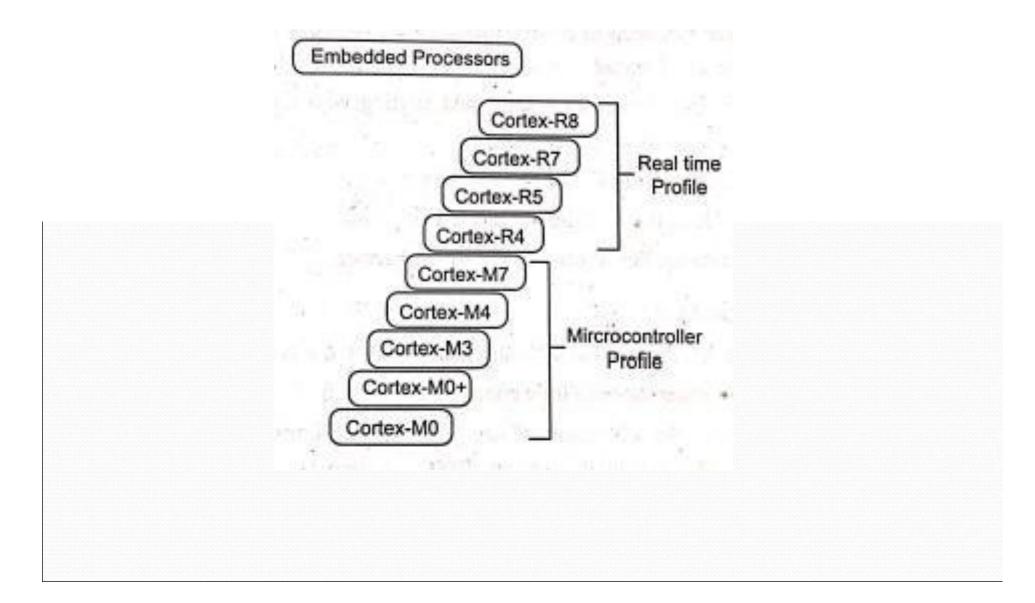

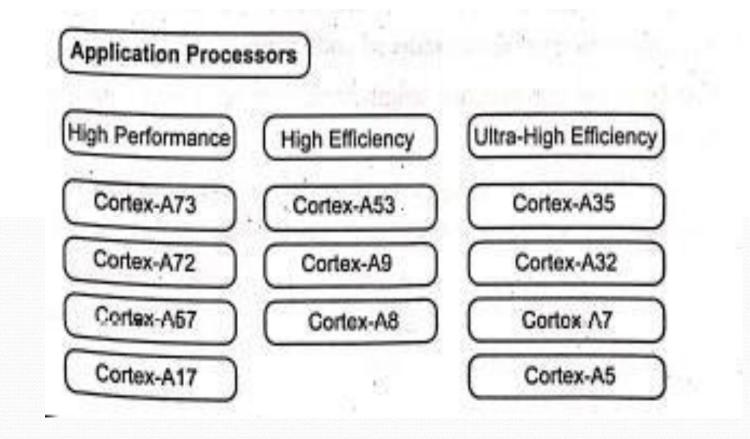

#### • 2.2 ARM PROCESSORS

- ARM Processor can be divided into three types

- ARM classic processor

- ARM Embedded Processor

- ARM Application processor

## **ARM Embedded Processor**

## **ARM Application processor**

# **ARM ARCHITECTURE**

- The architecture has evolved over time, and starting with cortex series of cores, three profiles are,

- Application Profile Cortex- A series

- Real time profile- Cortex- R series

- Microcontroller profile-Cortex –M series

#### **Arm Features**

- A load-store architecture,

- Fixed-length 32-bit instructions

- 3-Address instruction formats.

- It has 32 bit architecture but it supports to 16bit and 8 bit data types also

- A wide choice of development tools and simulation models for leading EDA (Electronic Design Automation) environments and excellent debug support

- ARM uses a Intelligent Memory Manager (IEM). It implements advanced algorithms to optimally balance processor workload and power consumption.IEM work with operating system and mobile OS

- ARM uses AHB (AMBA Advanced High performance Bus) interface. AMBA is open source specification for on chip interconnection

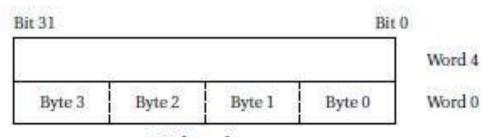

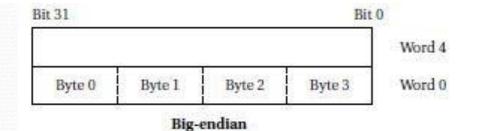

### Byte organizations with an ARM word

Little-endian

# **ARM ARCHITECTURE**

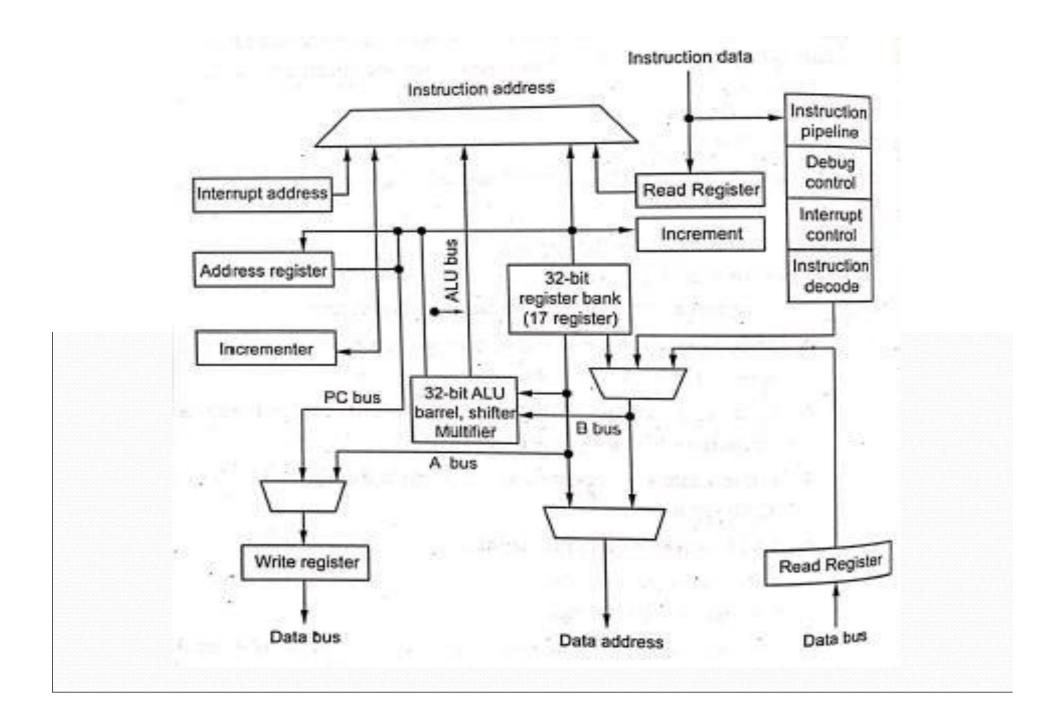

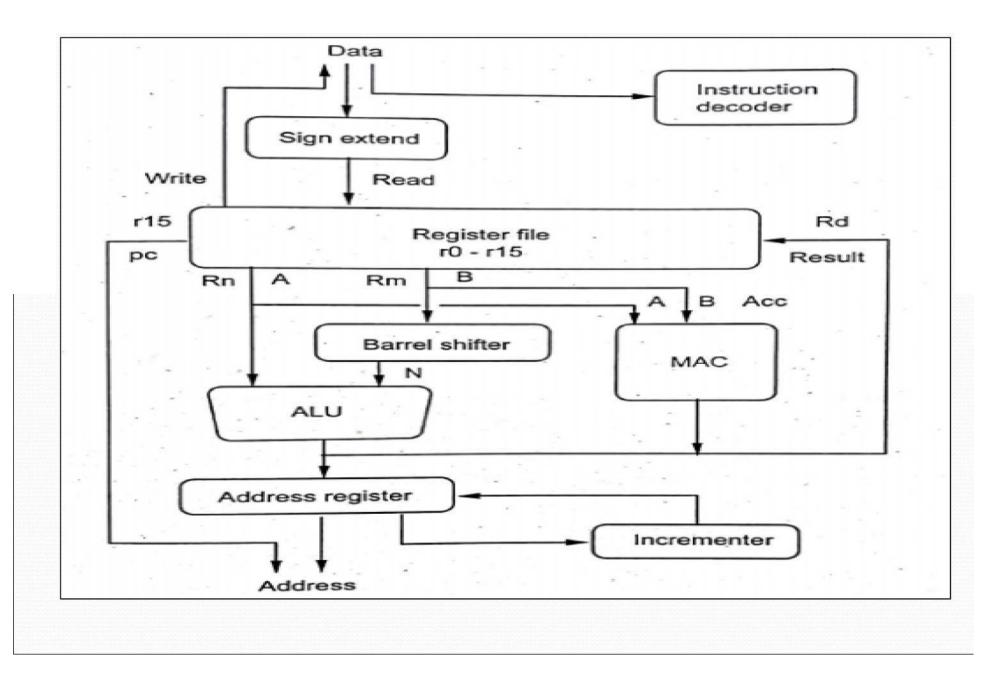

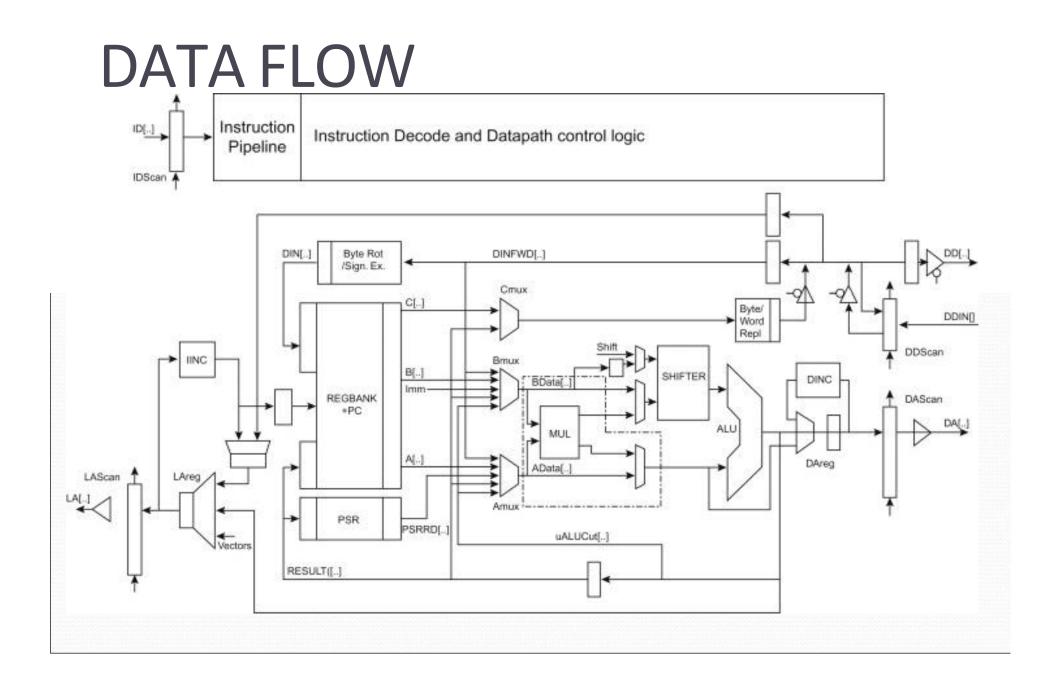

- ARM core is functional units connected by data buses.

- Arrow represents the flow of data.

- Lines represent buses.

- Boxes represent either operation unit or storage area

- Design of ARM is simple and Programmer's design.

- Power Saving design module.

- Flexible design for different application with simple changes

- Instruction Pipeline and Read Data Register are 32 bit

- ARM instructions have two registers:

- Rm, Rn- source register

- Rd-destination register.

- Address bus line A(31:0) and data in lines DATA (31:0) to store the data into the register.

- Address Register holds the address of next instruction / data to be fetched

- Address Incrementer the address register value to appropriate amount to point the next instruction/ data

- It contains 31 Register bank, each register are 32 bit registers and also contains 6 status registers each of 32 bits

### **CPU Modes of ARM:**

- User mode: It is used for programs and applications. It is a only non privileged mode.

- **System Mode:** It is a special version of user mode. It allows the full read write access to the CPSR.

- **Supervisor Mode:** it is privileged mode it enters whenever the processor get reset or SWI instruction is executed. In this mode OS kernel operates in.

- Abort Mode: It occurs when there is a failed attempt to access the memory. This mode is entered when prefetch abort and data abort exception occurs.

- Undefined mode: it is used when the processor encountered an instruction that is undefined or not supported by the implementation. It is a privileged mode.

- **Interrupt Mode :** It is a privileged mode. When the processor accepts the IRQ it occurs.

- Fast Interrupt Mode : It is a privileged mode. When the processor accepts the IRQ it occurs.

- **HYP Mode:** This mode introduced in the ARMV-7A fir cortex- A15 processor to providing hardware virtualization support.

# The Current Program Status Register (CPSR)

- It gives the status of ALU result for every execution

- The CPSR is used in user-level programs to store the condition code bits.

- Example, to record the result of a comparison operation and to control whether or not a conditional branch is taken

|        | 8      | 76 | 5 5 | 4    | 0 |

|--------|--------|----|-----|------|---|

| unused | 10000  | IF | Т   | mode |   |

|        | unused |    |     |      |   |

- N: Negative; the last ALU operation which changed the flags produced a negative result

- **Z: Zero**; the last ALU operation which changed the flags produced a **zero result** (every bit of the 32-bit result was zero).

- C: Carry; the last ALU operation which changed the flags generated a carry-out, either as a result of an arithmetic operation in the ALU or from the shifter.

- V: oVerflow; the last arithmetic ALU operation which changed the flags generated an overflow into the sign bit.

| For arithmetic | ADD | Add                 |

|----------------|-----|---------------------|

|                | ADC | Add with carry      |

|                | SUB | Subtract            |

|                | SBC | Subtract with carry |

|                | RSB | Reverse subtract    |

|                                          | RSC   | Reverse subtract with carry  |

|------------------------------------------|-------|------------------------------|

|                                          | MUL   | Multiply                     |

|                                          | MLA   | Multiply and accumulate      |

|                                          | AND   | Bit wise and                 |

|                                          | ORR   | Bit wise or                  |

| For logical                              | EOR   | Bit wise exclusive or        |

|                                          | BIC   | Bit clear                    |

|                                          | LSL   | Logical shift left           |

|                                          | LSR   | Logical shift right          |

| E                                        | ASL   | Arithmetic shift left        |

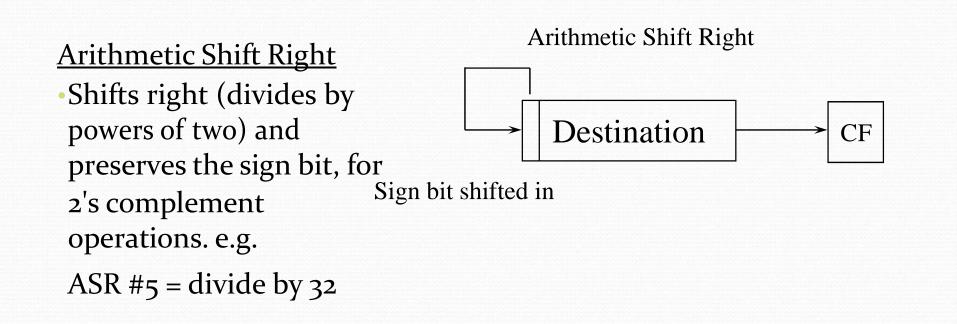

| For shift/rotate                         | ASR   | Arithmetic shift right       |

|                                          | ROR   | Rotate right                 |

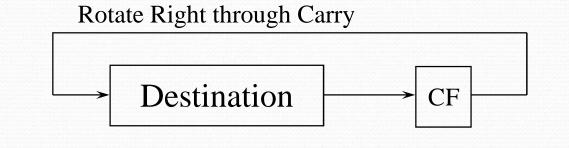

|                                          | RRX   | Rotate right extended with C |

|                                          | CMP   | Compare                      |

| ARM Comparison                           | CMN   | Negated compare              |

| Instructions                             | TST   | Bit wise test                |

| 5 A. | TEQ   | Bit wise negated test        |

| ARM Move                                 | MOV   | Move                         |

| Instructions                             | MVN   | Move negated                 |

| ARM Load                                 | LDR   | Load                         |

| Store                                    | STR   | Store                        |

| Instructions and                         | LDRSH | Load Half Word               |

| Pseudo     | STRH  | Store Half Word         |

|------------|-------|-------------------------|

| Operations | LDRSH | Load Half Word Signed   |

|            | LDRB  | Load byte               |

|            | STRB  | Store byte              |

|            | ADR   | Set register to address |

- Example Program:

- int a,b,c, X;

- X= a+b-c;

ADR r4, a : get address for a LDR r0, [r4] : get value of a ADR r4, b : get address for b, reusing r4LDR r1, [r4] : load value of bADD r3, r0, r1 : set intermediate result for X to a + b: get address for C ADR, r4, c : get value of C LDR ,r2, [r4] : complete computation of X SUB r3, r3, r2 : get address for X ADR r4, X: store X at proper location STR r3, [r4]

#### **ARM INSTRUCTION SET**

# Types of instruction set

- Data Processing Instructions

- Branch Instructions

- Load Store Instructions

- Software interrupt Instructions

- Program Status Register Instructions

### **DATA PROCESSING INSTRUCTIONS:**

- Move instruction

- Arithmetic instruction

- Logical instruction

- Comparison instruction

- Multiply instruction

# Move instruction

- MOV operand2

- MVN NOT operand 2

- MOVS Update In Status Reg

- Syntax:

- <Operation>{<cond>}{S} Rd, Operand2

- Examples:

- MOV ro, r1

- MOVS r2, #10

# The Barrel Shifter

- The ARM doesn't have actual shift instructions.

- Instead it has a barrel shifter which provides a mechanism to carry out shifts as part of other instructions.

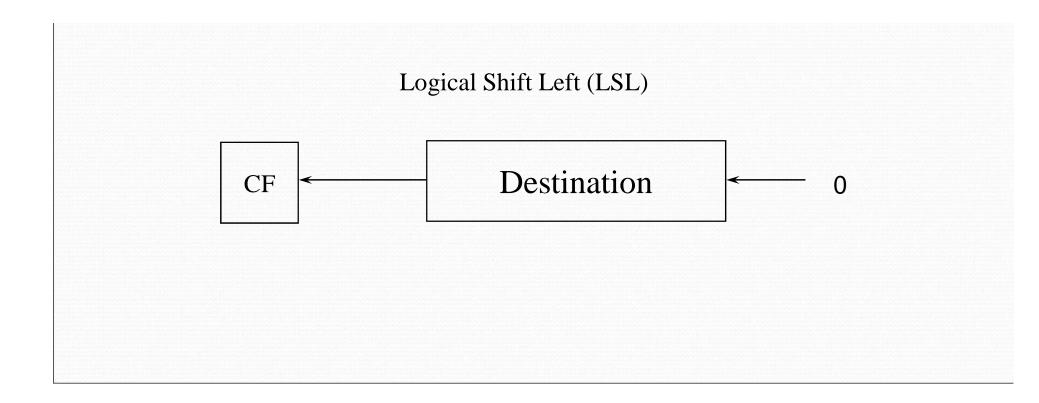

### Barrel Shifter - Left Shift

• Shifts left by the specified amount (multiplies by powers of two)

e.g.

LSL #5 = multiply by 32

## Barrel Shifter - Left Shift

# Barrel Shifter - Right Shifts

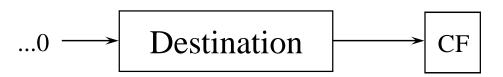

#### Logical Shift Right

Shifts right by the specified amount (divides by powers of two) e.g.

LSR #5 = divide by 32

Logical Shift Right

# **Barrel Shifter - Rotations**

### Rotate Right (ROR)