# DEPARTMENT OFELECTRONICSAND COMMUNICATION ENGINEERING

(ACADEMIC YEAR: 2019-2020)

EC8095-VLSI DESIGN (Regulation 2017)

Semester-VI

NAME-REG NO-

# UNIT I

# INTRODUCTION TO MOS TRANSISTOR

# **MOS Transistor**

The metal-oxide-semiconductor field-effect transistor (MOSFET or MOS, for short) is the basic building block of contemporary digital design. Its major asset from a digital perspective is that the device performs very well as a switch, and introduces little parasitic effects. Other important advantages are its integration density combined with a relatively "simple" manufacturing process, which make it possible to produce large and complex circuits in an economical way.

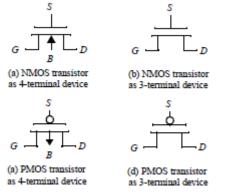

The MOSFET is a four terminal device. The voltage applied to the *gate* terminal determines if and how much current flows between the *source* and the *drain* ports. The *body* represents the fourth terminal of the transistor. Its function is secondary as it only serves to modulate the device characteristics and parameters.

At the most superficial level, the transistor can be considered to be a switch. When a voltage is applied to the gate that is larger than a given value called the *threshold voltage VT*, a conducting channel is formed between drain and source. In the presence of a voltage difference between the latter two, current flows between them. The conductivity of the channel is modulated by the gate voltage— the larger the voltage difference between gate and source, the smaller the resistance of the conducting channel and the larger the current.

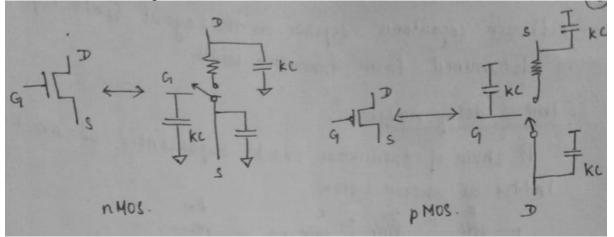

When the gate voltage is lower than the threshold, no such channel exists, and the switch is considered open. Two types of MOSFET devices can be identified. The NMOS transistor consists of n+ drain and source regions, embedded in ap-type substrate. The current is carried by electrons moving through an n-type channel between source and drain. This is in contrast with the pn-junction diode, where current is carried by both holes and electrons. MOS devices can also be made by using an n-type substrate and p+ drain and source regions. In

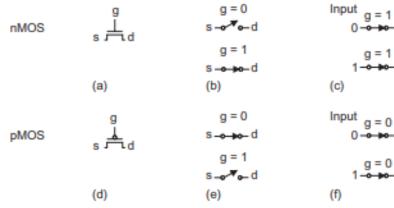

such a transistor, current is carried by holes moving through a *p*-type channel. The device is called a *p*-channel MOS, or PMOS transistor. In a complementary MOS technology (CMOS), both devices are present. The Circuit symbols for the various MOS transistors are shown in Figure. As mentioned earlier, the transistor is a four-port device with gate, source, drain, and body terminals (Figures a and c). Since the body is generally connected to a dc supply that is identical for all devices of the same type (GND for NMOS, *Vdd* for PMOS), it is most often not shown on the schematics (Figures b and d).**If the fourth terminal is not shown, it is assumed that the body is connected to the appropriate supply.**

#### i. <u>The MOS Transistor under Static Conditions</u>

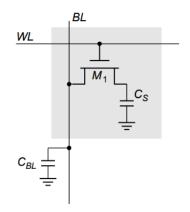

# The Threshold Voltage

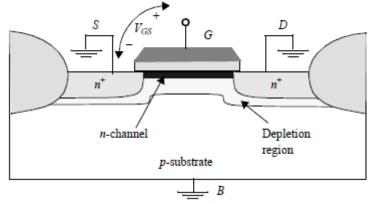

Consider first the case where VGS = 0 and drain, source, and bulk are connected to ground. The drain and source are connected by back-to-back *pn*-junctions (substrate-source and substrate-drain). Under the mentioned conditions, both junctions have a 0 V bias and can be considered off, which results in an extremely high resistance between drain and source. Assume now that a positive voltage is applied to the gate (with respect to the source), as shown in Figure. The gate and substrate form the plates of a capacitor with the gate oxide as the dielectric. The positive gate voltage causes positive charge to accumulate on the gate electrode and negative charge on the substrate side. The latter manifests itself initially by repelling mobile holes. Hence, a depletion region is formed below the gate. This depletion region is similar to the one occurring in a pn-junction diode.

As the gate voltage increases, the potential at the silicon surface at some point reaches a critical value, where the semiconductor surface inverts to *n*-type material. This point marks the onset of a phenomenon known as *strong inversion* and occurs at a voltage equal to twice the *Fermi Potential*

$$\phi_F = -\phi_T \ln(\frac{N_A}{n_i})$$

Further increases in the gate voltage produce no further changes in the depletion layer width, but result in additional electrons in the thin inversion layer directly under the oxide. These are drawn into the inversion layer from the heavily doped n + source region.

Hence, a continuous n-type channel is formed between the source and drain regions, the conductivity of which is modulated by the gate-source voltage. In the presence of an inversion layer, the charge stored in the depletion region is fixed and equals

$$Q_{B0} = \sqrt{2qN_A\varepsilon_{si}} - 2\phi_F$$

This picture changes somewhat in case a substrate bias voltage VSB is applied (VSB is normally positive for *n*-channel devices). This causes the surface potential required for strong inversion to increase and to become |-2fF + VSB|. The charge stored in the depletion region now is expressed by Eq.

$$Q_B = \sqrt{2qN_A \varepsilon_{si}(-2\phi_F + V_{SB})}$$

The value of *VGS* where strong inversion occurs is called the *threshold voltage VT.VT* is a function of several components, most of which are material constants such as the difference in work-function between gate and substrate material, the oxide thickness, the Fermi voltage, the charge of impurities trapped at the surface between channel and gate oxide, and the dosage of ions implanted for threshold adjustment. From the above arguments, it has become clear that the source-bulk voltage *VSB* has an impact on the threshold.

as well. Rather than relying on a complex (and hardly accurate) analytical expression for the threshold, we rely on an empirical parameter called *VT*0, which is the threshold voltage for VSB = 0, and is mostly a function of the manufacturing process. The threshold voltage under different body-biasing conditions can then be determined in the following manner,

$$V_T = V_{T0} + \gamma(\sqrt{-2\phi_F + V_{SB}} - \sqrt{-2\phi_F})$$

The parameter g (gamma) is called the *body-effect coefficient*, and expresses the impact of changes in *VSB*. Observe that the threshold voltage has a **positive** value for a typical **NMOS** device, while it is **negative** for a normal **PMOS** transistor.

#### **Resistive Operation**

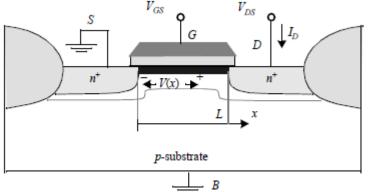

Assume now that VGS > VT and that a small voltage, VDS, is applied between drain and source. The voltage difference causes a current *ID* to flow from drain to source Figure. Using a simple analysis, a first-order expression of the current as a function of *V GS* and *VDS* can be obtained.

At a point x along the channel, the voltage is V(x), and the gate-to-channel voltage at that point equals VGS - V(x). Under the assumption that this voltage exceeds the threshold voltage all along the channel, the induced channel charge per unit area at point x can be computed.

$$Q_i(x) = -C_{ox}[V_{GS} - V(x) - V]_{\mathbf{f}}$$

Cox stands for the capacitance per unit area presented by the gate oxide, and equals

$$C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}}$$

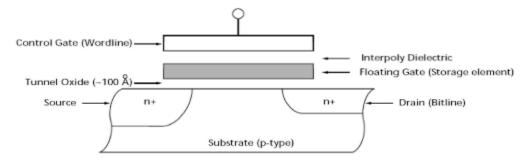

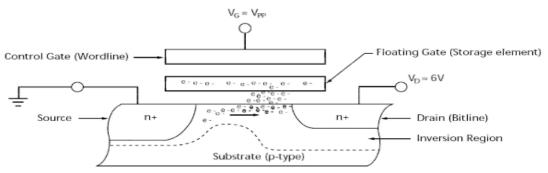

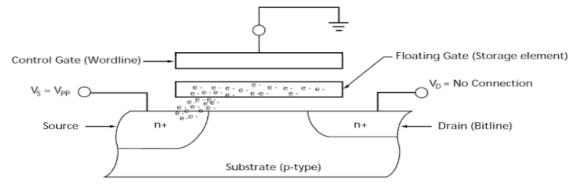

with eox = 3.97 ' eo = 3.5 ' 10-11 F/m the oxide permittivity, and *tox* is the thickness of the oxide. The latter which is 10 nm (= 100 Å) or smaller for contemporary processes. For an oxide thickness of 5 nm, this translates into an oxide capacitance of 7 fFm/m2.

The current is given as the product of the drift velocity of the carriers un and the available charge. Due to charge conservation, it is a constant over the length of the channel. *W* is the width of the channel in a direction perpendicular to the current flow.

# $I_D = -v_n(x)Q_i(x)W$

The electron velocity is related to the electric field through a parameter called the*m obility* mn (expressed in m2/V×s). The mobility is a complex function of crystal structure, and local electrical field. In general, an empirical value is used.

$$\upsilon_n = -\mu_n \xi(x) = \mu_n \frac{dV}{dx}$$

Combining the equations we have

$$I_D dx = \mu_n C_{ox} W (V_{GS} - V - V_T) dV$$

Integrating the equation over the length of the channel*L* yields the voltage-current relation of the transistor.

$$I_{D} = k_{n} \frac{W}{L} \left[ (V_{GS} - V_{T}) V_{DS} - \frac{V_{DS}^{2}}{2} \right] = k_{n} \left[ (V_{GS} - V_{T}) V_{DS} - \frac{V_{DS}^{2}}{2} \right]$$

Kn' is called the *process transconductance parameter* and equals

MSAJCE-ECE

$$k'_n = \mu_n C_{ox} = \frac{\mu_n \varepsilon_{ox}}{t_{ox}}$$

The product of the process transconductance and the (W/L) ratio of an (NMOS) transistor is called the *gain factor kn* of the device. For smaller values of *VDS*, the quadratic factor in Eq. for I<sub>D</sub> can be ignored, and we observe a linear dependence between *VDS* and *ID*. The operation region where Eq. for I<sub>D</sub> holds is hence called the *resistive* or *linear* region. One of its main properties is that it displays a continuous conductive channel between source and drain regions.

#### **The Saturation Region**

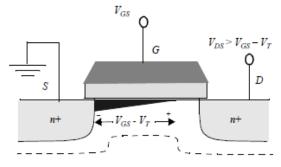

As the value of the drain-source voltage is further increased, the assumption that the channel voltage is larger than the threshold all along the channel ceases to hold. This happens when VGS - V(x) < VT. At that point, the induced charge is zero, and the conducting channel disappears or is *pinched off*.

This is illustrated in Figure, which shows (in an exaggerated fashion) how the channel thickness gradually is reduced from source to drain until pinch-off occurs. No channel exists in the vicinity of the drain region. Obviously, for this phenomenon to occur, it is essential that the pinch-off condition be met at the drain region, or

#### $V_{GS} - V_{DS} \le V_T$

Under those circumstances, the transistor is in the *saturation* region, and Eq. for I<sub>D</sub> no longer holds. The voltage difference over the induced channel (from the pinch-off point to the source) remains fixed at  $V_{GS}$  - V<sub>T</sub>, and consequently, the current remains constant (or saturates). Replacing  $V_{DS}$  by  $V_{GS}$  - V<sub>T</sub> in Eq. for I<sub>D</sub> yields the drain current for the saturation mode. It is worth observing that, to a first agree, the current is no longer a function of  $V_{DS}$ . Notice also the *squared dependency* of the drain current with respect to the control voltage  $V_{GS}$ .

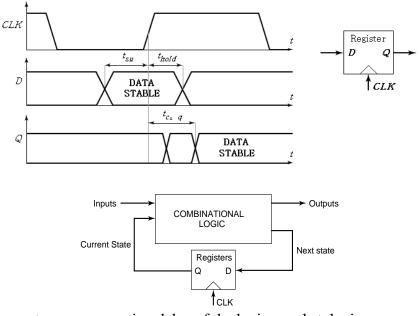

#### ii. **Dynamic Behavior**

The dynamic response of a MOSFET transistor is a sole function of the time it takes to (dis)charge the parasitic capacitances that are intrinsic to the device, and the extra capacitance introduced by the interconnecting lines . A profound understanding of the nature and the behavior of these intrinsic capacitances is essential for the designer of high-quality digital integrated circuits. They originate from three sources: the basic MOS structure, the channel charge, and the depletion regions of the reverse-biased *pn*-junctions of drain and source. Aside from the MOS structure capacitances, all capacitors are nonlinear and vary with the applied voltage, which makes their analysis hard

#### **MOS Structure Capacitances**

The gate of the MOS transistor is isolated from the conducting channel by the gate oxide that has a capacitance per unit area equal to Cox = eox / tox. We learned earlier that from a *IV* perspective it is useful to have *Cox* as large as possible, or to keep the oxide thickness very thin. The total value of this capacitance is called the *gate capacitance Cg* and can be decomposed into two elements, each with a different behaviour. Obviously, one part of *C g* contributes to the channel charge, and is discussed in a subsequent section. Another part is solely due to the topological structure of the transistor. This component is the subject of the remainder of this section.

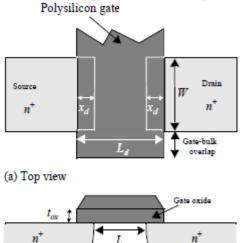

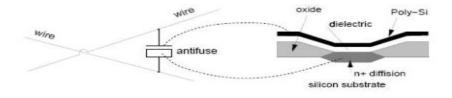

Consider the transistor structure of Figure. Ideally, the source and drain diffusion should end right at the edge of the gate oxide. In reality, both source and drain tend to extend somewhat below the oxide by an amount xd, called the *lateral diffusion*. Hence, the effective channel of the transistor L becomes shorter than the drawn length Ld (or the length the transistor was originally designed for) by a factor of DL = 2xd. It also gives rise to a parasitic capacitance between gate and source (drain) that is called the *overlap capacitance*. This capacitance is strictly linear and has a fixed value

(b) Cross section

$C_{GSO} = C_{GDO} = C_{ox} x_d W = C_o W$

Since xd is a technology-determined parameter, it is customary to combine it with the oxide capacitance to yield the overlap capacitance per unit transistor width *C o* (more specifically, *Cgso* and *Cgdo*).

#### **Channel Capacitance**

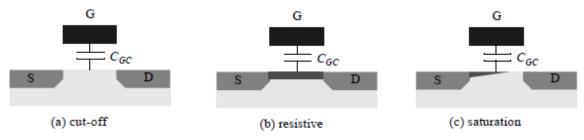

Perhaps the most significant MOS parasitic circuit element, the gate-to-channel capacitance *CGC* varies in both magnitude and in its division into three components *C GCS*, *CGCD*, and *CGCB* (being the gate-to-source, gate-to-drain, and gate-to-body capacitances, respectively),

depending upon the operation region and terminal voltages. This varying distribution is best explained with the simple diagrams of Figure. When the transistor is in cut-off (a), no channel exists, and the total capacitance *CGC* appears between gate and body. In the resistive region (b), an inversion layer is formed, which acts as a conductor between source and drain. Consequently, CGCB = 0 as the body electrode is shielded from the gate by the channel. Symmetry dictates that the capacitance distributes evenly between source and drain. Finally, in the saturation mode (c), the channel is pinched off. The capacitance between gate and drain is approximately zero, and so is the gate-body capacitance. All the capacitance hence is between gate and source.

The gate-capacitance components are nonlinear and varying with the operating voltages. To make a first-order analysis possible, we will use a simplified model with a constant capacitance value in each region of operation

| Operation Region | C <sub>GCB</sub>     | C <sub>GCS</sub> | C <sub>GCD</sub> | C <sub>GC</sub>  | C <sub>G</sub>                |

|------------------|----------------------|------------------|------------------|------------------|-------------------------------|

| Cutoff           | $C_{\alpha\alpha}WL$ | 0                | 0                | $C_{\alpha x}WL$ | $C_{ax}WL+2C_{o}W$            |

| Resistive        | 0                    | $C_{ox}WL/2$     | $C_{ox}WL/2$     | $C_{ox}WL$       | $C_{ox}WL+2C_{o}W$            |

| Saturation       | 0                    | $(2/3)C_{ox}WL$  | 0                | $(2/3)C_{ax}WL$  | $(2/3)C_{\alpha x}WL+2C_{o}W$ |

in the remainder of the text. The assumed values are summarized in Table.

#### **Junction Capacitances**

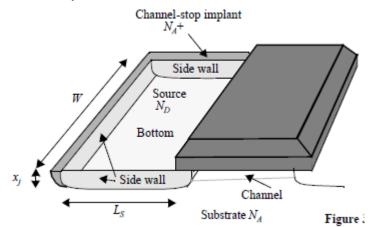

A final capacitive component is contributed by the reverse-biased source-body and drain body *pn*-junctions. The depletion-region capacitance is nonlinear and decreases when the reverse bias is raised as discussed earlier. To understand the components of the junction capacitance (often called the *diffusion capacitance*), we must look at the source (drain) region and its surroundings. The detailed picture, shown in Figure, shows that the junction consists of two components:

The *bottom-plate* junction, which is formed by the source region (with doping *ND*) and the substrate with doping *NA*. The total depletion region capacitance for this component equals Cbottom = CjWLS, with Cj the junction capacitance per unit area as given by Eq. . As the bottom-plate junction is typically of the abrupt type, the

grading coefficient m approaches 0.5.

• The *side-wall* junction, formed by the source region with doping *N D* and the *p*+ channelstop implant with doping level *NA* +. The doping level of the stopper is usually larger than that of the substrate, resulting in a larger capacitance per unit area. The side-wall junction is typically graded, and its grading coefficient varies from 0.33 to 0.5. Its capacitance value equals Csw = C'jswxj ( $W + 2 \land Ls$ ). Notice that no side-wall capacitance is counted for the fourth side of the source region, as this represents the conductive channel.

Since xj, the junction depth, is a technology parameter, it is normally combined with C'jsw into a capacitance per unit perimeter Cjsw = C'jswxj. An expression for the total junction capacitance can then be derived,

$$\begin{split} C_{diff} &= C_{bottom} + C_{sw} = C_j \times AREA + C_{jsw} \times PERIMETER \\ &= C_j L_S W + C_{jsw} (2L_S + W) \end{split}$$

#### **Capacitive Device Model**

G

All the above contributions can be combined in a single capacitive model for the MOS transistor, which is shown Figure. Its components are readily identified on the basis of the preceding discussions.

$$C_{GS} = C_{GCD} + C_{GDO}; C_{GB} = C_{GCB}$$

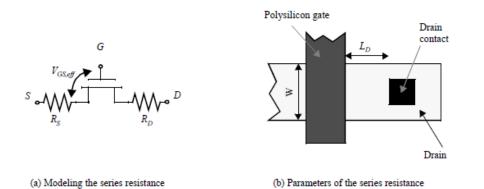

#### **Source-Drain Resistance**

The performance of a CMOS circuit may further be affected by another set of parasitic elements, being the resistances in series with the drain and source regions, as shown in Figure . This effect become more pronounced when transistors are scaled down, as this leads to shallower junctions and smaller contact openings become smaller. The resistance of the drain (source) region can be expressed as

$$R_{S,D} = \frac{L_{S,D}}{W} R_{\Box} + R_C$$

with *RC* the contact resistance, *W* the width of the transistor, and *LS*,*D* the length of the source or drain region . Ro is the *sheet resistance* per square of the drain source diffusion, and ranges from 20 to 100 W/o. Observe that the resistance of a square of material is constant, independent of its size.

#### Non ideal I-V Effects

# **Channel-Length Modulation**

The equation seems to suggest that the transistor in the saturation mode acts as a perfect current source — or that the current between drain and source terminal is a constant, independent of the applied voltage over the terminals. This not entirely correct. The effective length of the conductive channel is actually modulated by the applied  $V_{DS}$ : increasing  $V_{DS}$  causes the depletion region at the drain junction to grow, reducing the length of the effective channel. As can be observed from Eq. For I<sub>D</sub> in the saturation region, the current increases when the length factor *L* is decreased. A more accurate description of the current of the MOS transistor is therefore given in Eq.

$$I_D = I_D'(1 + \lambda V_{DS})$$

with  $I_D$ ' the current expressions derived earlier, and 1 an empirical parameter, called the *channel-length modulation*. Analytical expressions for 1 have proven to be complex and inaccurate. I varies roughly with the inverse of the channel length. In shorter transistors, the drain-junction depletion region presents a larger fraction of the channel, and the channel-modulation effect is more pronounced. It is therefore advisable to resort to long-channel transistors if a high-impedance current source is needed.

#### **Velocity Saturation**

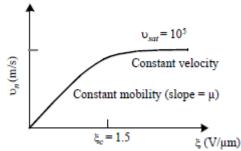

The behaviour of transistors with very short channel lengths (called *short-channel devices*) deviates considerably from the resistive and saturated models, presented in the previous paragraphs. The main culprit for this deficiency is the *velocity saturation* effect. Eq. For velocity states that the velocity of the carriers is proportional to the electrical field, independent of the value of that field. In other words, the carrier mobility is a constant. However, at high field strengths, the carriers fail to follow this linear model. In fact, when the electrical field along the channel reaches a critical value xc, the velocity of the carriers tends to saturate due to scattering effects (collisions suffered by the carriers). This is illustrated in Figure

For *p*-type silicon, the critical field at which electron saturation occurs is around 1.5  $\Box$   $\Box$  106 V/m (or 1.5 V/ $\Box$ m), and the saturation velocity  $\Box$  *sat* approximately equals 105 m/s. The velocity as a function of the electrical field, plotted in Figure , can be roughly approximated by the following expression:

$$\upsilon = \frac{\mu_n \zeta}{1 + \xi/\xi_c} \text{ for } \xi \leq \xi_c$$

$$= \upsilon_{sat} \quad \text{for } \xi \geq \xi_c$$

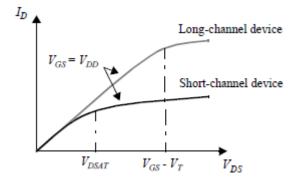

• For a short-channel device and for large enough values of VGT,  $\Box(VGT)$  is substantially smaller than 1, hence VDSAT < VGT. The device enters saturation before  $V_{DS}$  reaches  $V_{GS} - V_T$ . Short-channel devices therefore experience an extended saturation region, and tend to operate more often in saturation conditions than their long-channel counterparts, as is illustrated in Figure.

8

• The saturation current *IDSAT* displays a *linear dependence* with respect to the gate source voltage *VGS*, which is in contrast with the squared dependence in the long channel device. This reduces the amount of current a transistor can deliver for a given control voltage. On the other hand, reducing the operating voltage does not have such a significant effect in submicron devices as it would have in a long-channel transistor.

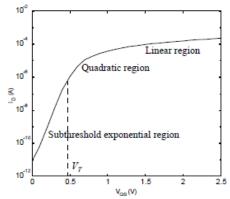

#### **Subthreshold Conduction**

A closer inspection of the *ID-VGS* curves of Figure 3.20 reveals that the current does not drop abruptly to 0 at VGS = VT. It becomes apparent that the MOS transistor is already partially conducting for voltages below the threshold voltage. This effect is called *su bthreshold* or *weak-inversion* conduction. The onset of strong inversion means that ample carriers are available for conduction, but by no means implies that no current at all can flow for gate-source voltages below VT, although the current levels are small under those conditions. The transition from the on- to the off-condition is thus not abrupt, but gradual.

To study this effect in somewhat more detail, we redraw the *ID* versus *VGS* curve of Figure on a logarithmic scale as shown in Figure. This confirms that the current does not drop to zero immediately for VGS < VT, but actually decays in an exponential fashion, similar to the operation of a bipolar transistor. 2 In the absence of a conducting channel, the n+ (source) - p (bulk) - n+ (drain) terminals actually form a parasitic bipolar transistor. The current in this region can be approximated by the expression.

$$I_D = I_S e^{\frac{V_{GS}}{kT/q}} \left(1 - e^{-\frac{V_{DS}}{kT/q}}\right)$$

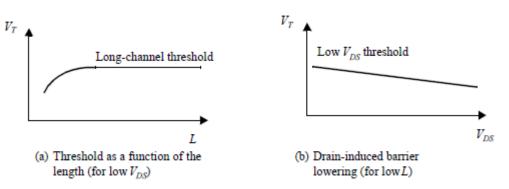

#### **Threshold Variations**

the threshold voltage is only a function of the manufacturing technology and the applied body bias *VSB*. The threshold can therefore be considered as a constant over all NMOS (PMOS) transistors in a design. As the device dimensions are reduced, this model becomes inaccurate,

and the threshold potential becomes a function of L, W, and VDS. Two-dimensional secondorder effects that were ignorable for long-channel devices suddenly become significant. In the traditional derivation of the VTO, for instance, it is assumed that the channel depletion region is solely due to the applied gate voltage and that all depletion charge beneath the gate originates from the MOS field effects. This ignores the depletion regions of the source and reverse-biased drain junction, which become relatively more important with shrinking channel lengths. Since a part of the region below the gate is already depleted (by the source and drain fields), a smaller threshold voltage suffices to cause strong inversion. In other words, VT0 decreases with L for short-channel devices (Figure a . A similar effect can be obtained by raising the drain-source (bulk) voltage, as this increases the width of the drainjunction depletion region. Consequently, the threshold decreases with increasing VDS. This effect, called the drain-induced barrier lowering, or DIBL, causes the threshold potential to be a function of the operating voltages (Figure b). For high enough values of the drain voltage, the source and drain regions can even be shorted together, and normal transistor operation ceases to exist. The sharp increase in current that results from this effect, which is called *punch-through*, may cause permanent damage to the device and should be avoided.

Punch-through hence sets an upper bound on the drain-source voltage of the transistor.

#### **Hot-Carrier Effects**

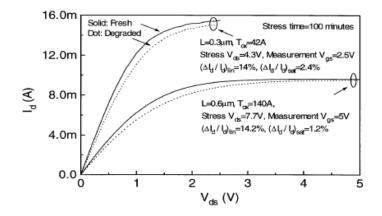

- Besides varying over a design, threshold voltages in short-channel devices also have the tendency to *drift over time*. This is the result of the *hot-carrier* effect [Hu92].

- Over the last decades, device dimensions have been scaled down continuously, while the power supply and the operating voltages were kept constant.

- The resulting increase in the electrical field strength causes an increasing velocity of the electrons, which can leave the silicon and tunnel into the gate oxide upon reaching a high-enough energy level. Electrons trapped in the oxide change the threshold voltage, typically increasing the thresholds of NMOS devices, while decreasing the *VT* of PMOS transistors. For an electron to become hot, an electrical field of at least 104 V/cm is necessary. This condition is easily met in devices with channel lengths around or below 1 mm.

- The hot-electron phenomenon can lead to a long-term reliability problem, where a circuit might degrade or fail after being in use for a while. This is illustrated in Figure , which shows the degradation in the *I*-*V* characteristics of an NMOS transistor after it has been subjected to extensive operation. State-of the-art MOSFET technologies therefore use specially-engineered drain and source regions to ensure that the peaks in the electrical fields are bounded, hence preventing carriers to

reach the critical values necessary to become hot. The reduced supply voltage that is typical for deep sub-micron technologies can in part be attributed to the necessity to keep hotcarrier effects under control.

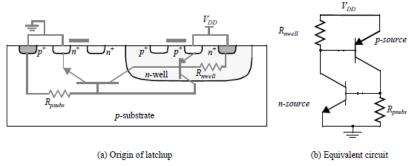

#### **CMOS Latchup**

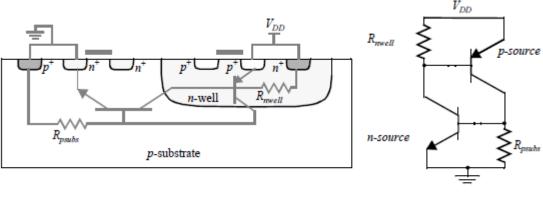

The MOS technology contains a number of intrinsic bipolar transistors. These are especially troublesome in CMOS processes, where the combination of wells and substrates results in the formation of parasitic *n-p-n-p* structures. Triggering these thyristor-like devices leads to a shorting of the *VDD* and *VSS* lines, usually resulting in a destruction of the chip, or at best a system failure that can only be resolved by power-down.

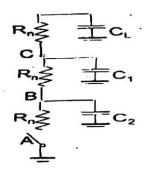

Consider the *n*-well structure of Figure a. The *n-p-n-p* structure is formed by the source of the NMOS, the *p*-substrate, the *n*-well and the source of the PMOS. A circuit equivalent is shown in Figure b. When one of the two bipolar transistors gets forward biased (e.g., due to current flowing through the well, or substrate), it feeds the base of the other transistor. This positive feedback increases the current until the circuit fails or burns out.

(a) Origin of latchup

(b) Equivalent circuit

To avoid latchup, the resistances *Rnwell* and *Rpsubs* should be minimized. This can be achieved by providing numerous well and substrate contacts, placed close to the source connections of the NMOS/PMOS devices. Devices carrying a lot of current (such as transistors in the I/O drivers) should be surrounded by *guard rings*. These circular well/substrate contacts, positioned around the transistor, reduce the resistance even further and reduce the gain of the parasitic bipolars.

#### **CMOS logic**

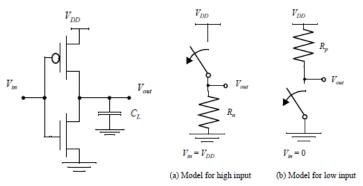

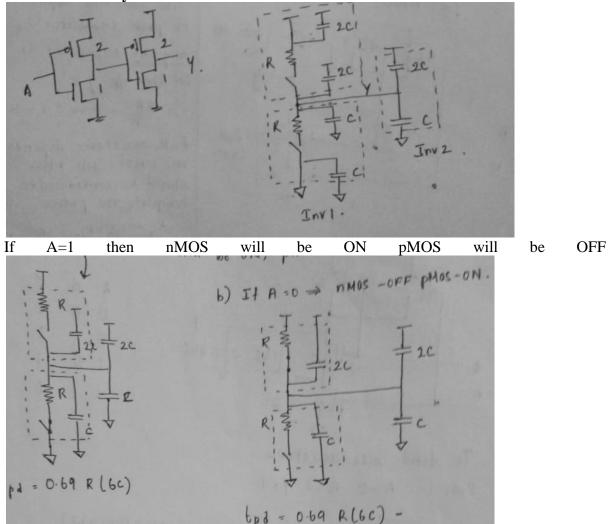

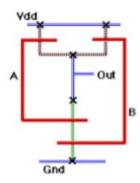

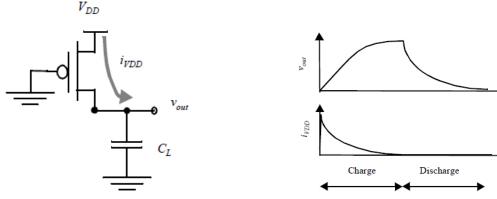

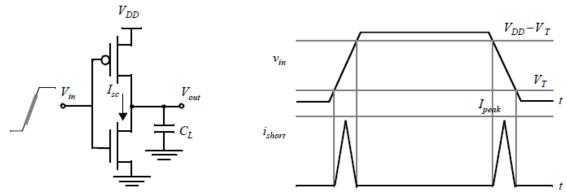

#### The Static CMOS Inverter

Figure 5.1 shows the circuit diagram of a static CMOS inverter. the transistor is nothing more than a switch with an infinite off resistance (for |VGS| < |VT|), and a finite on-resistance (for |VGS| > |VT|). This leads to the following interpretation of the inverter. When *Vin* is high and equal to *VDD*, the NMOS transistor is on, while the PMOS is off. This yields the equivalent circuit of Figure a. A direct path exists between *Vout* and the ground node, resulting in a steady-state value of 0 V. On the other hand, when the input voltage is low (0 V), NMOS and

PMOS transistors are off and on, respectively. The equivalent circuit of Figure b shows that a path exists between *VDD* and *Vout*, yielding a high output voltage. The gate clearly functions as an inverter.

A number of other important properties of static CMOS can be derived from this switch level view:

• The high and low output levels equal *VDD* and *GND*, respectively; in other words, the voltage swing is equal to the supply voltage. This results in high noise margins.

• The logic levels are not dependent upon the relative device sizes, so that the transistors can be minimum size. Gates with this property are called *ratioless*. This is in contrast with *ratioed logic*, where logic levels are determined by the relative dimensions of the composing transistors.

• In steady state, there always exists a path with finite resistance between the output and either *VDD* or *GND*. A well-designed CMOS inverter, therefore, has low *output impedance*, which makes it less sensitive to noise and disturbances. Typical values of the output resistance are in  $k \square \square$  range.

• The *input resistance* of the CMOS inverter is extremely high, as the gate of an MOS transistor is a virtually perfect insulator and draws no dc input current. Since the input node of the inverter only connects to transistor gates, the steady-state input current is nearly zero. A single inverter can theoretically drive an infinite number of

gates (or have an infinite fan-out) and still be functionally operational; however, increasing the fan-out also increases the propagation delay, as will become clear below. So, although fan-out does not have any effect on the steady-state behavior, it degrades the transient response.

No direct path exists between the supply and ground rails under steady-state operating conditions (this is, when the input and outputs remain constant). The absence of current flow (ignoring leakage currents) means that the gate does not consume any static power.

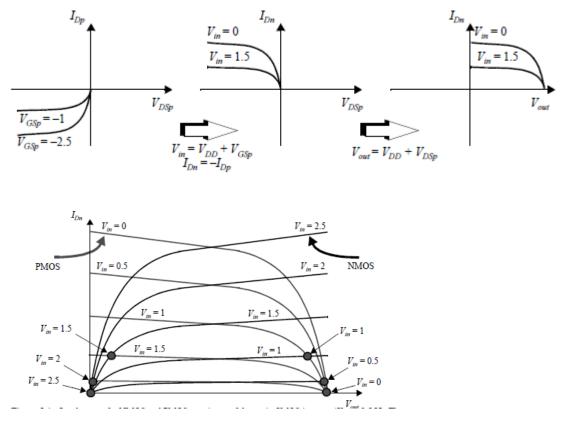

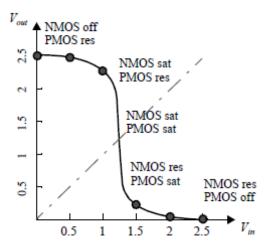

# **DC Transfer characteristics**

The nature and the form of the voltage-transfer characteristic (VTC) can be graphically deduced by superimposing the current characteristics of the NMOS and the PMOS devices. Such a graphical construction is traditionally called *a load-line plot*. It requires that the *I-V* curves of the NMOS and PMOS devices are transformed onto a common coordinate set. We have selected the input voltage *Vin*, the output voltage *Vout* and the NMOS drain current *IDN* as the variables of choice. The PMOS *I-V* relations can be translated into this variable space by the following relations (the subscripts *n* and *p* denote the NMOS and PMOS devices, respectively):

$$I_{DSp} = -I_{DSn}$$

$$V_{GSn} = V_{in} ; V_{GSp} = V_{in} - V_{DD}$$

$$V_{DSn} = V_{out} ; V_{DSp} = V_{out} - V_{DD}$$

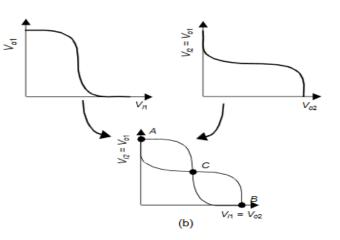

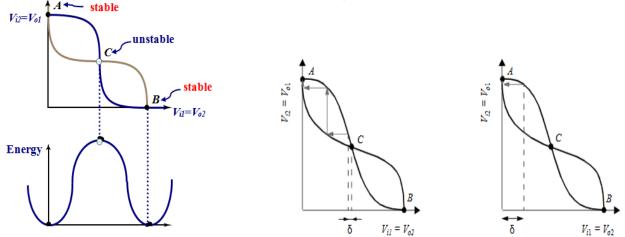

The load-line curves of the PMOS device are obtained by a mirroring around the *x*-axis and a horizontal shift over *VDD*. This procedure is outlined in Figure , where the subsequent steps to adjust the original PMOS *I-V* curves to the common coordinate set *Vin*, *Vout* and *IDn* are illustrated.

The resulting load lines are plotted in above Figure. For a dc operating points to be valid, the currents through the NMOS and PMOS devices must be equal. Graphically, this means that the dc points must be located at the intersection of corresponding load lines. A number of those points (for Vin = 0, 0.5, 1, 1.5, 2, and 2.5 V) are marked on the graph. As can be observed, all operating points are located either at the high or low output levels.

The VTC of the inverter hence exhibits a very narrow transition zone. This results from the high gain during the switching transient, when both NMOS and PMOS are simultaneously on, and in saturation. In that operation region, a small change in the input voltage results in a large output variation. All these observations translate into the VTC of below Figure.

MSAJCE-ECE

# **VLSI DESIGN**

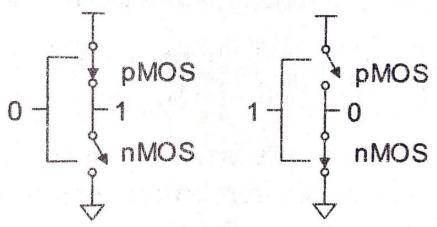

#### Pass Transistor Logic

.

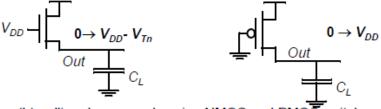

nMOS pass strong 0 – But degraded or weak 1 ;• pMOS pass strong 1 – But degraded or • weak 0. Thus nMOS are best for pull-down network

- Primary inputs drive both gate and source/drain terminals

- NMOS switch closes when the gate input is high

- Remember NMOS transistors pass a strong 0 but a weak 1

- Primary inputs drive both gate and source/drain terminals

- PMOS switch closes when the gate input is low

Remember - PMOS transistors pass a strong 1 but a weak 0

(a) Basic concept

Output

degraded 1

Output

0 ------ degraded 0

strong 1

g = 1

g = 0

g = 0

-0-

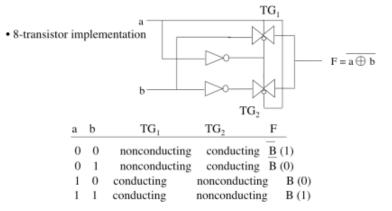

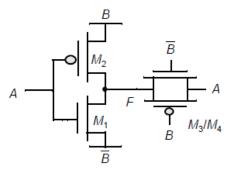

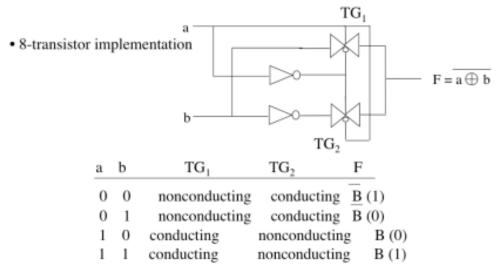

# **Transmission Gates**

- · Pass transistors produce degraded outputs

- Transmission gates pass both 0 and 1 well

V<sub>DD</sub>

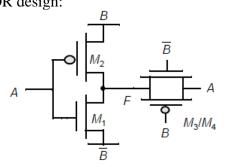

Multiplexer design:

XOR design:

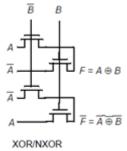

# XNOR design:

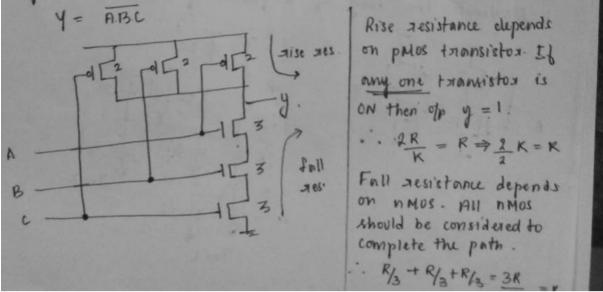

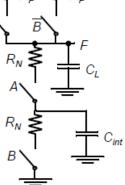

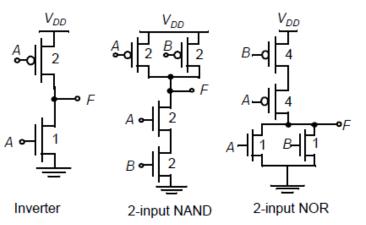

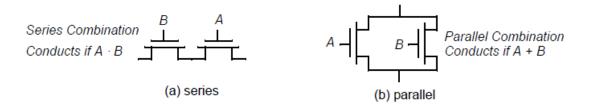

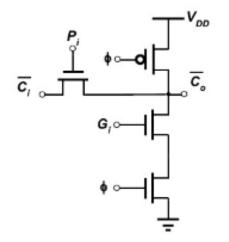

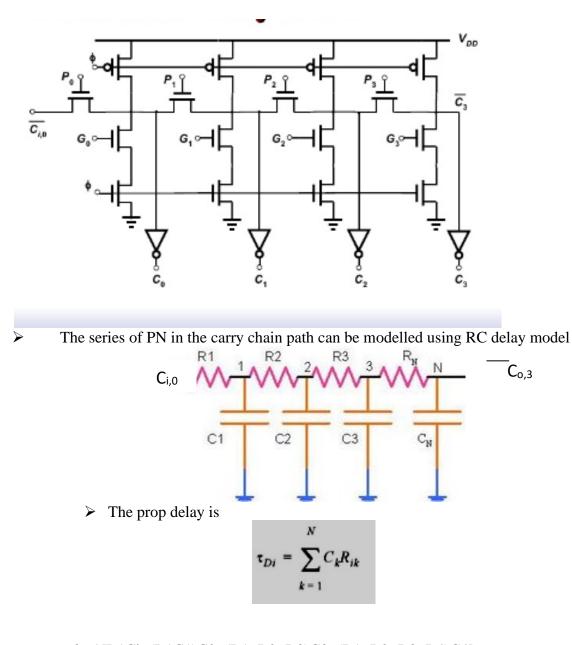

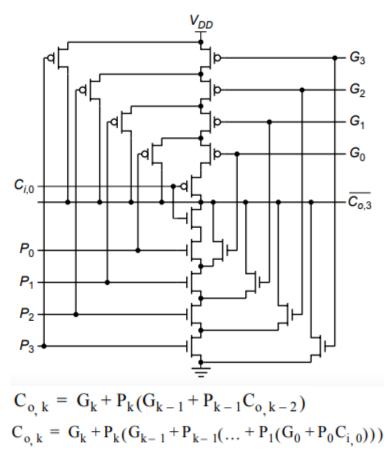

#### RC DELAY MODEL

It treats transistors as switches in series with resistors.

A unit nMOS transistors has an effective resistance of R and pMOS transistor has an effective resistance 2R.

The size of the unit transistor refers to a transistor with maximum length and minimum contacted diffusion width.

AnMOS transistor of K time unit width has resistance R/K. Similarly a pMOS transistor K times unit width has resistance 2R/K[because of its lower mobility i.e is mobility  $\mu$  increase and resistance R decreases].

Each transistor has a gate and diffusion capacitance cgs and Cdb and Csb. So a transistor of K times unit width has capacitance C.

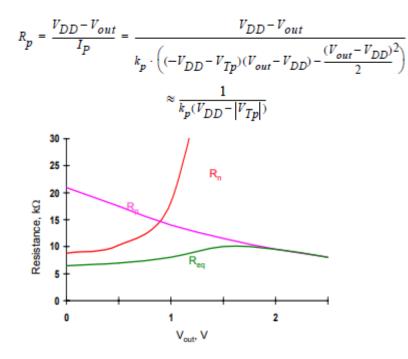

#### **Effective resistance and capacitance**

Parallel and series transistor combine like conventional resistors.

When multiple transistors are in series then the equivalent resistance is the sum of each individual resistance. When multiple transistors are in parallel the the equivalent re; sistance is lower if they are all ON.

Eg: Sketch 3input NAND gate with transistors width chosen to achieve effective rise and fall resistance equal to that of a unit inverter.

Diffusion capacitance depends on the layout. Gate capacitance is determined from the transistor width.

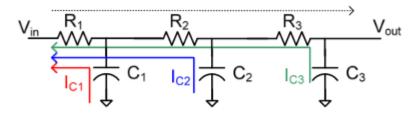

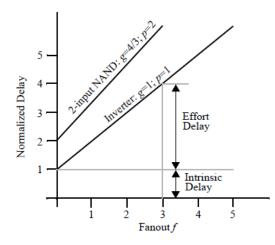

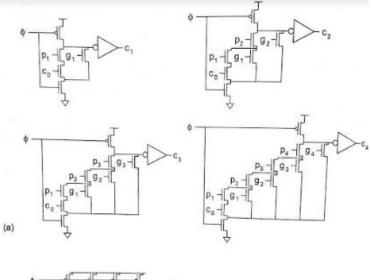

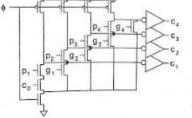

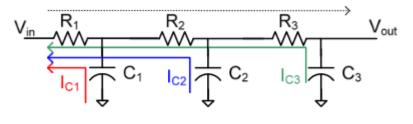

#### **ELMORE DELAY MODEL**

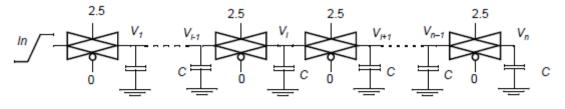

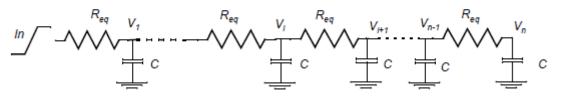

A chain of transistors can be represented as an RC ladder as shown below

$$\tau_{Elmors} = R_1 C_1 + (R_1 + R_2) C_2 + (R_1 + R_2 + R_3) C_3$$

The Elmore delay model estimates the delay of an RC ladder. It is the sum of the resistance Rn-I (between that node and a supply) multiplied by the capacitance on the node.

# Problem

1. Estimate the delay of a fanout of 1 inverter

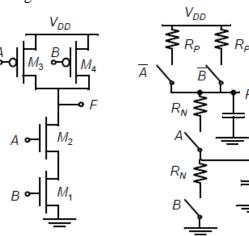

2.Sketch a 2 input NAND gate with transistor width chosen to achieve effective rise and fall resistance equal to the unit inverter. Compute the rising and falling propagation delay (in terms of R and C) of the NAND gate driving h identical NAND gates using the Elmore delay model. If C=2fF/ $\mu$ m and R=2.5 k $\Omega$ / $\mu$ m in a 180nm process what is the delay of a fanout of 3 NAND gate.

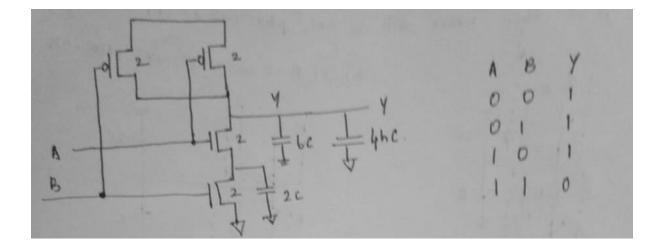

(a) Two-input NAND

(b) RC equivalent model

nise resistance To find Cose i A = 0 B=1 4=1 t pdn = 0.69 R (6c+4hc) = 0.69 R c [6+4h] e = 28F/um R= 2.5 kvz/um 6hC h= 3. Epda = 0.69 x 2.52103 x 222 90ps x.69 - 62.1ps 11 A = 0 B t pan = 0.69 x R [6c+ 4hc] 0.69 RC[3+26] 6C 4hc

3.Consider the NAND gate of Figure . Assume NMOS and PMOS devices of 0.5mm/0.25mm and 0.75mm/0.25mm, respectively. This sizing should result in approximately equal worst-case rise and fall times (since the effective resistance of the pull-down is designed to be equal to the pull-up resistance).

| Input Data<br>Pattern | Delay<br>(psec) |

|-----------------------|-----------------|

| A = B= 0→1            | 69              |

| A = 1, B= 0→1         | 62              |

| A= 0→1, B = 1         | 50              |

| A=B=1→0               | 35              |

| A=1, B = 1→0          | 76              |

| A= 1→0, B = 1         | 57              |

(a) Two-input NAND

(b) RC equivalent model

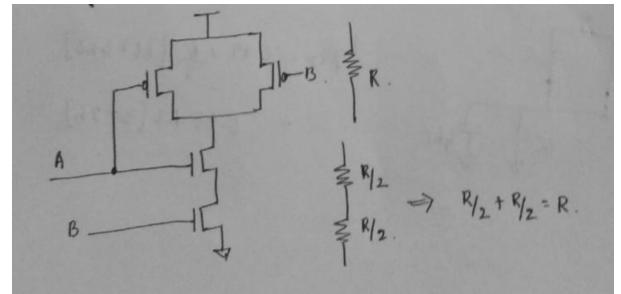

**Two Input NOR**

Four input NAND gate and its RC model.

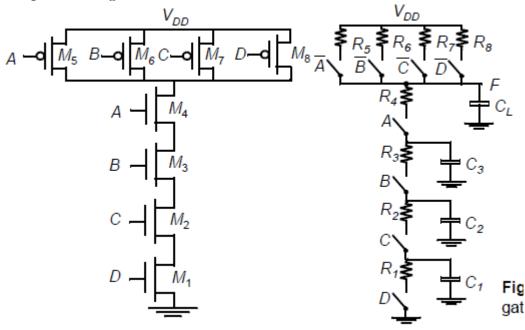

# LINEAR DELAY MODEL

In general the propagation delay of a gate can be written as d= Parasitic delay P, effort delay f.

Parasitic delay P = Inherent delay to the gate when no load is attached.

Effort delay or a stage effort depends on the complexity and fanout of the gate.

f= Logical effort g=fanout

f=g.h and d=p+;

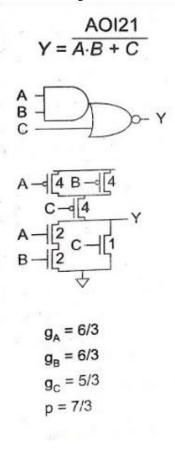

# i. Logical effort g

It is defined as the ratio between the input capacitances of the gate and the input capacitance of the inverter that can deliver the same amount.

g= Cin of gate/ Cin of inverter

Both delivering same current.

It represents the complexity of the gate.

Eg: Determine the logical effort of inverter NAND and NOR gate.

For inverter Cin=3C g=3C/3C=1

MSAJCE-ECE

For 2 input NAND Cin=4C g=4C/3C =4/3

For 2 input NOR Cin=5C g=5C/3C =5/3

# ii. Estimates of intrinsic delay factors

| Gate type         | р          |

|-------------------|------------|

| Inverter          | 1          |

| n-input NAND      | п          |

| n-input NOR       | п          |

| n-way multiplexer | 2 <i>n</i> |

| XOR, NXOR         | $n2^{n-1}$ |

# iii. Logical effort of common gate

|             | Number of Inputs |     |     |          |

|-------------|------------------|-----|-----|----------|

| Gate Type   | 1                | 2   | 3   | n        |

| Inverter    | 1                |     |     |          |

| NAND        |                  | 4/3 | 5/3 | (n+2)/3  |

| NOR         |                  | 5/3 | 7/3 | (2n+1)/3 |

| Multiplexer |                  | 2   | 2   | 2        |

| XOR         |                  | 4   | 12  |          |

# iv. Electrical effort or fanout h

It is defined as the ratio between the output capacitance to the input capacitance.

h= Cout/Cin where Cout is the capacitance of external load and Cin is the input capacitance of the gate.

$D{=}\,f{+}p$

=gh+p

G= Cout/Cin +p

Let Cin/g= drive= 1/R, then d=Cout/drive +p

# v. Parasitic delay

It is defined as the delay of the gate when it drives zero load. It can be estimated with RC delay models.

Mainly depends on diffusion capacitances.

The inverter has 3 units of diffusion capacitance on the outpu. So the parasitic delay is 3RC.

The normalised parasitic delay Pinv=1. It is defined as the ratio of diffusion capacitance to the gate capacitance.

The normalised parasitic delay of NAND and NOR gate is 6RC/3RC = 2 Pinv or simple 2. Tpd= $[n^2/2+5/2n]RC$ . It is the Elmore delay model.

The two main problems of complementary CMOS gates are,

- 1. Complexity of the gate (i.e fan in) increases and the overall capacitance also incrases which will affect the speed of the gate.

- 2. The number of transistors required to implement "N" inputs is 2N. This increases the implementation area.

- 3. The following techniques are used to reduce the dealay of larger fan in are

Transistor sizing.

Input reoedering.

Progressive tr sizing.

Logic reconstructing.

| Term              | Stage expression             | Path expression                           |

|-------------------|------------------------------|-------------------------------------------|

| Logical effort    | g (seeTable 1)               | $G = \prod g_i$                           |

| Electrical effort | $h = \frac{C_{out}}{C_{in}}$ | $H = rac{C_{out (path)}}{C_{in (path)}}$ |

| Branching effort  | n/a                          | $B = \prod b_i$                           |

| Effort            | f = gh                       | F = GBH                                   |

| Effort delay      | f                            | $D_F = \sum f_i$                          |

| Number of stages  | 1                            | Ν                                         |

| Parasitic delay   | ho (seeTable 2)              | $P = \sum p_i$                            |

| Delay             | d = f + p                    | $D = D_F + P$                             |

# vi. Delay as a function of fanout for an inverter and a 2-input NAND.

22

#### TRANSISTOR SIZING

The delay of larger fan in can be reduced by increaring the transistor sizes. This will lower the resistance of thr device which is in series and finally reduces delay.

However increasing the transistor sizes leads to larger parasitic capacitance which is not only affects the delay of the gate also increasing larger load to the next stage gate.

# • Progressive transistor sizing

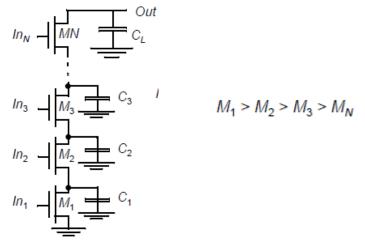

An alternate approach to uniform sizing is the progressive transistor sizing. Consider the following example in which the transistor are connected in series.

The delay is given by= 0.69[R1C1+(R1+R2)C2+(R1+R2+R3)C3+(R1+R2+R3+R4)C4]This equation indicates that the resistance R1 appears N times and R2 appears (N-1) times etc. So we have to made the transistor M size larger (morder to reduce R1) than M2 transistors M1>M2>M3>M4 is the progress sizing.

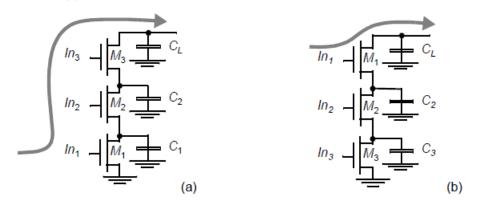

#### • Input reordering

The gate works fast when inner input signals arrives than the outer input signal.

The input which is closer to the power supply rail (Vdd or Gnd) is called outer input. The input which is closer to the output is called inner input.

In1= outer input and In3= Inner input.

Consider that In1 is the critical signal. Critical signal is the signal that arrives last of all inputs.

Consider Case(1): In3=1; In2=1

M1=OFF and M2=ON. So capacitance C1and C2 cannot discharge.

Therefore In1 arrives late. The delay of is

t=0.69[R1C1+(R1+R2)C2+(R1+R2+R3)C3+(R1+R2+R3+R4)C4]Now order the input signal In1 In this case(2):

VLSI DESIGN

In3=1: In2=1.

Therefore M2=ON and M3=ON and M1=OFF till In1=1. Here C2 and C1 can discharge. However Cl will discharge only after In1=1. The delay is t=(R1+R2+R3)C1\*0.69

Logical reconstructing

The delay of large number of inputs can be reduced by restricting the gate into 2/3 input gates which will speed up the gate.

# **OPTIMIZING PERFORMANCE IN COMBINATIONAL NETWORKS**

The method of logical effort provides a simple method to choose the fastest ciru=cuit topology and number of stages for a given function.

It allows the designer to quickly estimate the minimum possible delay for the given topology. Logical effort is based on linear delay model. The logical effort method is used to

- 1. Estimate the delay of individual logic.

- 2. To predict the delay of multistage logic network.

- 2. To predict the deray of multistage logic network.

3. Choose the best number of stages for a multistage network.

# I. DELAY IN LOGIC GATE

The delay of a logic gate can be expressed by means of linear delay model.

Total delay d = gh + p

Propagation delay tpd= dT where g is the logical effort h is the electrical effort p is the parasitic delay V is the time constant for a particular process.

Eg: Estimate the delay of fanout of 4 inverter i.e inverter driving 4 identical copies. Assume the inverter is constructed in a 180nm process with T=15ps.

Logical effort g=1 Electrical effort h=12C/3C=4 Parasitic delay of an inverter p=1 The total delay d=gh+p =1\*4+1=5tpd=5\*15ps=75ps.

# **II. DELAY IN MULTISTAGE LOGIC NETWORK**

Logical effort can be used to predict the delay of multistage network.

Logical effort is independent of size while electrical effort depends on size.

The path effort F is the product of the logical electrical and branching efforts of the path. F=G.B.H;

# Path logical effort G

It is defined as the product of the logical effort of each stage along the path.

G=pi gi

# Path electrical effort H

It is defined as the ratio of the output capacitance to the input capacitance. In the path electrical effort is defined as the product of stage electrical effort.

#### H= Cout(path)/Cin(path)

# **Branching effort**

It is defined as the ratio of the total capacitance seen by a stage to the capacitance on the path. b=(Con(path)+Coff(path))/Con(path)

B=15+15/15=2

# Path branching effort

It is the product of branching effort between stages

B= pi bi

If a path has a N stages and each path has the same effort is given by

f^=gihi=F^1/N

Thus the minimum possible delay of an N stage path with the path effort and parasitic delay p is

D=NF^1/N+P

$=Df+P=\sum di$

WherDf is th path b effort delay.

To achieve the least delay, the capacitance transformation formula used to find the best input capacitance of a gate for a given ouput capacitance.  $Cin=(Couti.gi)/f^{\wedge}$

MSAJCE-ECE

#### Problems

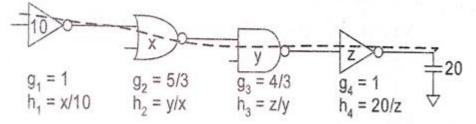

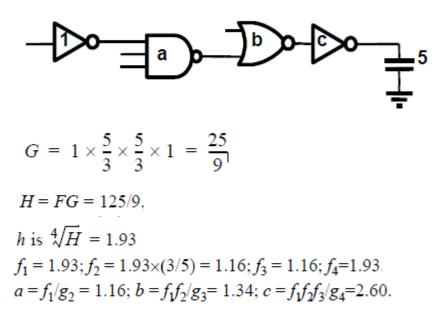

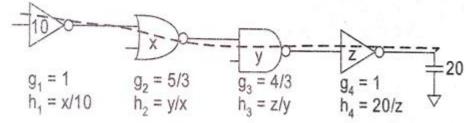

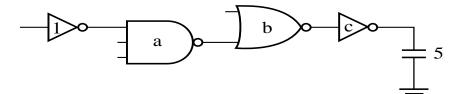

Consider the logic network of Figure, which may represent the critical path of a more complex logic block. The output of the network is loaded with a capacitance which is 5 times larger than the input capacitance of the first gate, which is a minimum-sized inverter. find the path logical effort

Estimate the minimum delay of the path for the following diagram and choose transistor size to achieve the delay

The path logical effort G=g1g2g3g4=pi gi =1.5/3.4/3.1=20/9 Path electrical effort H=20/10=2 Path branching effort B=1 The path effort F=GBH =20/9\*1\*2=40/9 Then F^i/N= F^1/4=1.45 Path parasitic delay P=1+2+2+1=6 Minimum path delay  $D=NF^{(1/N)}+P$ =4\*1.451+6=11.8 tpd=D T=11.8 T z=20\*1/1.451 Cin4= Z=13.78 Cin3=y=Cin4g3/f^=12.66 Cin3=x=Cin3 g2/f^=14.54 Cin1=Cin2 g1/f^=10.02

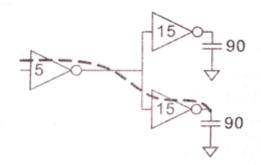

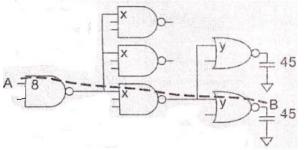

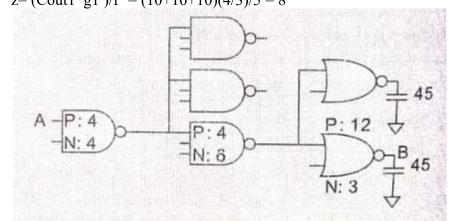

2. Estimate the minimum delay of the path from A to B for a given diagram and choose transistor sizes to achieve this delay. The initial NAND2 gate may present a load of 8 $\lambda$ transistor width on the input and output load is equivalent to 45  $\lambda$  of transistor width.

SOLUTION:

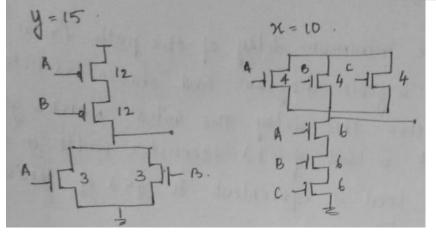

$G = \pi gi = g1.g2.g3 = (4/3)*(5/3)*(5/3)=100/27$  B = (3x/x)\*(2y/y)=6 H = Cout/Cin = 45/8 F = GBH = (100/27)\*6\*(45/8) = 125  $F^{(1/N)} = f^{2} = 125^{(1/3)} = 5$   $D = Nf^{2} + P = (3*5)+7 = 22$  tpd = DT = 22T  $y = (Cout I * gi) / f^{2} = Cin3 = (Cout^{*} g3)/f^{2} = 45(5/3)/5$  y = 15 x = Cin2 = (15+5)(5/3)/5 = 10 $z = (Cout1*g1)/f^{2} = (10+10+10)(4/3)/5 = 8$

#### **III. CHOOSING THE BEST NUMBER OF GATES**

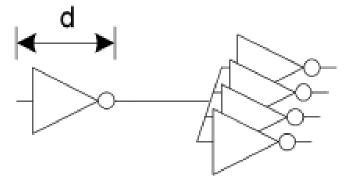

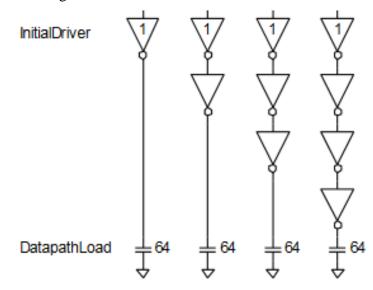

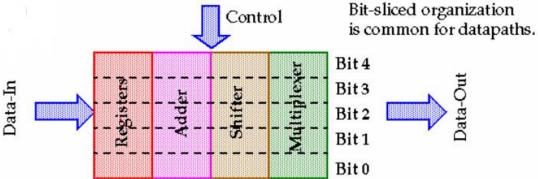

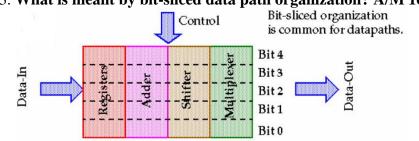

A control unit generates a signal from a unit sized invertor. The signal must drive unit sized loads in each bit slice of a 64 bit datapath. The designer can add inv to buffer the signal to drive the large load. What is the best no of inv to add and what delay can be achieved?

| N=No   | 1  | 2          | 3              | 4                                 |

|--------|----|------------|----------------|-----------------------------------|

| of     |    |            |                |                                   |

| stages |    |            |                |                                   |

| F=gh   | 64 | 8          | 4              | 28                                |

| D=p+f  | 65 | 1+8+1+8=18 | 4+1+4+1+4+1=15 | 2.8+1+8/2.8+1+23/8+1+64/23+1=15.3 |

|        |    |            | Fastest        |                                   |

#### **Technology Scaling**

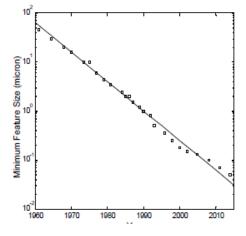

Over the last decades, we have observed a spectacular increase in integration density and computational complexity of digital integrated circuits. Underlying this revolution are the advances in device manufacturing technology that allow for a steady reduction of the minimum feature size such as the minimum transistor channel length realizable on a chip. To illustrate this point, we have plotted inF igure the evolution of the (average) minimum device dimensions starting from the 1960s and projecting into the 21st century. We observe a reduction rate of approximately 13% per year, halving every 5 years. Another interesting observation is that no real sign of a slowdown is in sight, and that the breathtaking pace will continue in the foreseeable future.

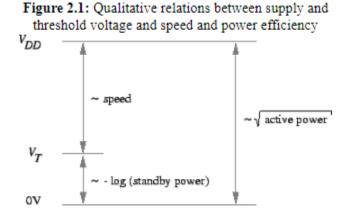

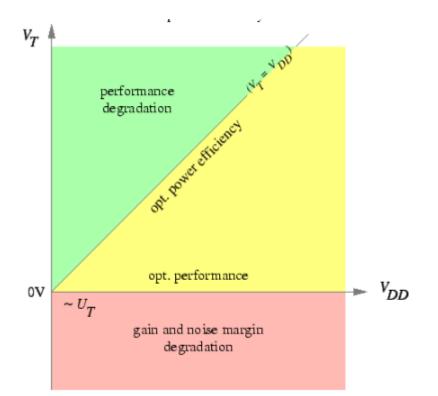

This continued reduction in feature size influences the operating characteristics and properties of the MOS transistor, and indirectly the critical digital design metrics such as switching frequency and power dissipation. A first-order projection of this behaviour is called a scaling analysis. In addition to the minimum device dimension, we have to consider the supply voltage as a second independent variable in such a study. Different scaling scenarios result based on how these two independent variables are varied with respect to each other.

Three different models are studied in Table. To make the results tractable, it is assumed that all device dimensions scale by the same factor S (with S > 1 for a reduction in size). This includes the width and length of the transistor, the oxide thickness, and the junction depths. Similarly, we assume that all voltages, including the supply voltage and the threshold voltages, scale by a same ratio U. The relations governing the scaling behaviour of the dependent variables are tabulated in column. Observe that this analysis only considers shortchannel devices with a linear dependence between control voltage and saturation current.

| Parameter                       | Relation               | Full Scaling     | General Scaling  | Fixed-Voltage Scaling |

|---------------------------------|------------------------|------------------|------------------|-----------------------|

| W, L, t <sub>ox</sub>           |                        | 1/S              | 1/S              | 1/S                   |

| $V_{DD}$ , $V_T$                |                        | 1/S              | 1/U              | 1                     |

| N <sub>SUB</sub>                | $V/W_{depl}^2$         | S                | $S^2/U$          | S <sup>2</sup>        |

| Area/Device                     | WL                     | 1/S <sup>2</sup> | 1/S <sup>2</sup> | 1/S <sup>2</sup>      |

| Cax                             | $1/t_{ox}$             | S                | S                | S                     |

| Cgate                           | $C_{ox}WL$             | 1/S              | 1/S              | 1/S                   |

| k <sub>n</sub> , k <sub>p</sub> | $C_{ox}W/L$            | S                | S                | S                     |

| I <sub>sat</sub>                | $C_{ox}WV$             | 1/S              | 1/U              | 1                     |

| Current Density                 | I <sub>sat</sub> /Area | S                | $S^2/U$          | S <sup>2</sup>        |

| Ron                             | V/I <sub>sat</sub>     | 1                | 1                | 1                     |

| Intrinsic Delay                 | RonCgate               | 1/S              | 1/S              | 1/S                   |

| Р                               | $I_{sat}V$             | 1/S <sup>2</sup> | $1/U^{2}$        | 1                     |

| Power Density                   | P/Area                 | 1                | $S^{2}/U^{2}$    | S <sup>2</sup>        |

# **Full Scaling (Constant Electrical Field Scaling)**

In this ideal model, voltages and dimensions are scaled by the same factor S. The goal is to keep the electrical field patterns in the scaled device identical to those in the original device. Keeping the electrical fields constant ensures the physical integrity of the device and avoids breakdown or other secondary effects. This scaling leads to greater device density (Area), higher performance (Intrinsic Delay), and reduced power consumption (P).

The effects of full scaling on the device and circuit parameters are summarized in the third column of Table . We use the intrinsic time constant, which is the product of the gate capacitance and the on-resistance, as a measure for the performance. The analysis shows that the on-resistance remains constant due to the simultaneous scaling of voltage swing and current level. The performance improved is solely due to the reduced capacitance. The results clearly demonstrate the beneficial effects of scaling- the speed of the circuit

increases in a linear fashion, while the power/gate scales down quadratically.

#### **Fixed-Voltage Scaling**

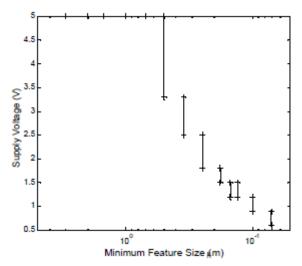

In reality, full scaling is not a feasible option. First of all, to keep new devices compatible with existing components, voltages cannot be scaled arbitrarily. Having to provide for multiple supply voltages adds considerably to the cost of a system. As a result, voltages have not been scaled down along with feature sizes, and designers adhere to well-defined standards for supply voltages and signal levels. As is illustrated in Figure 3.40, 5 V was the de facto standard for all digital components up to the early 1990s, and a *fixed-voltage scaling model* was followed.

Only with the introduction of the 0.5 mm CMOS technology did new standards such as 3.3 V and 2.5 V make an inroad. Today, a closer tracking between voltage and device dimension can be observed. The reason for this change in operation model can partially be explained with the aid of the fixed-voltage scaling model, summarized in the fifth column of Table. In a velocity-saturated device, keeping the voltage constant while scaling the device dimensions does not give a performance advantage over the full-scaling model, but instead comes with a major power penalty. The gain of an increased current is simply offset by the higher voltage level, and only hurts the power dissipation. This scenario is very different from the situation that existed when transistors were operating in the long-channel mode, and the current was a quadratic function of the voltage. Keeping the voltage constant under these circumstances gives a distinct performance advantage, as it causes a net reduction in on-resistance.

#### **General Scaling**

We observe in Figure that the supply voltages, while moving downwards, are not scaling as fast as the technology. For instance, for the technology scaling from 0.5m m to 0.1 mm, the maximum supply-voltage only reduces from 5 V to 1.5 V. The obvious question is why not to stick to the full-scaling model, when keeping the voltage higher does not yield any convincing benefits? This departure is motivated by the following argumentation:

• Some of the intrinsic device voltages such as the silicon band-gap and the built-in junction potential, are material parameters and cannot be scaled.

• The scaling potential of the transistor threshold voltage is limited. Making the threshold too low makes it difficult to turn off the device completely. This is aggravated by the large process variation of the value of the threshold, even on the same wafer.

Therefore, a more general scaling model is needed, where dimensions and voltages are scaled independently. This general scaling model is shown in the fourth column of Table. Here, device dimensions are scaled by a factor S, while voltages are reduced by a factor U. When the voltage is held constant, U = 1, and the scaling model reduces to the fixed-voltage model. Note that the general-scaling model offers a performance scenario

identical to the full- and the fixed scaling, while its power dissipation lies between the two models (for S > U > 1).

In VLSI design, as processes become more and more complex, need for the designer to understand the intricacies of the fabrication process and interpret the relations between the different photo masks is really troublesome.

Therefore, a set of layout rules, also called design rules, has been defined.

They act as an interface or communication link between the circuit designer and the process engineer during the manufacturing phase.

The objective associated with layout rules is to obtain a circuit with optimum yield (functional circuits versus non-functional circuits) in as small as area possible without compromising reliability of the circuit.

In addition, Design rules can be conservative or aggressive, depending on whether yield or performance is desired. Generally, they are a compromise between the two. Manufacturing processes have their inherent limitations in accuracy.

So the need of design rules arises due to manufacturing problems like -

- Photo resist shrinkage, tearing.

- Variations in material deposition, temperature and oxide thickness.

- Impurities.

- Variations across a wafer.

These lead to various problems like :

# • Transistor problems:

Variations in threshold voltage: This may occur due to variations in oxide thickness, ionimplantation and poly layer. Changes in source/drain diffusion overlap. Variations in substrate.

#### • Wiring problems:

Diffusion: There is variation in doping which results in variations in resistance, capacitance.

Poly, metal: Variations in height, width resulting in variations in resistance, capacitance. Shorts and opens.

# • Oxide problems:

Variations in height.

Lack of planarity.

# • Via problems:

Via may not be cut all the way through.

Undersize via has too much resistance.

Via may be too large and create short.

To reduce these problems, the design rules specify to the designer certain geometric constraints on the layout artwork so that the patterns on the processed wafers will preserve the topology and geometry of the designs. This consists of minimum-width and minimum-spacing constraints and requirements between objects on the same or different layers. Apart from following a definite set of rules, design rules also come by experience.

# Types of Design Rules

The design rules primary address two issues:

1. The geometrical reproduction of features that can be reproduced by the maskmaking and lithographical process, and

2. The interaction between different layers.

There are primarily two approaches in describing the design rules.

1. Linear scaling is possible only over a limited range of dimensions.

2. Scalable design rules are conservative .This results in over dimensioned and less dense design.

3. This rule is not used in real life.

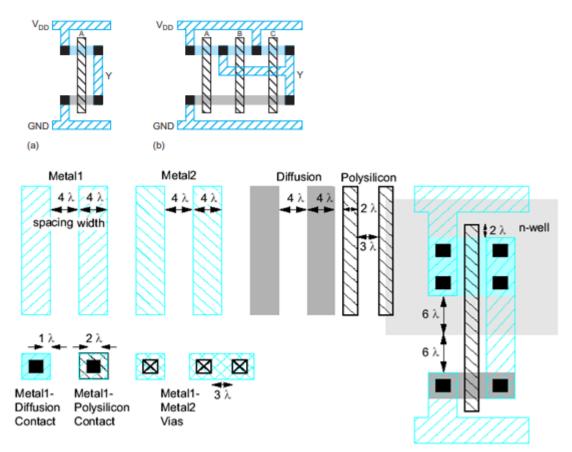

1. Scalable Design Rules (e.g. SCMOS,  $\lambda$ -based design rules): In this approach, all rules are defined in terms of a single parameter  $\lambda$ . The rules are so chosen that a design can be easily ported over a cross section of industrial process ,making the layout portable .Scaling can be easily done by simply changing the value of  $\lambda$ .

2. Absolute Design Rules (e.g.  $\mu$ -based design rules ) : In this approach, the design rules are expressed in absolute dimensions (e.g. 0.75 $\mu$ m) and therefore can exploit the features of a given process to a maximum degree. Here, scaling and porting is more demanding, and has to be performed either manually or using CAD tools .Also, these rules tend to be more complex especially for deep submicron. The fundamental unity in the definition of a set of design rules is the minimum line width .It stands for the minimum mask dimension that can be safely transferred to the semiconductor material .Even for the same minimum dimension, design rules tend to differ from company to company, and from process to process. Now, CAD tools allow designs to migrate between compatible processes.

# Layer Representations

With increase of complexity in the CMOS processes, the visualization of all the mask levels that are used in the actual fabrication process becomes inhibited. The layer concept translates these masks to a set of conceptual layout levels that are easier to visualize by the circuit designer. From the designer's viewpoint, all CMOS designs have the following entities:

• Two different substrates and/or wells: which are p-type for NMOS and n-type for PMOS.

• Diffusion regions (p+ and n+): which defines the area where transistors can be formed. These regions are also called active areas. Diffusion of an inverse type is needed to implement contacts to the well or to substrate. These are called select regions. • Transistor gate electrodes: Polysilicon layer

• Metal interconnect layers

• Interlayer contacts and via layers. The layers for typical CMOS processes are represented in various figures in terms of:

- A color scheme (Mead-Conway colors).

- Other color schemes designed to differentiate CMOS structures.

- Varying stipple patterns

• Varying line styles

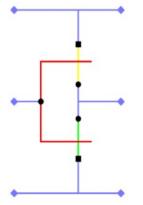

# **Stick Diagrams**

Another popular method of symbolic design is "Sticks" layout. In this, the designer draws a freehand sketch of a layout, using colored lines to represent the various process layers such as diffusion, metal and polysilicon .Where polysilicon crosses diffusion, transistors are created and where metal wires join diffusion or polysilicon, contacts are formed.

This notation indicates only the relative positioning of the various design components. The absolute coordinates of these elements are determined automatically by the editor using a compactor. The compactor translates the design rules into a set of constraints on the component positions, and solves a constrained optimization problem that attempts to minimize the area or cost function.

The advantage of this symbolic approach is that the designer does not have to worry about design rules, because the compactor ensures that the final layout is physically correct. The disadvantage of the symbolic approach is that the outcome of the compaction phase is often unpredictable. The resulting layout can be less dense than what is obtained with the manual approach. In addition, it does not show exact placement, transistor sizes, wire lengths, wire widths, tub boundaries.

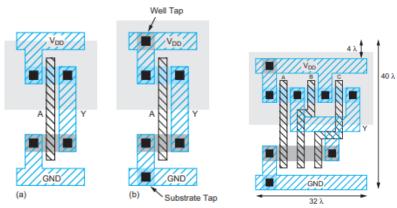

# **Gate Layouts**

A good deal of ingenuity can be exercised and a vast amount of time wasted exploring layout topologies to minimize the size of a gate or other cell such as an adder or memory element. For many applications, a straightforward layout is good enough and can be automatically generated or rapidly built by hand. This section presents a simple layout style based on a "line of diffusion" rule that is commonly used for standard cells in automated layout systems. This style consists of four horizontal strips: metal ground at the bottom of the cell, n-diffusion, p-diffusion, and metal power at the top. The power and ground lines are often called supply rails. Polysilicon lines run vertically to form transistor gates. Metal wires within the cell connect the transistors appropriately.

Figure (a) shows such a layout for an inverter. The input A can be connected from the top, bottom, or left in polysilicon. The output Y is available at the right side of the cell in metal. Figure shows the same inverter with well and substrate taps placed under the power and ground rails, respectively

# PART A

- Define threshold voltage of MOSFET A/M 19

The Threshold voltage, V for a MOS transistor can be defined as the voltage applied

T between the gate and the source of the MOS transistor below which the drain to

source current, I<sub>DS</sub> effectively drops to zero.

- 2. By what factor gate capacitance must be scaled if constant electric field scaling is employed? A/M 19

gate capacitance must be scaled by a factor 1/S

- 3. Why NMOS device conducts strong zero and weak one? N/D 18 For an NMOS to pass VDD(logic 1) from input node to output node gate should be logic 1 . And the node out gets gradually charged from 0 towards VDD . When out reaches VDD-Vtn then (Vgate- Vout) = VDD-(VDD-Vtn) = Vtn which is the minimum voltage required for the NMOS to be ON state for a current to flow. So node out reaching to a potential more than VDD-Vtn turns off the NMOS. So the maximum voltage level that the output node can be charged to is VDD-Vtn.

- 4. Draw the stick diagram of static CMOS 2 input NAND gate N/D 18

# 5. What is meant by velocity saturation? A/M 18

The saturation current increases less than quadratically with increasing Vgs .Tis is caused by two effects velocity saturation and mobility degradation.At high electric fields strengths Vds/L carrier velocity ceases to increase linearly with field strength.this is called velocity saturation and results in lower Ids ,than expected at high Vds.

| Parameter                       | Relation                          | Full Scaling     | General Scaling  | Fixed-Voltage Scaling |

|---------------------------------|-----------------------------------|------------------|------------------|-----------------------|

| W, L, t <sub>ox</sub>           |                                   | 1/S              | 1/ <i>S</i>      | 1/5                   |

| $V_{DD}$ , $V_T$                |                                   | 1/S              | 1/U              | 1                     |

| N <sub>SUB</sub>                | $V/W_{depl}^2$                    | S                | $S^2/U$          | S <sup>2</sup>        |

| Area/Device                     | WL                                | 1/S <sup>2</sup> | 1/S <sup>2</sup> | 1/S <sup>2</sup>      |

| Cox                             | $1/t_{ox}$                        | S                | S                | S                     |

| Cgate                           | $C_{ox}WL$                        | 1/S              | 1/S              | 1/S                   |

| k <sub>n</sub> , k <sub>p</sub> | CoxW/L                            | S                | S                | S                     |

| Isat                            | $C_{ox}WV$                        | 1/S              | 1/U              | 1                     |

| Current Density                 | I <sub>sat</sub> /Area            | S                | $S^2/U$          | S <sup>2</sup>        |

| Ron                             | V/I <sub>sat</sub>                | 1                | 1                | 1                     |

| Intrinsic Delay                 | R <sub>on</sub> C <sub>gate</sub> | 1/S              | 1/S              | 1/S                   |

| Р                               | $I_{sat}V$                        | 1/S <sup>2</sup> | $1/U^{2}$        | 1                     |

| Power Density                   | P/Area                            | 1                | $S^{2}/U^{2}$    | $S^2$                 |

| 6. | List th | ne scaling | properties? | A/M 18 |

|----|---------|------------|-------------|--------|

|----|---------|------------|-------------|--------|

# 7. Why Nmos transistor is selected as pull down transistor? N/D 17

The nmos I selected for pull down transistor because it passes strong 1's. which the used to turn off the transistor.

# 8. What is the need of demarcation line? N/D 17

In CMOS a demarcation line is drawn to avoid touching of p-diff with n-diff . all pmos must lie on one side of the line and all nmos will have o on other side.

9. What is meant channel length modulation in NMOS transistors? A/M 17 In cut off, the gate-to-source voltage is not greater than the threshold voltage, and the MOSFET is inactive .thus, channel-length modulation means that the saturation region drain current will increase slightly as the drain to source voltage is increases.

# 10. Define propagation delay of a CMOS inverter? A/M 17

Propagation delays Tplh and tphl are defined as the times required for output voltage to reach the middle between the low and high logic levels.

# 11. Define body bias effect? N/D 16

Body effect refers to the change in the threshold voltage of the device when there is a difference between substrate(body) and source voltages. Body bias is usually the lowest voltage in the chip(in case of of p-substrate). The substrate bias effect and source drain breakdown characteristics in body tied short channel silicon on insulator metal oxide semiconductor field effect transistor.

# 12. Draw stick and layout diagram for cmos inverter? N/D 16

# 13. State channel length modulation. Write down the equation for describing the channel length modulation effect in NMOS transistor. A/M 16

The effective length of the conductive channel is actually modulated by the applied  $V_{DS}$ : increasing  $V_{DS}$  causes the depletion region at the drain junction to grow, reducing the length of the effective channel. As can be observed from Eq. For I<sub>D</sub> in the saturation region, the current increases when the length factor *L* is decreased. A more accurate description of the current of the MOS transistor is therefore given in Eq.

$$I_D = I_D'(1 + \lambda V_{DS})$$

with  $I_D$ ' the current expressions derived earlier, and 1 an empirical parameter, called the *channel-length modulation*.

#### 14. What is latch-up? How to prevent latch-up? A/M 16

Consider the *n*-well structure of Figure a. The *n-p-n-p* structure is formed by the source of the NMOS, the *p*-substrate, the *n*-well and the source of the PMOS. A circuit equivalent is shown in Figure b. When one of the two bipolar transistors gets forward biased (e.g., due to current flowing through the well, or substrate), it feeds the base of the other transistor. This positive feedback increases the current until the circuit fails or burns out.

#### PART B

- Derive an expression for Ids of nMOS in linear and saturated region? A/M 19 (OR) Describe the equation for source to drain current in the three region of operation of MOS transistor and draw the VI characteristics. A/M 16

- Draw a CMOS inverter. Analyse the switching characteristics during the rise time when Vin changes from high to low? A/M 19 & derive the noise margin for CMOS inverter? N/D 16

- 3. Draw the stick diagram of CMOS inverter? A/M 19(OR) Write the layout design rules and draw the stick diagram and layout diagram for 4 input NAND gate and 4 input NOR. A/M 18 (OR) Write the layout rules and draw diagram for four input NAND and NOR gate? N/D 17 (OR) Draw the layout diagram for NAND and NOR gate? A/M 17 (OR) State the minimum width and minimum spacing lambda based design rules to draw the layout A/M 19

- 4. Explain the dynamic behaviour of MOS transistors with neat diagram A/M 18

- (a)(i) Explain the electrical properties of CMOS? N/D 17

(a) (ii) Discuss on scaling and its limits? N/D 17 (OR) Explain the need of scaling , scaling principles and fundamentals units of CMOS inverter? A/M 17

- 6. Draw and explain the dc and transfer characteristics of CMOS inverter with necessary condition for the different regions of operation? A/M 17 (OR) Explain the DC transfer characteristics of a CMOS inverter with necessary conditions for the different regions of operation. A/M 16

- 7. Explain the different steps involved in n-well Cmos fabrication process? N/D 16

- 8. Explain in detail about the body effect and its effect in MOS device A/M 16

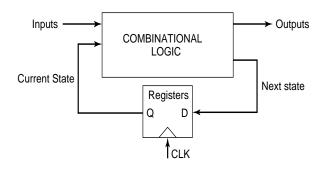

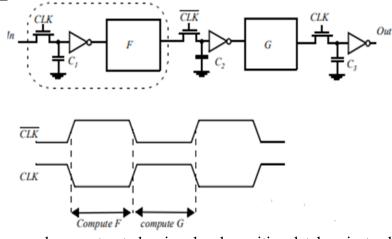

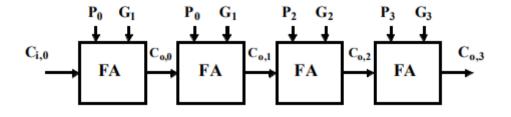

#### Unit II **Combinational Logic Circuits**

#### Introduction

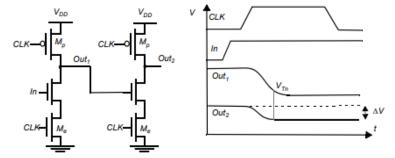

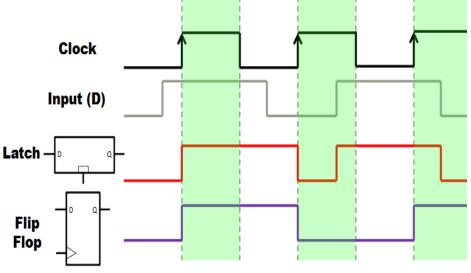

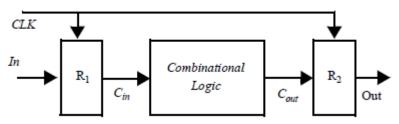

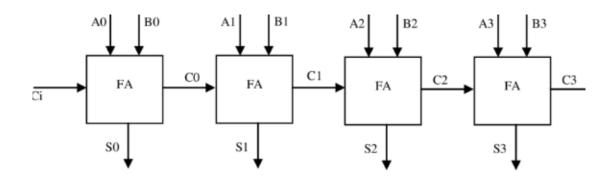

In combinational circuits, the output is a function of current inputs. Eg: adder, subtractor, MUX and DEMUX. In general, the delay of a logic gate depends on its output current I, load capacitance C and output voltage  $\Delta V$ . The time delay is directly proportional to C / I.

If any one of these numerator parameters is reduced or I increases then time delay t decreases.

Generally the nMOS transistor provides more current than pMOS for the same size and capacitance so nMOS network are preferred. The logical effort g is directly proportional to C/I. If g decreases speed will be increasing.

There are number of logic families to implement a given logic function. It can be choosing/ evaluation in terms of area, speed energy and power. The different logic families are

• Static CMOS design.

• Dynamic CMOS design.

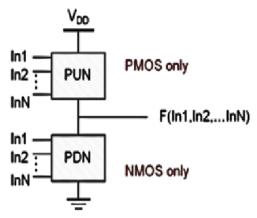

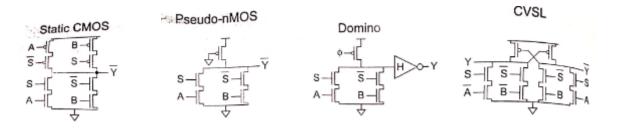

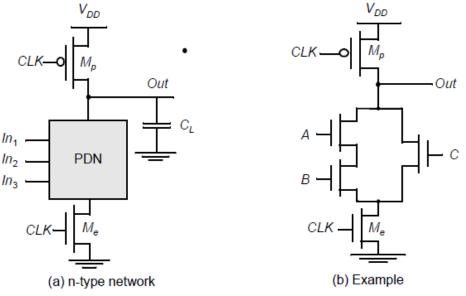

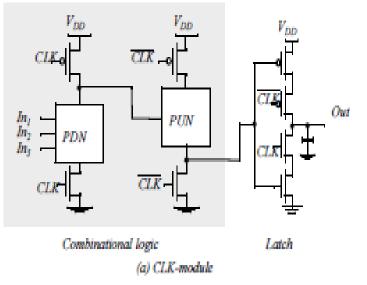

#### I. Static CMOS design

At each and every points in time the gate output is either connected to Vdd or Vss through a low resistance path.

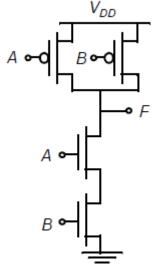

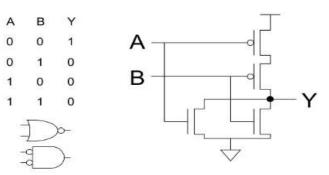

#### 1) Complementary CMOS

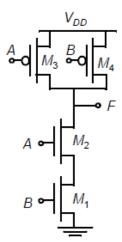

It is a combination of pMOS [pull up network] and nMOS [pull down network]. Diagram

nMOS produces "strong zero" and pMOS produces " strong one"

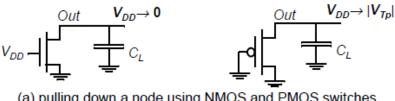

(a) pulling down a node using NMOS and PMOS switches

(b) pulling down a node using NMOS and PMOS switches

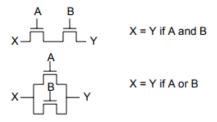

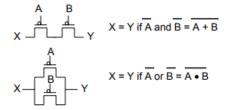

If nMOS devices are connected in series then the function is "AND". If the nMOS devices are connected in parallel that represents an OR

For pMOS series means OR and AND means parallel. The parallel connection of transistor in Pun corresponds to a series connection in PDN. Hence they are called dual networks.

The CMOS is naturally inverting so realization of AND Or and Xor require extra inverter stage. The number of transistors required is 2N.

| Α | В | F |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

CMOS NOR Gate

#### Advantages

Good noise margin. Fast. Low power. Rendily available in standard cell libraries. Insensitive to device variation. Easy to design. Widely supported by CAD tools.

# Disadvantages

For each input it requires both nMOS and pMOS.

It has relatively large logical effort i.e during falling output transition the pMOS transistors add significant capacitance. Eventhough it is not responsible for falling output transistion (1 to 0

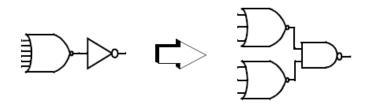

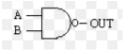

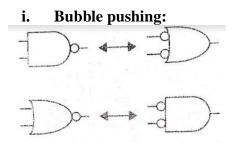

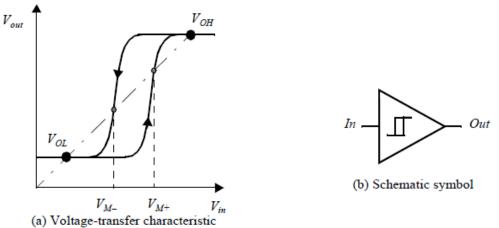

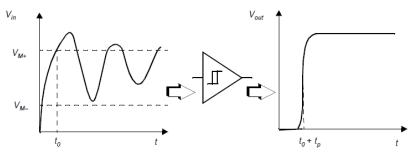

Bubble pushing is a technique to apply De Morgan's theorem directly to the logic diagram. To change the logic gate (AND to OR and OR to AND), Add **bubbles** to the inputs and outputs where there were none, and remove the original **bubbles**.

#### ii. Compound Gates:

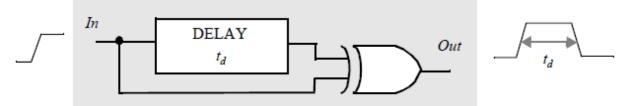

#### iii. Input Ordering Delay Effect:

- If input arrival time is known, Connect latest input to inner terminal

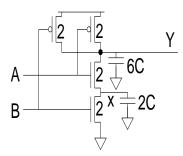

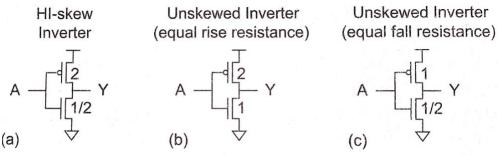

#### iv. Skewed Gates:

- Skewed gates favor one transition over another

- Ex: suppose rising output of inverter is most critical

- Downsize noncritical nMOS transistor

- Calculate logical effort by comparing to unskewed inverter with same effective resistance on that edge.

- $\begin{array}{rl} & g_u = 2.5 \ / \ 3 = 5/6 \\ g_d = 2.5 \ / \ 1.5 = 5/3 \end{array}$

(b)

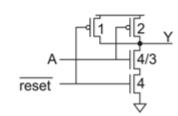

# Eg: Resettable Buffer optimized for data input

- Asymmetric gates favor one input over another

- Ex: suppose input A of a NAND gate is most critical

- Use smaller transistor on A (less capacitance)

- Boost size of noncritical input

- So total resistance is same

- $g_A = 10/9: g_B = 2$

- $g_{avg} = (g_A + g_B)/2 = 14/9$

- Asymmetric gate approaches g = 1 on critical input

- But total logical effort goes up

#### 2) . Ratioed circuits:

Ratioed circuit use weak pull up device and strong pull down device.

The transfer function depends on the ratio between the strength of PUN and PDN.

#### Advantages:

It reduces the input capacitance so that the logical effort is improved (by eliminating large pMOS transistors which load the supply).

Reduced area.

### **Disadvantages:**

Continuously dissipates power when input=1. poor noise margin than CMOS.

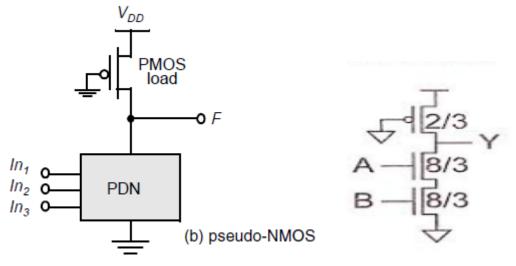

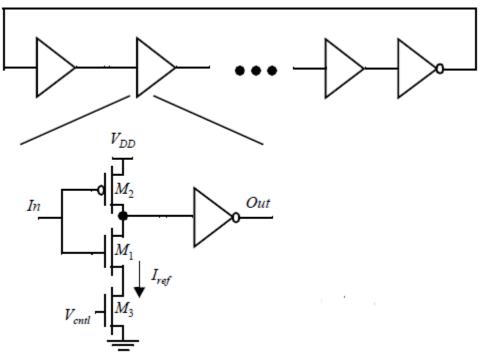

#### i)Pseudo nMOS:

The most common form of CMOS ratioed logic.

The PDN of ratioed circuit is similar to PDN of static CMOS. But the pull up network is replaced by a single pMOS transistor where input is grounded, so is always on

If the PUN is strong , it produces the high  $V_{OL}$  (noise margin -good).

If the pull up network is weak it produces high rising delay(speed ).

pMOS transistor width is optimised.

So the width of the transistor is selected by taking 1/4 strength( or 1/2 effective width of the nMOS transistor).

EX: Invertor using pseudo nMOS:

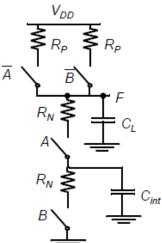

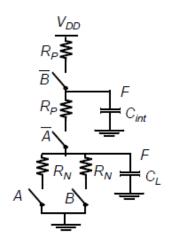

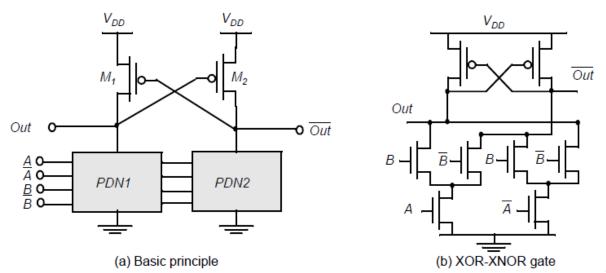

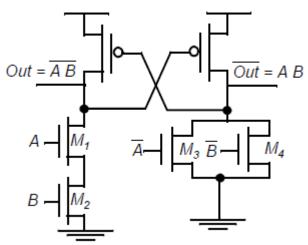

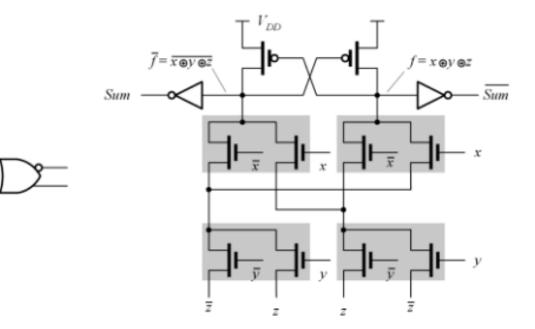

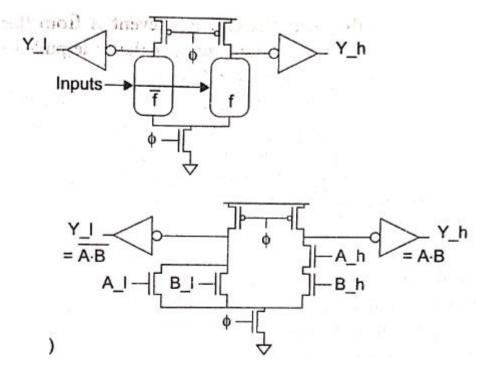

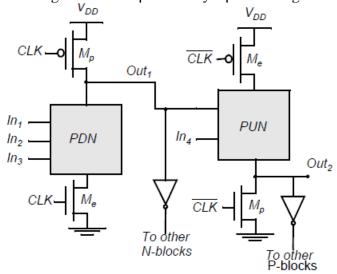

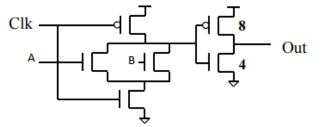

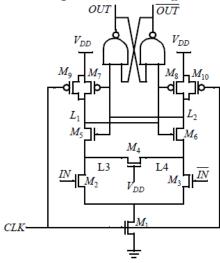

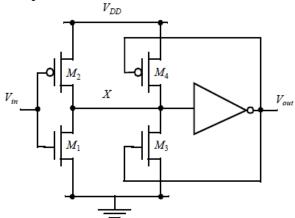

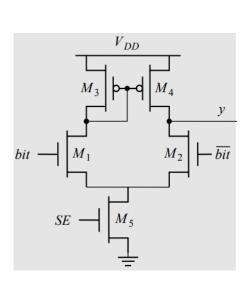

# ii) Cascode Voltage Switch Logic(CVSL):

- The static power dissipation problem in the ratioed circuits can be improved by using CVSL.

- It uses both true and complementary input signals and computes both true and complementary output using a pair n-MOS PDN.

- The PDN f implements the logic function similar to static CMOS gates.

- The PDN f' uses inverted inputs. The networks f and f' are complementary with parallel transistors in one network and series in another network.

- •

- When A=B=1, both n-MOS are **ON** which pulls the output **y=0**. This turns on the p-MOS transistor (p1) which produces the **y'=1**.

- When A=0 B=1, n3 turns ON so it produces the output y'=0 which turns on the p2 which produces y=1.

- When A=B=0, both n3 and n4 turn ON, this will pull the output y'=0 which will turn on the p2 transistor so the y=1.

- For any given input one of the PDN will be ON and the other will be OFF, so there is no static power dissipation.

- The advantage of CVSL is speed, because all of the logic is performed with n-MOS transistor then reducing input capacitance.

- The disadvantage of CVSL is it requires both the low and high going transitions, which increases the delay. CVSL is not suited to NAND and NOR logic.

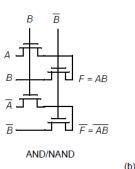

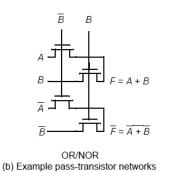

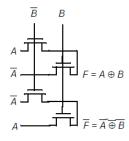

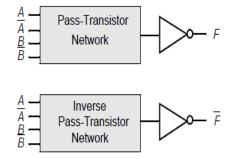

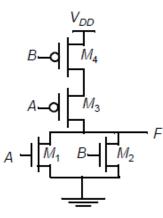

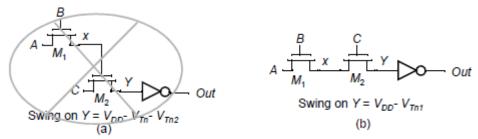

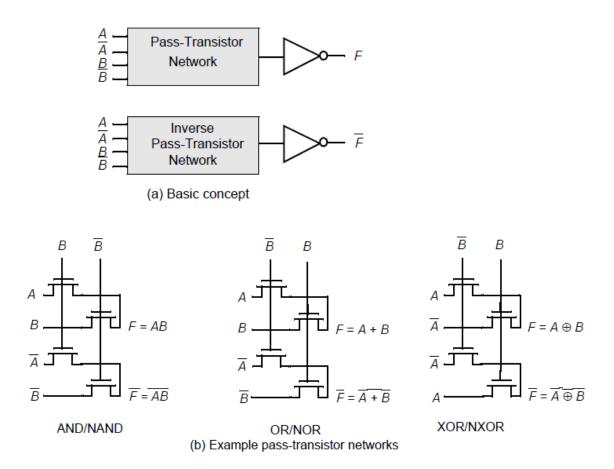

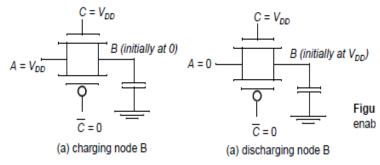

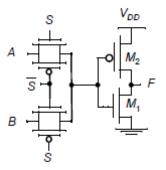

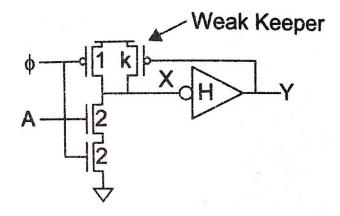

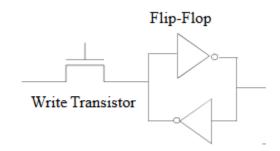

# 3) . Pass Transistor Logic

A popular and widely-used alternative to complementary CMOS is pass-transistor logic, which attempts to reduce the number of transistors required to implement logic by allowing the primary inputs to drive gate terminals as well as source/drain terminals. This is in contrast to logic families that we have studied so far, which only allow primary inputs to drive the gate terminals of MOSFETS.

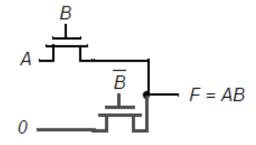

Figure shows an implementation of the AND function constructed that way, using only NMOS transistors. In this gate, if the *B* input is high, the top transistor is turned on and copies the input *A* to the output *F*. When *B* is low, the bottom pass transistor is turned on and passes a 0. The switch driven by *B* seems to be redundant at first glance. Its presence is essential to ensure that the gate is static, this is that a low-impedance path exists to the supply rails under all circumstances, or, in this particular case, when *B* is low.

The promise of this approach is that fewer transistors are required to implement a given function. For example, the implementation of the AND gate in Figure requires 4 transistors (including the inverter required to invert B), while a complementary CMOS implementation would require 6 transistors. The reduced number of devices has the additional advantage of lower capacitance.

- > nMOS pass strong 0 But degraded or weak 1

- ➢ pMOS pass strong 1 − But degraded or weak 0

$$A \xrightarrow{B} F = AB$$

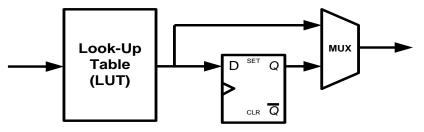

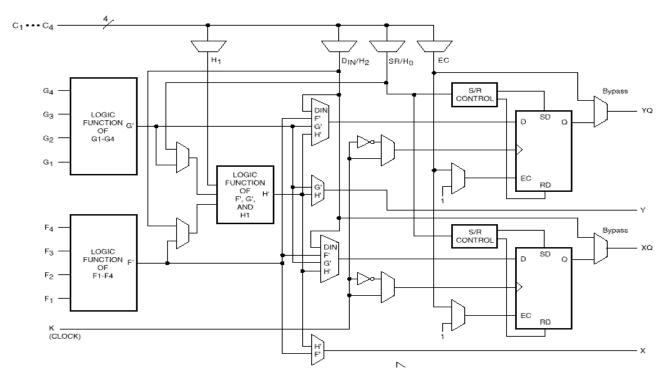

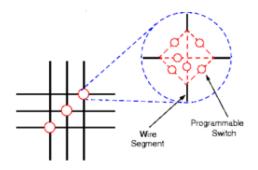

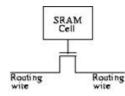

An NMOS device is effective at passing a 0 but is poor at pulling a node to *VDD*. When the pass transistor pulls a node high, the output only charges up to *VDD* -*VTn*. In fact, the situation is worsened by the fact that the devices